更新后的 FPGA 夹层卡规范提供无与伦比的高 I/O 密度、向后兼容性。

作为使用 FPGA 和高速 I/O 的嵌入式计算设计的重要发展,名为 FMC+ 的最新夹层卡标准将把卡中的千兆位收发器(GT)的总数量从 10 个扩展到 32 个,最大数据速率从 10Gbps 提升到 28Gbps,同时保持与当前 FMC 标准实现向后兼容。

这些功能与使用 JESD204B 串行接口标准的新器件以及 10G 和 40G 光学器件及高速串行存储器也非常吻合。FMC+ 可满足最具挑战性的 I/O 要求,为开发人员提供了双重优势:夹层卡的灵活性,以及单芯片设计的高 I/O 密度。

FMC+ 规范是在去年制定和细化的。VITA 57.4 工作组已经批准该规范并将在 2016 年初提交 ANSI 投票。下面详细介绍一下这一重要的新标准,了解其对高级嵌入式设计的影响。

夹层卡的优势

夹层卡是一种为嵌入式系统添加特定功能的有效且广泛使用的方法。因为夹层卡是连接在基础卡或载卡上,而不是直接插在背板上,夹层卡可以轻松更换。对系统设计人员来说,这意味着既能够灵活配置,又可以轻松升级。但由于连接问题或安装到开发板上需占用额外的空间,这种灵活性往往会以牺牲功能为代价。

对于 FPGA,主要的开放标准是 ANSI/VITA 57.1,也称之为 FPGA 夹层卡 (FMC) 规范。最新标准 FMC+(更正式的说法,即 VITA 57.4)通过大幅增强千兆位串行接口的功能,扩展了现有 FMC 标准的功能。

与单芯片解决方案相比,FMC+ 能解决基于夹层卡的 I/O 的许多不足,同时提供更高的灵活性和性能。同时 FMC+ 标准具有后向兼容,符合 FMC 的发展历史并满足其用户群体需求。

该 FMC 标准定义的是一种小型夹层卡,其高度和宽度类似于久成熟的 XMC 或 PMC,但长度只有其一半。这意味着 FMC 与开放标准格式相比,组件板级空间更小。但 FMC 不需要往往占用大量板级空间的总线接口,例如 PCI-X。作为替代,FMC 使用供电要求较为简单的直连 I/O 与主控 FPGA 通信。这意味着虽然尺寸更小,但 FMC 实际上有比它们的 XMC 同等产品更大的 I/O 容量和 PMC 和 XMC 规范一样,FMC 和 FMC+ 也同时提供空气冷却和传导冷却两种选择,因此商业和军用市场各自需求的普通和耐用型应用都能适用。

FMC 规范解析起来相当简单。该标准为高引脚数(HPC)设计可提供多达 160 个单端或 80 个差分并联 I/O 信号,为低引脚数 (LPC) 设计提供一半数量的 I/O 信号。可以设置多达 10 个全双工 GT 连接。这些 GT 适用于光纤或其他串行接口。此外,FMC 规范还定义了关键的时钟信号。所有这些 I/O 都是可选的,虽然大部分主机现在支持完全连接。

FMC 规范还定义了多种电源输入,虽然夹层卡定义的是由主机供电。这种方法的工作方式是先给夹层卡部分供电,这样主机就能够询问 FMC,然后 FMC 通过为 VADJ 定义电压范围来做出响应。如果主机能够提供该电压范围,则一切顺利进行。不在夹层卡上设主电源调整既能节省空间,又能降低夹层卡的功耗。

用于模拟 I/O 的 FMC

设计人员可将 FMC 用作任何用户想连接到 FPGA 的功能,例如数字 I/O、光纤、控制接口、存储器或附加处理。但模拟 I/O 仍然是 FMC 技术最常见的用途。FMC 规范适用于相当大范围的快速高精度 I/O,但也需要权衡使用,尤其是对使用并行接口的高速部件来说。

例如德州仪器的 ADC12D2000RF 双通道 2 Gsps 12 位 ADC 使用 1:4 复用总线接口,因此该总线速度对主控 FPGA 来说不算过快。数字数据接口单独需要 96 个信号(48 个 LVDS 对)。对这种级别的器件,FMC 只能支持一个此类器件,即便有足够的空间容纳更多器件,但 FMC 的上限是 160 个信号。较低精度器件就算是工作在较高速度下,例如那些工作在 8 位数据通道上的器件,即便换衡器、放大器、时钟等提出更高的前端模拟耦合要求,也可以允许更多通道数量。

对使用并行接口,运行速度在 5 Gsps 或 6 Gsps(吞吐量大于 50Gbps),精度大于 8 位的模拟接口,FMC 规范开始无法应对。站在市场的角度,从通道密度、速度和精度来看,主流 FMC 的吞吐量在 25-50 Gbps 之间。这样的性能水平是物理封装尺寸与到主控 FPGA 的可用连接权衡的结果。

除了并行连接,FMC 规范还支持多达 10 个双工高速串行(GT)链路。

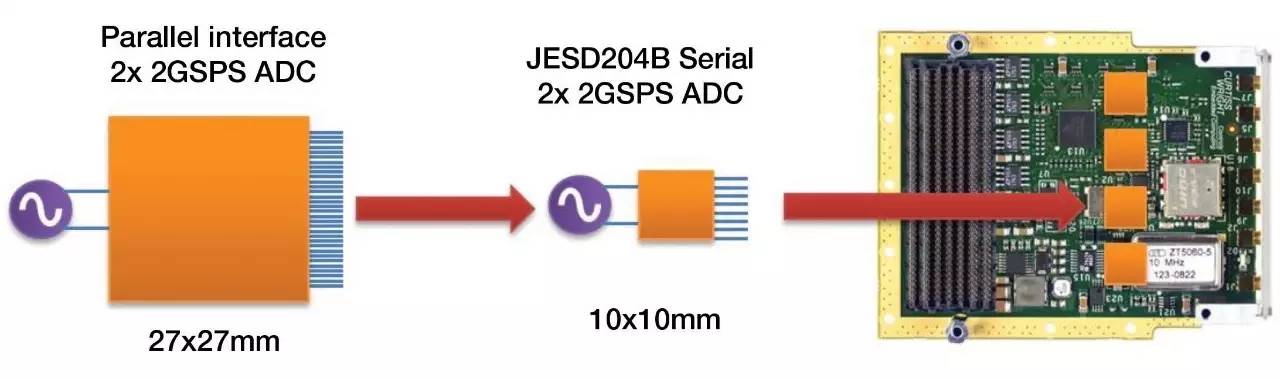

图 1 - FMC 借助 JESD204B 缩小封装带来的影响

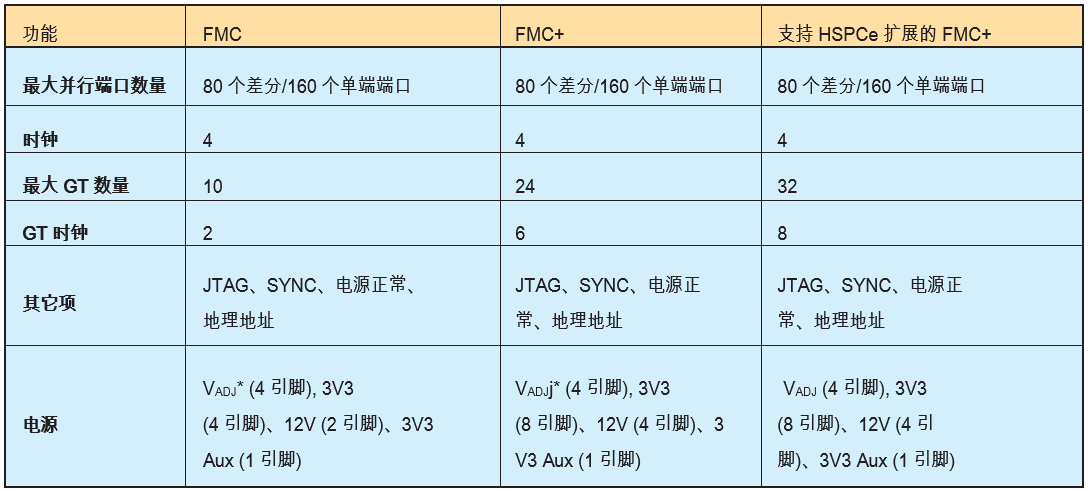

* VADJ:由夹层卡定义,由主机提供的电压电平

表 1 - FMC 和 FMC+ 连接一览表

这些接口对光纤 I/O、以太网、混合存储立方体 (HMC) 和 Bandwidth Engine 等新兴技术以及使用 JESD204B 接口的新一代模拟 I/O 器件有用。

JESD204B 到来

虽然 JESD204 串行接口标准(目前为修订版“B”)问世已有一段时间,直到最近它才被市场广泛采用,成为新一代高采样率数据转换器的串行接口标配。这种广泛采用背后的推动力来自电信行业对更小型化、更低功耗和更低成本器件的渴求。

如前文所述,采用并行接口的双通道 2 Gsps、12 位 ADC 需要大量的 I/O 信号。这一要求直接影响到封装尺寸。在本例中要求使用 292 引脚封装,尺寸大致为 27x27mm(虽然下一代引脚几何结构能让封装尺寸缩小到不足 20x20mm)。

而采用 JESD204B 连接的同等器件可以采用 68 引脚、10x10mm 封装,同时功耗更低。

这种封装尺寸的大幅缩减与不断演进的 FPGA 形成良好的搭配,因为 FPGA 正在提供数量不断增长、速度不断提升的 GT 链路。图 1 所示的是封装尺寸和 FMC/FMC+ 开发板尺寸的示例。

根据采样率要求的数据吞吐能量、精度和模拟 I/O 通道数量,典型的使用 JESD204B 接口的高速 ADC 和 DAC 有 1-8 个工作在 3-12Gbps 速率上的 GT 链路。

FMC 规范定义的是尺寸相对较小的夹层卡,但随着 JESD204B 器件的兴起,可用板级空间内能够容纳更多部件。FMC 规范定义的最多 10 个 GT 链路是一个可用的数量。就是这有限数量的 GT 链路只需使用并行 I/O 所需引脚数量的一部分,就能够提供 80 Gbps乃至更高的吞吐量。

使用 JESD204B 等接口的串行连接 I/O 器件的兴起,确实给电子战的部分细分应用带来了不足,例如数字化射频存储器 (DRFM)。因数据流水线较长,串行接口不可避免地会带来更大的时延。对 DRFM 应用来说,数据输入到数据输出之间的时延是一个根本性的性能参数。虽然各种串行连接器件之间的时延往往有很大不同,新一代器件会让数据以越来越快的速度穿过流水线,其中部分器件有望具备调节流水线深度的能力。究竟能实现多大的改进,仍有待观望。

今天部分采样率大于 1Gbps 的标准 ADC 器件的时延低于 100 ns。其他应用能够容忍这一时延,或忽略不计,包括软件定义射频 (SDR)、雷达告警接收器和其他信号情报 (SIGINT) 细分领域。在大众市场化电信基础设施的推动下,新一代 RF ADC 和 DAC 技术得到了广泛使用,这些应用也因此获得了显著优势。

在 FPGA 社区之外,新一代 DSP 器件也在开始采用 JESD204B。但是 FPGA 很有可能仍然能够占据最能充分发挥宽带模拟 I/O 器件功能的位置。这是因为 FPGA 能以更优异的并行性处理巨大的数据量。

FMC+ 的演进

为将 FMC 提升到全新的高度,VITA 57.4 工作组已经使用工作在更高速度上的更大数量 GT 链路制定出一个规范。FMC+ 只是给 FMC 连接器增加外层列来处理更多信号,没有更改任何电路板形状或机械结构,因此具备完整的 FMC 后向兼容性。

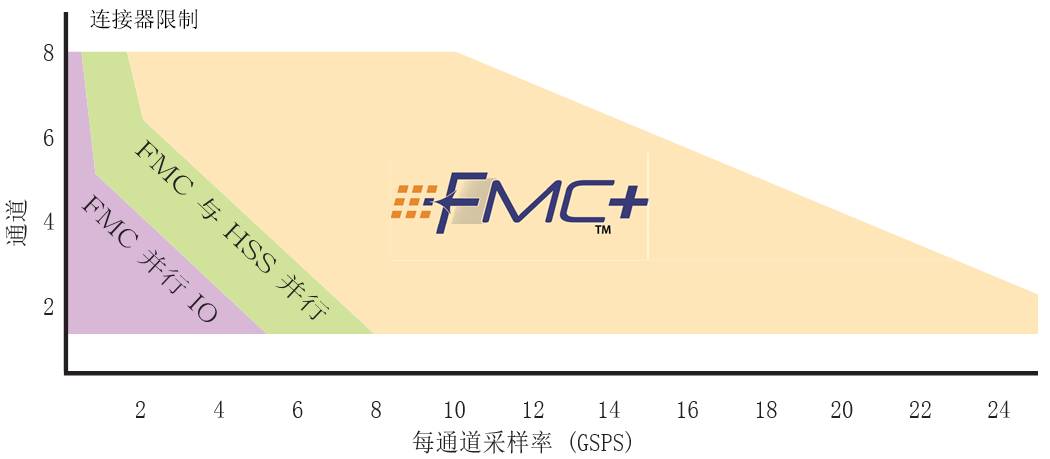

新增行可以构成增强型连接器的组成部分,从而最大限度地减少对可用板级空间的占用。FMC+ 规范把可用 GT 链路的最大数量从 10 个增加到 24 个,并可选择添加另外 8 个链路,从而实现合计 32 个全双工链路。额外的链路使用 HSPCe 单独连接器(HSPC 为主连接器)。表 1 是 FMC 和 FMC+ 连接的概览多个独立信号完整性团队对更高的 28Gbps 数据率进行了特性描述和验证。在包含并行接口的情况下,每个方向的最大双工吞吐量现在能够超过 900Gpbs。关于同时支持 FMC 和 FMC+ 的不同功能的数字化解决方案预期能达到的净吞吐量的略图,请参阅图 2。

图 2 - FMC 与 FMC+ 数字化器的吞吐能量对比

设计人员可以利用 FMC+ 实现的更大吞吐量充分发挥提供巨大 I/O 带宽的新器件的优势。这里仍然需要有权衡,例如有多少器件能安装到该夹层卡的可用空间中,但对适度数量的通道而言,与今天的 FMC 规范相比,可实现的吞吐量已经是巨大的飞跃。

新一代 ADC 和 DAC

在今后几年里可以合理预计高精度 ADC 和 DAC 将突破 10 Gsps 壁垒,使用直接 RF 采样支持 L-、S- 乃至 C 波段频率的极宽宽带通信。在 10Gbps 以下,12 位、14 位乃至 16 位精度的转换器正在兴起,部分支持多个通道。这些器件的大部分将使用配备 12 Gbps 通道的 JESD204B(或更新版本)的信号处理,直至更新一代产品让这一速度迈上新的高度。这些快速发展背后的动力来自电信行业,但国防工业也能加以利用,以满足尺寸、重量以及成本 (SWAP-C) 要求。

其他 FMC+ 的优势与用途

虽然和 FMC 类似,FMC+ 也很可能被 ADC、DAC 和收发器产品左右,FPGA 提供的更大 GT 密度让它能用于其他功能。两个值得一提的功能是光纤和新型串行存储器。

和 JESD204B 一样,存在对更快、更密集光纤的需求。使用光纤排带的器件能让部件的尺寸最小。因为 FMC+ 的空间能立即支持 24 路全双工光纤链路,有 FMC+ 支持的较高速度,该应用很有可能率先实现。每路光纤 28Gbps 的带宽将让吞吐量迅速地迈过单芯片夹层卡 100G 和 400G 大关。今天在现行 FMC 格式上的 100G 光传输能力正在兴起。

另一个适用于 FMC+ 的新兴领域是混合存储立方体 (HMC) 和 MoSys 的 Bandwidth Engine 等串行存储器。这些新颖的器件属于全新一类高性能存储器,

借助 GT 连接功能可提供前所未有的系统性能和带宽。(赛灵思中国通讯第 43 期 ,查看这些新存储器类型。)

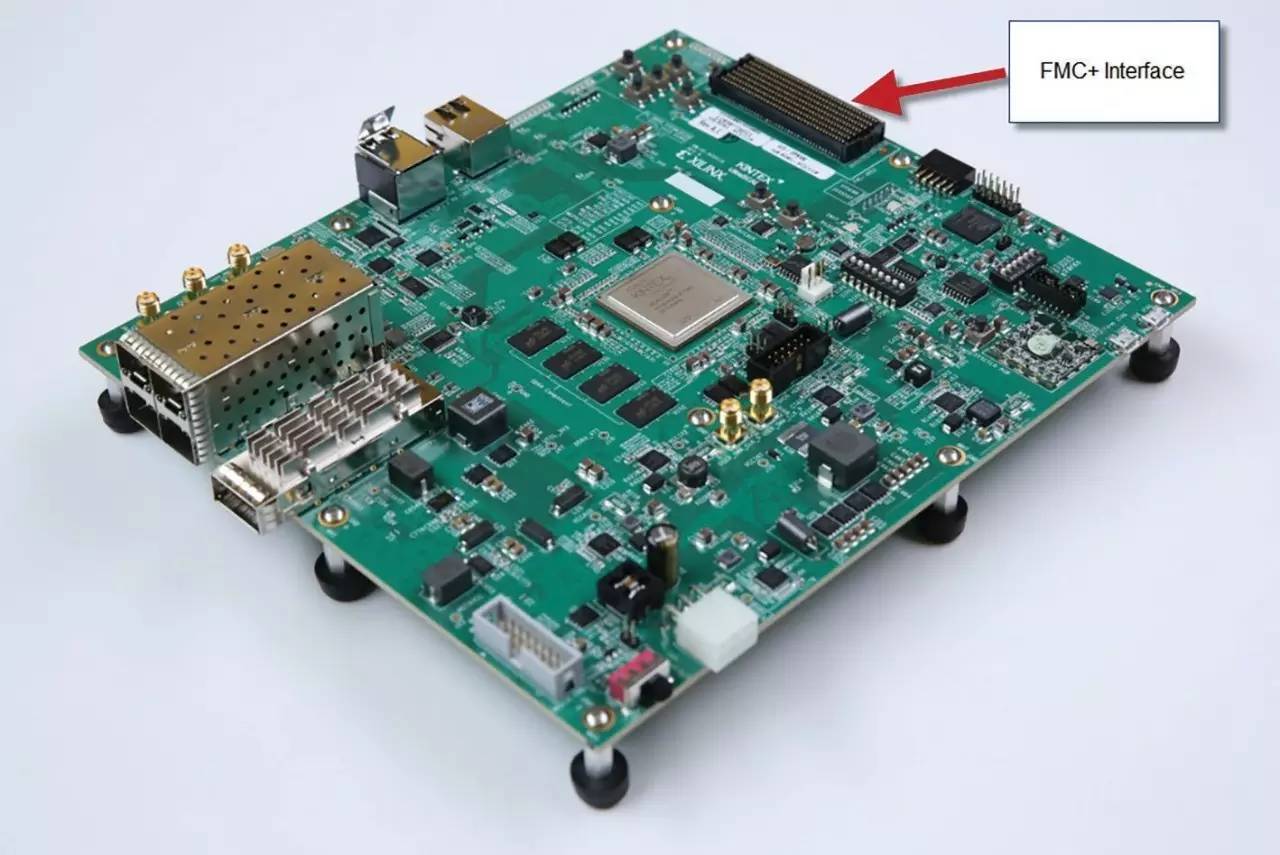

呱呱落地

新一代 FMC 规范已经推出,正在适应串行连接器件推动的新技术。FMC 行业的主要参与者已经开始采用这一规范。图 3 所示的是采用 FMC+ 的第一款赛灵思演示板 KCU114。FMC 标准借助新的 FMC+ 涅槃重生并已呱呱落地,为新一代高性能 FPGA 驱动应用做好了准备。

图 3 - 采用 FMC+ 的赛灵思 KCU114 演示板

-

FPGA

+关注

关注

1628文章

21725浏览量

602911 -

光纤

+关注

关注

19文章

3912浏览量

73119 -

嵌入式设计

+关注

关注

0文章

390浏览量

21283

发布评论请先 登录

相关推荐

FMC+标准对嵌入式设计有什么影响?

FMC+标准将嵌入式设计推到全新的高度

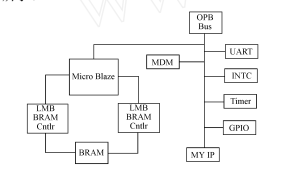

FPGA实现嵌入式系统

AltiumDesigner基于FPGA嵌入式系统设计

基于ARM的FPGA嵌入式系统实现

对嵌入式FPGA的详解

uefi 嵌入式Linux,面向嵌入式平台的高级UEFI开发环境.PDF

FPGA夹层卡对高级嵌入式设计的影响

FPGA夹层卡对高级嵌入式设计的影响

评论