在赛灵思 SDSoC 开发环境发布前,标准 SoC 设计方法涉及一系列不同的工程设计技巧。通常来说,如果系统架构师根据要求生成系统架构和子系统,那么解决方案的功能要分别实现在硬件(逻辑侧)和软件(处理器侧)中。这样,FPGA 和软件工程师要分别开发各自的功能,再根据集成测试计划进行组成和测试。这种方法持续运用了多年,但赛灵思 Zynq-7000 All Programmable SoC 以及即将推出的赛灵思 Zynq UltraScale+ MP-SoC 等功能更强的 SoC 的问世要求采用新的设计方法。

SDSoC 方法能帮助更广泛的工程师用户群开发极高性能系统。在 SDSoC 开发环境中进行开发的工程师新手会发现,可以轻松快速地启动并运行系统,而且系统优化也同样便捷。

我们举一个简单而具代表性的例子来说明如何完成上述任务并获得相应的收益。我们针对的是运行 Linux 的 ZedBoard,并采用内置示例之一:矩阵乘法器和加法模板。

设计方法简史

可编程逻辑器件自 1980 年推出以来一直迅速发展。起初,工程师通过原理图输入法对器件进行编程(虽然 22v10 等较早期的可编程逻辑器件 (PLD) 是通过逻辑方程编程的)。这需要电子工程师执行大部分 PLD 开发工作,因为逻辑设计和优化通常属于电子工程学范畴。随着器件尺寸和功能的不断提升,这种原理图输入法自然开始面临局限性问题,因为设计和验证时间会随着设计复杂性的增加而显著延长。工程师需要具备在更高抽象层上工作的能力。

VHDL 和 Verilog 应运而生。二者开始都是用来描述和模拟逻辑设计(特别是 ASIC)的语言。VHDL 甚至有自己的军用标准。既然我们要在硬件描述语言 (HDL) 中描述逻辑行为,那么自然应该综合所需的逻辑电路。综合工具的开发使得工程师能描述通常在寄存器传输层的逻辑行为。HDL 也能大幅改进验证方法,有助于开发行为测试平台,支持结构化验证。HDL 也首次支持模块化和厂商独立性。

HDL 内在并行性、寄存器传输层设计法和实现流程则需要了解优化和时序收敛,这就意味着 PLD 开发任务大部分落到了电子工程师的身上。

HDL 一直是 PLD 开发领域的事实标准,但多年发展中也考虑到整体产业的发展需求。单就 VHDL 而言,相继于 1987 年(IEEE 采用的第一年)、1993 年、2000 年、2002 年、2007 年、2008 年进行了修订。不过,跟原理图输入法一样,HDL 也逐渐开始面临一系列局限性问题,包括开发和验证时间太长、器件功能要求提高等。

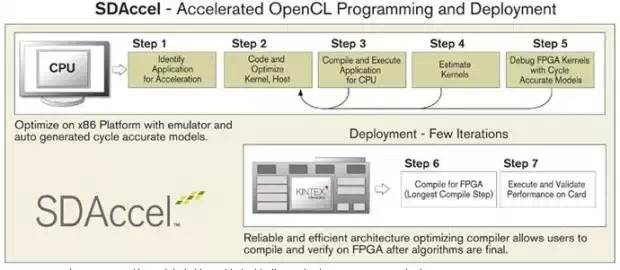

随着 PLD 的角色从胶合逻辑向加速外设甚至最终向系统核心发展,业界需要新的设计方法来满足有关发展需求。近年来,高层次综合 (HLS) 越来越受欢迎。根据高层次综合法,设计通过 C/C++(用赛灵思的 Vivado HLS)或其他工具(如 MathWorks 公司的 MATLAB 或国家仪器公司的 LabVIEW)输入。由于新的设计方法能够充分发挥器件的功能,这种方法开始将设计和实现从电子工程领域转向软件领域,从而显著扩大了潜在的 PLD 设计人员群体,并巩固了 PLD 作为系统核心的地位。

因此,SoC 设计自然能用 HLS 来生成紧密集成的开发环境,工程师则能在环境中无缝加速设计逻辑侧功能。在此情况下,SDSoC 环境应运而生。

熟悉的环境

SDSoC 开发环境基于 Eclipse,大多数软件开发人员对这种环境应该是比较熟悉的(图1)。该环境通过采用能处理 C 或 C++ 程序的全新 SDSoC 编译器无缝支持器件可编程逻辑 (PL) 侧功能加速。

SDSoC环境中使用最高抽象层进行开发,具体如下:

在 C 或 C++ 中开发应用。

对应用进行特性分析,明确性能瓶颈问题。

使用特性分析信息,明确器件 PL 侧哪些功能需要加速。

随后构建系统并生成 SD 卡映像。

硬件到位后,进一步分析性能并根据要求优化加速功能。

我们能在 SDSoC 环境中开发出可在裸机、FreeRTOS 或 Linux 操作系统上运行的各种不同应用。该环境内置支持 ZedBoard、MicroZed 和 Digilent ZYBO 等大部分 Zynq SoC 开发板。这样,我们不仅能加速开发应用,还能通过该功能定义自己的底层硬件平台,在自己的定制硬件平台能用于集成时使用。

在 SDSoC 环境中编译程序时,构建过程输出提供了从 SD 卡配置 Zynq SoC 所需的系列文件。该系列文件包括一级和二级引导载入程序,以及操作系统所需的应用和映像。

SDSOC 实例

下面我们看看 SDSoC 环境如何工作,多快就能让实例启动并运行起来。我们针对的 ZedBoard 开发板运行 Linux 操作系统并使用内置矩阵乘法器和加法模板。

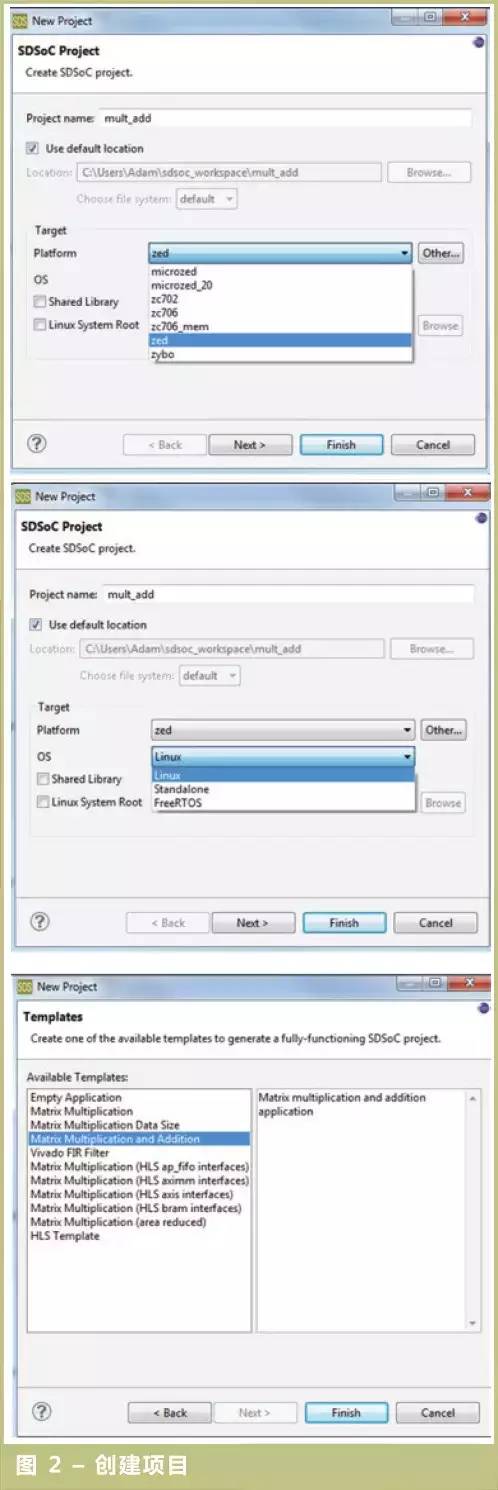

首先一如既往地创建项目。我们能通过欢迎窗口(图 1)或通过菜单选择“File -> New -> SDSoC”项目来创建项目。这两种方法都能打开对话框,让我们给项目命名,选择开发板和操作系统(图 2)。

这将在 SDSoC GUI 左侧 Project Explorer 下生成项目。我们在该项目下会看到以下文件夹,每个文件夹都有自己唯一的图标:

SDSoC 硬件功能:这里我们能看到转移到硬件的功能。一开始这个文件夹是空的,等待我们转移。

Includes:展开这个文件夹能看到构建过程中使用的所有 C/C++ 报头文件。

src:包含演示用源代码。

为确保我们正确配置所有事项,包括 SDSoC 安装和环境以及开发板,我们要构建演示,其只在器件片上处理系统 (PS) 侧运行。

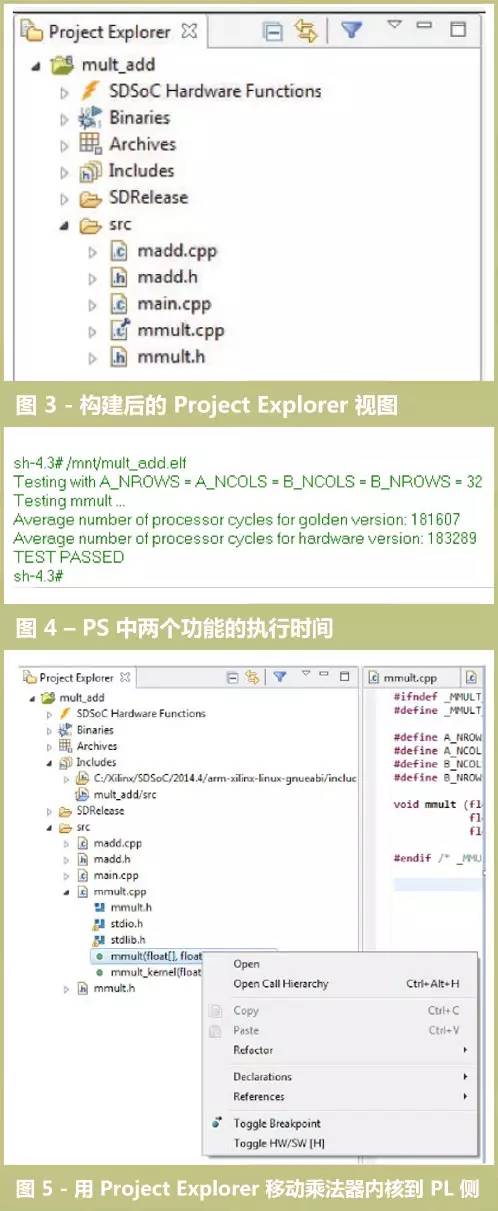

当然,下一步就是构建项目了。在菜单上选中项目,我们选择“Project->Build Project”。构建时间不会太长。完成后,会看到如图 3 所示的文件夹出现在 Project Explorer 中的项目下。除了上述文件夹之外,还有:

二进制文件:这里能找到软件编译过程生成的可执行连接 (ELF) 文件。

归档:链接对象文件,创建其中的二进制文件。

SDRelease:包含我们的引导文件和报告。

我们已经构建了首个演示,只能在 Zynq SoC 的 PS 上运行,下面我们来看看如何确保其按预期正常运行。对应用进行特性分析,明确 SDSoC 加速运行。工程师用特性分析信息明确应该移动哪些功能。

我们用已提供的 sds_lib.h 库在基本层面进行特性分析,这能在 64 位全局计数器上获得基本时间戳 API,让我们测出每个功能的用时。我们用API 能简单记录功能开始和停止时间,这一时间差就是整个过程的执行时间。

源代码包括两个版本的矩阵乘法和加法算法。所谓的黄金版不用于转移到片上可编程逻辑 (PL);另一版则针对这个目的。通过在 PS 中构建并运行,我们能确保有针对性地对比,而且两个流程执行时间基本相同。

构建完成后,我们能拷贝“Project Explorer 下 SDRelease -> sd_card”文件夹中的所有文件到 SD 卡,然后将 SD 卡插到 ZedBoard 上(SD 卡配置的模式引脚要正确设置)。终端程序连接以及引导序列完成后,我们就要运行程序。输入“/mnt/mult_add.elf”(这里的 mult_add 是我们创建的项目的名称)。在 ZedBoard 上运行,得到如图 4 所示的结果,显示两个功能运行的时间基本相同。

验证执行时间基本相同后,我们将乘法函数移到 SoC 的 PL 侧,这步很容易实现。

分析实例中 src 目录的文件结构,我们看到:

main.cpp:这包含主函数、黄金计算、时间戳和器件硬件侧所用的乘法加法函数调用。

mmult.cpp:这包含在硬件部分运行的乘法函数。

madd.cpp:这包含在硬件部分运行的加法函数。

完成上述步骤后,下次构建项目时,SDSoC 链接器会自动调用赛灵思 Vivado HLS 和Vivado 来执行 SoC 中 PL 侧的功能。

下一步就是将一个函数转移到 SoC 的 PL 侧。我们通过以下两种方法之一能完成这一任务:

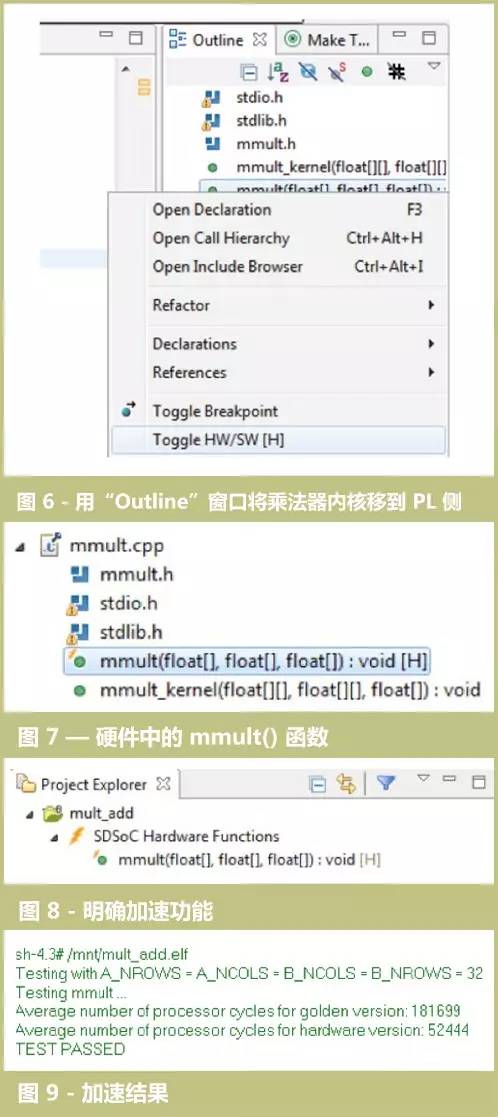

在 Project Explorer 中,我们展开文件,看到文件中的函数,选择感兴趣的函数,右键点击并选择“Toggle HW/SW [H]”(图5)。

打开文件并执行右侧“outline”标签下的同样选项,这也能显示函数(图 6)。

开关硬件中加速的 mmult() 函数能让 [H] 添加到函数后面(图 7)。

我们还会看到 SDSoC Hardware Functions 下选择的功能(“Project Explorer”标签中项目下方,图 8)。这能让我们方便地看到设计中加速的所有功能。

完成上述步骤后,下次构建项目时,SDSoC 链接器会自动调用赛灵思 Vivado HLS和Vivado Design Suite 其余部分来执行 SoC 中 PL 侧的功能。与此同时,会创建软件驱动程序,支持功能加速。我们看到,功能转移到器件 PL 侧是无缝的,而且还会提高性能。

编译和生成 SD 卡映像后,我将 mmult() 函数移到硬件,在 ZedBoard 上运行。如图 9 所示,执行时间(处理器工作循环)只有 52,444 / 183,289 = 0.28,也就是此前期间 PS 侧 183,289 个处理器工作循环(执行时间)的 28%(图 4)。考虑到器件 PS 侧相同功能的性能,我们看到只需简单点击鼠标就能大幅改进执行时间。

-

子系统

+关注

关注

0文章

110浏览量

12468 -

系统构架

+关注

关注

0文章

5浏览量

6262

发布评论请先 登录

相关推荐

赛灵思表示将推出更多功能更强的设计方案

赛灵思表示将推出更多功能更强的设计方案

评论