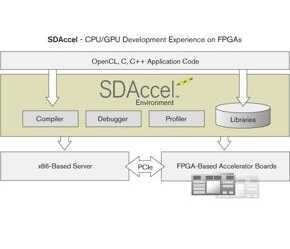

OpenCL 标准为软件开发人员提供了一个统一的编程环境,可编写高效、可移植的代码,实现丰富的算法,SDAccel 开发环境符合 Khronos OpenCL 1.0 标准, 因此可以轻松地在 FPGA 上对 OpenCL 进行加速。

Xilinx 已经形成一个联盟成员的全球生态系统,可提供各种平台、库和设计服务帮助全球设计团队充分利用在其 OpenCL、C 和 C++ 应用中基于 FPGA 的加速。

以下通过两个视频向您详细介绍 OpenCL 应用架构,以及内存架构,并同时还向您演示如何使用赛灵思 FPGA 进行加速。

OpenCL 应用架构详解

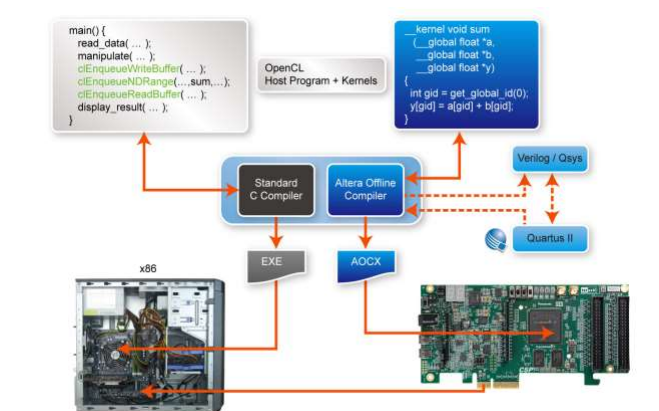

OpenCL 中对于异构计算应用为所有的实现定义了一个基本的编程模型标准。本视频介绍了一个 基于 OpenCL 应用的主机代码和内核元素,并演示了这些元素包含 FPGA 加速器对系统映射的解释

OpenCL 内存架构详解

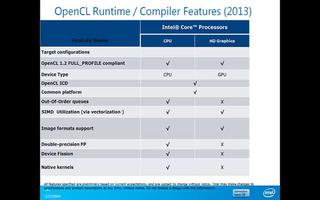

OpenCL 定义了一个内存架构和抽象模型,是一个可应用于计算设备的通用标准。这就意味着程序员只需要了解一个可简化应用编程的内存模型就足够了。本视频提供了对 OpenCL 内存模型架构的详解,并演示了如何在 FPGA 加速器件上实现它。

-

FPGA

+关注

关注

1629文章

21754浏览量

604236 -

赛灵思

+关注

关注

32文章

1794浏览量

131334 -

编程

+关注

关注

88文章

3627浏览量

93809

发布评论请先 登录

相关推荐

Intel altera opencl 入门

什么是OpenCL?面向FPGA的OpenCL有什么优点?

介绍android下的OpenCL开发步骤

Altera发布业界第一个面向FPGA的OpenCL计划

面向Altera FPGA的OpenCL:提高性能和设计效能

OpenCL 代码的可移植性优势及异构系统中的应用

为OpenCL应用创建、构建和调试英特尔SDK的OpenCL代码

英特尔SDKfor OpenCL使用介绍

OpenCL应用程序的主机代码和内核元素

适用于OpenCL,C和C ++的Xilinx SDAccel集成开发环境

如何使用OpenCL轻松实现FPGA应用编程

Intel Cyclone V 开发板OpenCL使用手册免费下载

OpenCL编程环境作用和介绍

OpenCL编程环境作用和介绍

评论