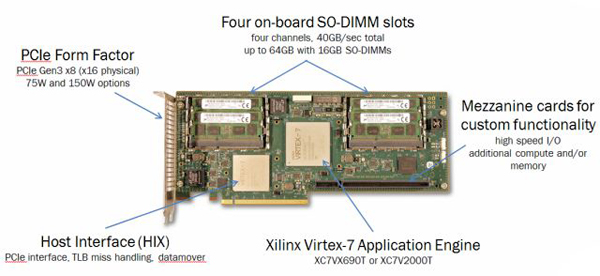

在New Orleans举办的超级计算机大会(SC14)上,Convey Computer公司介绍了很多关于HLL(高级语言)的标准扩展和利用FPGA实现加速的应用等内容。Convey公司制造了一整套的基于FPGA的硬件加速器板卡,支持PCIe计算接口和服务器系统包裹Wolverine(”金刚狼”),这些设计都是基于Xilinx Virtex-7系列FPGA芯片。Convey公司是目前几个能够提供加速器板卡商业成品的提供商之一,加速器板卡也是这次Xilinx公司推出的SDAccel开发环境的一部分。( 为OpenCL,C, C++打造类似于CPU/GPU的软件开发环境)

基于FPGA的加速器应用Wolverine(”金刚狼”),支持PCIe系统

在SC14会议上Convey公司的展台采用信息海报的形式,提供了大量关于使用高级语言(HLL)来加速基于FPGA的应用代码的开发。下面我将引用海报的重点部分,以防你错过了Convey公司的展台,或者不能亲自来New Orleans参加SC14会议:

以前加速器应用设计主要使用硬件描述语言(HDL)例如Verilog来进行程序设计。这就需要专门的技能和工具软件,这就限制了这个器件不能被更多的人所接触到。

最近,加速器编程标准已经推出,主要为便携式应用的设计提供支持,这个标准主要面对不同提供商的加速器。这里我们介绍一下由Convey Computer公司开发的OpenMP编译器原型和由Xilinx公司开发的OpenCL编译器.(也就是Xilinx公司推出SDAccel开发工具软件)

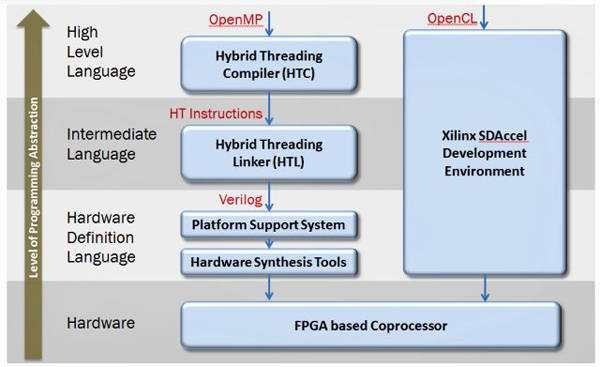

FPGA是一块可编程的集成电路,通过编程可以实现不同的电路设计,这些设计是通过硬件描述语言(HDL)例如Verilog具体实现的,通过硬件综合工具将硬件描述语言代码转换成比特流文件,下载到器件中完成对电路的配置。

Convey公司的OpenMP编译器采用OpenMP4.0加速器指令,将它们转换为公司的混合线程(HT)来表示。中间语言包括将基于C++和实时运行库的高级编程指令相结合,主要是为了能够访问系统的底层设备。这个工具集将HT转化为Verilog语言,很多工作都是自动完成的,包括创建复用并行单元和转化工作顺序表。生成的Verilog语言代码和由硬件平台提供的系统底层驱动代码会被综合生成比特流文件,最后将比特流文件下载到处理器中,完成配置。

Xilinx公司SDAccel开发软件能够实现将OpenCL应用代码编译成二进制文件,这些二进制文件是能够被处理器所识别的,并执行,编译过程采用标准的编程开发环境。下面的插图展示了这两种编译器是怎么工作的:

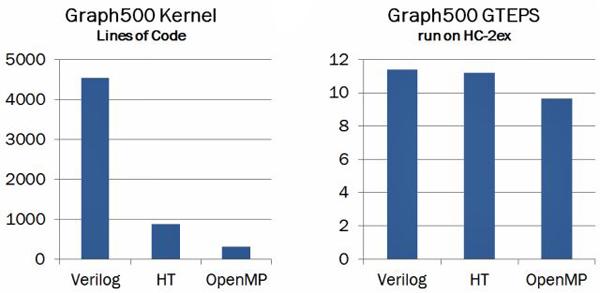

使用高级编程工具将需要更少的代码来实现功能的描述,这就可以让程序员将更多的精力放在算法的研究上,而不是为搭建一些底层驱动伤脑筋。

例如,手工实现的Graph500广度优先搜索内核使用Verilog语言大概包括超过4500多行的代码,同样的内核实现使用混合线程(HT)中间过渡语言只需要883行代码。使用OpneMP版本的内核只需304行C语言代码,使用OpenMP实现的内核性能是9.7 GTEPS,使用Verilog语言的内核性能是11.4GTEPS,使用HT语言的内核性能是11.2GTEPS,相比较而言还是可以接受的。

从这个例子所显示出的意义来看,使用OpenMP代码实现的简单内核性能完全可以与Verilog语言实现的内核性能相匹敌,例如Graph500,使用OpenMP实现的版本可以达到Verilog语言实现版本性能的85%,但是却只需要更少的代码量。

这次对高级语言标准扩展的介绍允许将基于FPGA的加速器应用的程序设计大大简化。基于这些标准的编程工具可以生成高度并行的硬件设计,而且性能完全可以与采用底层硬件描述语言实现的设计性能相匹敌。

---> END <---

-

超级计算机

+关注

关注

2文章

464浏览量

42068 -

C语言

+关注

关注

180文章

7618浏览量

138228 -

加速器板卡

+关注

关注

0文章

2浏览量

2293

发布评论请先 登录

相关推荐

无法导入硬件加速器

高级语言(HLL)标准扩展大大简化基于FPGA加速器的应用程序的开发

Bitfusion支持通过云访问基于赛灵思All Programmable器件的FPGA硬件加速功能

利用硬件加速器提高处理器的性能

赛灵思公司与SK电讯技术结合,加速FPGA加速器在AI领域的应用

基于Xilinx FPGA的Memcached硬件加速器的介绍

赛灵思公司与SK电讯宣布SKT已在其数据中心中部署赛灵思FPGA

Vitis在Alveo 板卡上加速应用案例

赛灵思系列芯片支持Convey Computer公司的硬件加速器板卡

赛灵思系列芯片支持Convey Computer公司的硬件加速器板卡

评论