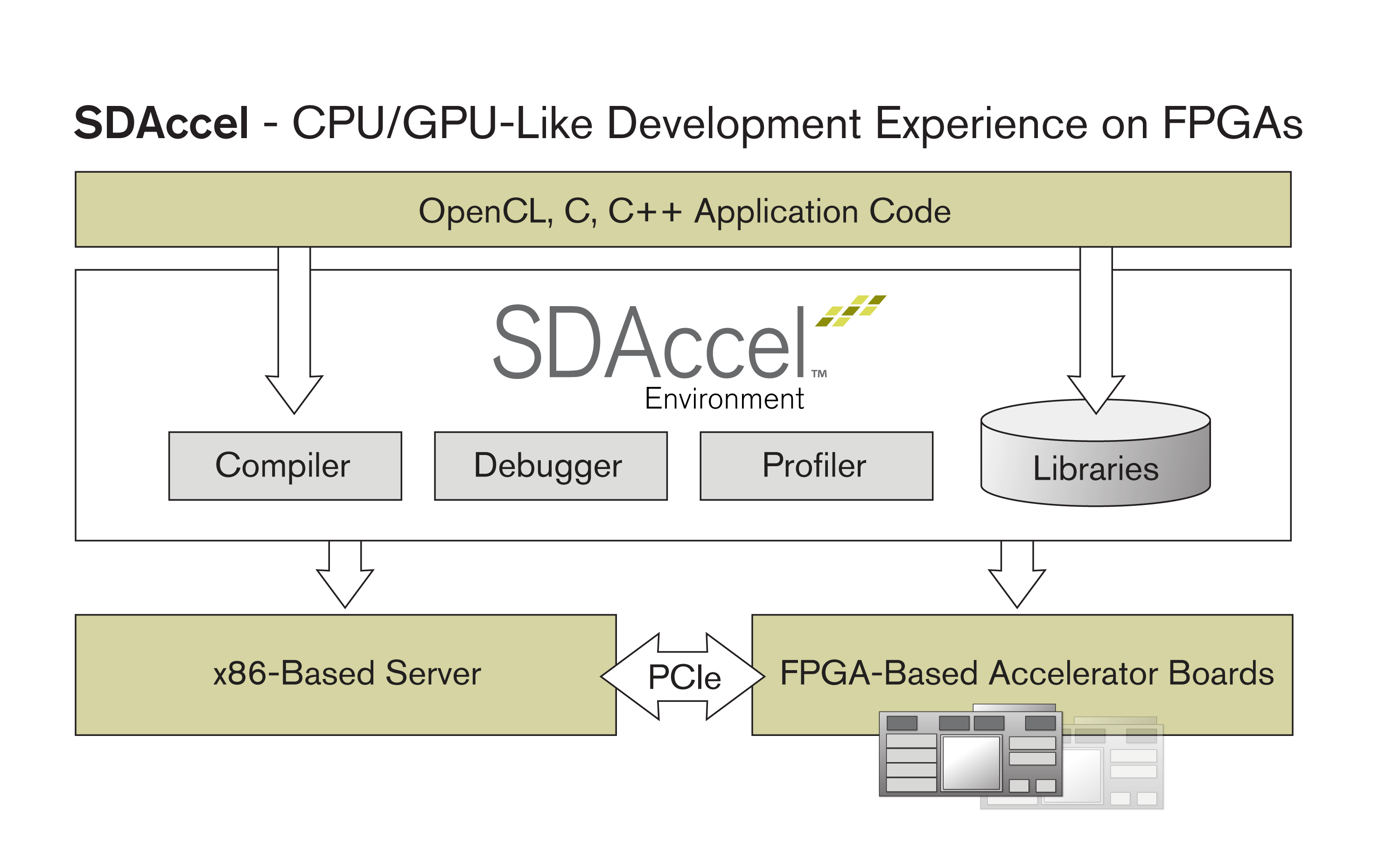

All Programmable 技术和器件的全球领先企业赛灵思公司(Xilinx, Inc. (NASDAQ:XLNX))在国际超算大会(Super Computing 2014)上宣布推出针对OpenCL、C和C++的SDAccel开发环境,将单位功耗性能提高达25倍,从而利用FPGA实现数据中心应用加速。SDAccel是赛灵思SDx系列的最新成员,将业界首款支持OpenCL、C和C++内核任意组合的架构优化编译器、库、开发板完美结合在一起,在FPGA上首次实现了完全类似CPU/GPU的开发和运行时间体验。

图:赛灵思亚太区销售及市场副总裁,杨飞正在介绍 SDAccel 所带来的优势

戴尔公司平台架构与技术及CTO 办公室执行总监Robert Hormuth指出:“基于FPGA的技术有了新的突破,能支持优化的计算应用。在戴尔服务器部署的过程中,简化编程是决定采用FPGA加速器的关键障碍。。毫无疑问,赛灵思开辟了一条正确的道路,让开发人员能够借助一个软件环境,提高FPGA平台用户的生产力。”

IBM电源开发副总裁兼OpenPOWER基金会总裁Brad McCredie表示:“IBM高度赞赏赛灵思致力于实现其FPGA软件可编程性这一发展方向。利用C、C++和OpenCL创建优化型FPGA加速器的高度灵活性和可靠的结果质量,能提升IBM为客户带来更大价值的能力。IBM坚信OpenCL对提高生产力大有裨益,同时我们正在与赛灵思展开紧密合作,将该技术应用到我们的OpenPOWER产品设计中。”

首款针对OpenCL、C和C++的架构优化编译器

SDAccel的架构优化编译器相对CPU或GPU,单位功耗性能提高达25倍,相对其它FPGA解决方案,性能和资源效率提高3倍。SDAccel采用了已被1,000多名程序员广泛使用的基础编译器技术。SDAccel充分利用该编译器的功能,使软件开发人员能够利用新的或现有的OpenCL、C和C++ 代码创建高性能加速器,并针对计算搜索、图像识别、机器学习、编码转换、存储压缩和加密等各种数据中心应用中的存储器、数据流和流水线技术进行了精心优化。

在FPGA上首次实现完全类似CPU/GPU的开发体验

借助SDAccel,开发人员能够使用其熟悉的工作流程优化应用,而且即便之前没有FPGA使用经验,也能受益于FPGA平台的优势。集成设计环境(IDE)不仅可提供编码模板和软件库,而且还能对各种开发目标进行编译、调试和特性分析,如在X86平台上仿真、使用快速仿真进行性能验证以及在FPGA处理器上进行本地执行等。IDE可在数据中心用FPGA平台上执行应用。该平台配套提供面向所有支持开发目标的自动仪器插入功能。此外,SDAccel还经过精心设计,使CPU/GPU开发人员能够轻松将其应用迁移到FPGA上,同时还可在他们熟悉的工作流程中维护和复用OpenCL、C和C++代码。

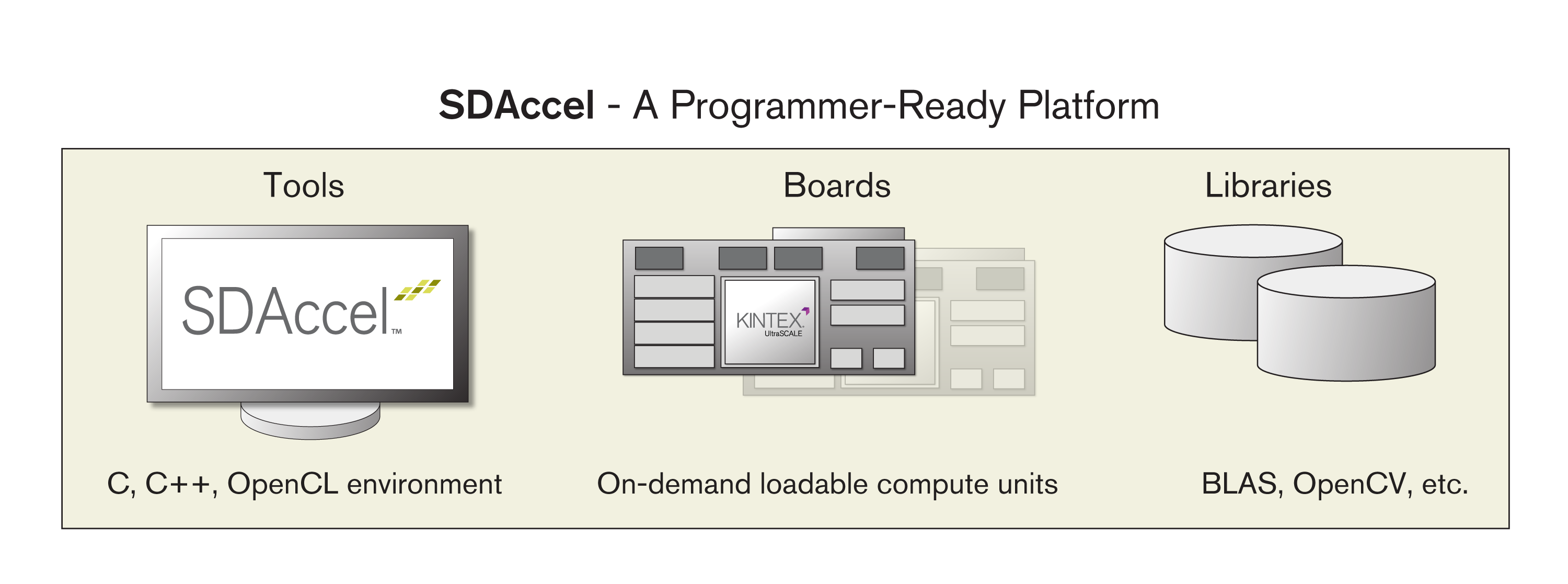

综合全面的SDAccel环境包括编程器用IDE、基于C语言的FPGA优化库,以及数据中心用现成商用(COTS)平台。

SDAccel库包括用于高性能低功耗实现方案的内置OpenCL函数、DSP、视频以及线性代数库。针对特定领域加速,赛灵思联盟合作成员Auviz Systems提供了精心优化的OpenCV和BLAS OpenCL兼容型软件库。原有的COTS成员包括Alpha Data、Convey、Pico Computing,预计2015年年初还将增加更多成员。

在FPGA上首次实现完全与CPU/GPU的运行时间体验

只有SDAccel能够支持带有多个程序和类似CPU / GPU按需可加载计算单元的应用。与CPU/GPU类似,SDAccel对于FPGA解决方案的独特之处,在于能够保持程序转换过程中的系统正常工作。SDAccel是业界唯一能够创建可在应用运行过程中加载新加速器内核的FPGA计算单元的环境。 在整个应用执行过程中,存储器、以太网、PCIe和性能监控器等关键系统接口和功能均保持工作状态。即时可重配置的计算单元可让多个应用共享FPGA加速器。例如通过对运行系统编程,可支持图像搜索、视频转码和图像处理之间的切换。

供货情况

赛灵思在美国新奥尔良市举行的2014国际超算大会上实时演示了SDAccel产品。如需了解更多SDAccel早期试用版的功能,敬请联系本地的销售代表。

该产品基于已发布的Khronos规范,有望通过Khronos一致性测试过程。

SDx是面向系统和软件工程师的一系列开发环境。SDx让具备较少甚至没有FPGA专业知识的开发人员也能够利用高级编程语言充分发挥可编程硬件和业界标准处理器的功能优势。

-

赛灵思

+关注

关注

32文章

1794浏览量

131246 -

开发环境

+关注

关注

1文章

225浏览量

16609

发布评论请先 登录

相关推荐

Lumen将AI光纤交易链接亚马逊数据中心

数据中心对MOS管性能的要求

Fujitsu 和 Supermicro 宣布战略合作,共同开发绿色 AI 计算技术和液冷数据中心解决方案

SK海力士推出高性能数据中心SSD PEB110

安森美引领数据中心能效革命

安森美推出提高数据中心能效的完整电源解决方案

安森美推出新款碳化硅芯片,助力AI数据中心节能

Rapidus携手Esperanto研发低功耗数据中心AI半导体

谷歌推出Trillium AI芯片,性能提高近5倍

赛昉科技与超聚变达成战略合作,RISC-V在数据中心迎来历史性跨越

赛灵思宣布推出新的开发环境,将数据中心的单位功耗性能提高达25倍

赛灵思宣布推出新的开发环境,将数据中心的单位功耗性能提高达25倍

评论