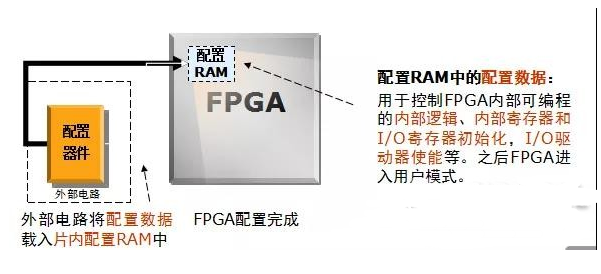

目前,大多数FPGA芯片是基于 SRAM 的结构的, 而 SRAM 单元中的数据掉电就会丢失,因此系统上电后,必须要由配置电路将正确的配置数据加载到 SRAM 中,此后 FPGA 才能够正常的运行。

常见的配置芯片有EPCS 芯片 (EPCS4、EPCS8、EPCS16、EPCS64、EPCS128),还有通用的串行 SPI FLASH 芯片如 M25P40、 M25P16、 W25Q16 等。

配置(configuration)是对FPGA的内容进行编程的过程。每次上电后都需要进行配置是基于SRAM工艺FPGA的一个特点,也可以说是一个缺点。FPGA配置过程如下:

FPGA配置方式

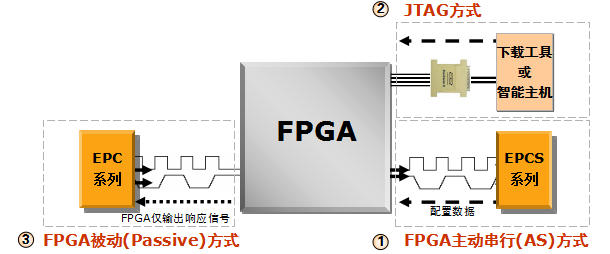

根据FPGA在配置电路中的角色,可以将配置方式分为三类:

1.FPGA主动串行(AS)方式

2. JTAG方式

3. FPGA被动(Passive)方式

FPGA配置过程

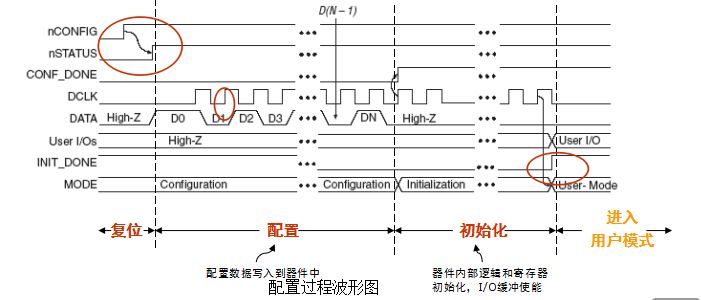

FPGA的配置包括3各阶段:复位、配置和初始化。

FPGA正常上电后,当其nCONFIG管脚被拉低时,器件处于复位状态,这时所有的配置RAM内容被清空,并且所有I/O处于高阻态,FPGA的状态管脚nSTATUS和CONFIG_DONE管脚也将输出为低。当FPGA的nCONFIG管脚上出现一个从低到高的跳变以后,配置就开始了,同时芯片还会去采样配置模式(MSEL)管脚的信号状态,决定接受何种配置模式。

随之,芯片将释放漏极开路(open-drain)输出的nSTATUS管脚,使其由片外的上拉电阻拉高,这样,就表示FPGA可以接收配置数据了。在配置之前和配置过程中,FPGA的用户I/O均处于高阻态。

在接收配置数据的过程中,配置数据由DATA管脚送入,而配置时钟信号由DCLK管脚送入,配置数据在DCLK的上升沿被锁存到FPGA中,当配置数据被全部载入到FPGA中以后,FPGA上的CONF_DONE信号就会被释放,而漏极开路输出的CONF_DONE信号同样将由外部的上拉电阻拉高。因此,CONF_DONE管脚的从低到高的跳变意味着配置的完成,初始化过程的开始,而并不是芯片开始正常工作。

INIT_DONE是初始化完成的指示信号,它是FPGA中可选的信号,需要通过Quartus II工具中的设置决定是否使用该管脚。在初始化过程中,内部逻辑、内部寄存器和I/O寄存器将被初始化,I/O驱动器将被使能。

当初始化完成以后,器件上漏极开始输出的INIT_DONE管脚被释放,同时被外部的上拉电阻拉高。这时,FPGA完全进入用户模式,所有的内部逻辑以及I/O都按照用户的设计运行,这时,那些FPGA配置过程中的I/O弱上拉将不复存在。不过,还有一些器件在用户模式下I/O也有可编程的弱上拉电阻。在完成配置以后,DCLK信号和DATA管脚不应该被浮空(floating),而应该被拉成固定电平,高或低都可以。

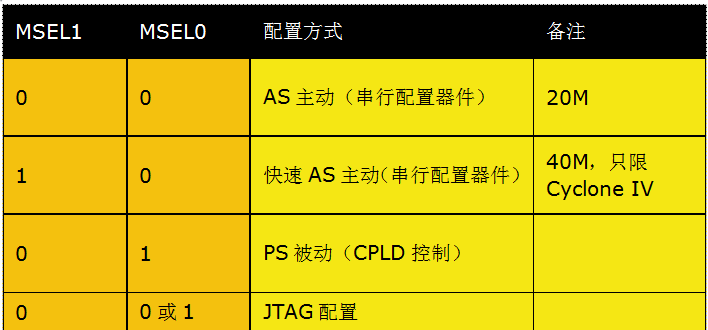

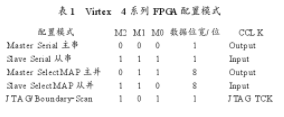

FPGA配置模式选择

用户可以通过设置FPGA上的MSEL0、MESL1两个引脚的状态来选择配置方式。各种方式的MSEL0、MESL1设置如下表所列:

说明:

在上表中,如果只采用一种配置方式,则可以直接将MSEL0、MESL1连接到VCC(注意要与FPGA的IO口的供电VCCIO相同)或GND;

如果需要多种配置方式,那么MSEL要用控制器(单片机、CPLD等)来控制以进行切换;

MSEL管脚在配置开始前必须处于一个固定的状态,因此不能将MSEL管脚悬空。

主动串行配置

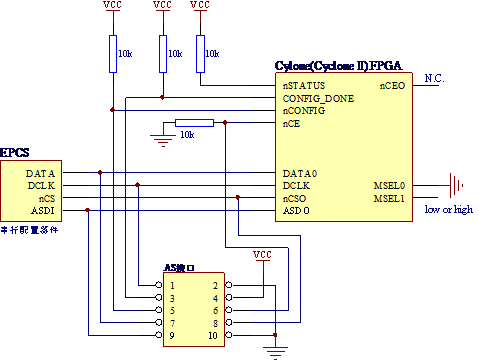

主动串行配置方式(AS)是将配置数据事先存储在串行配置器件EPCS中,然后在系统上电时Cyclone IV FPGA通过串行接口读取配置数据(如果是压缩数据,还会进行解压缩处理)对内部的SRAM单元进行配置。

因为上述配置过程中FPGA控制配置接口,因此通常称为主动配置方式。在配置期间,Cyclone IV用过串行接口来读配置数据,来对里面的SRAM编程。串行配置器件的四个接口包括,串行时钟输入DCLK,串行数据输出DATA,低有效的片选信号NCE,串行数据输入ASDI。

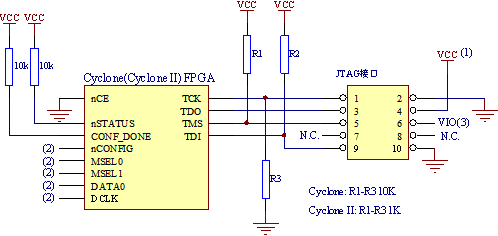

主动串行配置电路图:

因为FPGA上的nSTATUS、CONFIG_DONE管脚都是开漏结构,所以都要接上拉电阻。FPGA的片选脚nCE必须接地。

JTAG配置

通过JTAG接口,利用Quartus II软件可以直接对FPGA进行单独的硬件重新配置。Quartus II软件在编译时会自动生成用于JTAG配置的.sof文件。

如果同时使用AS方式和JTAG方式来配置FPGA,JTAG配置方式拥有最高的优先级,此时AS方式将停止,而执行JTAG方式配置。

利用Quartus II软件和USB Blaster等下载电缆可下载配置数据到FPGA。Quartus II软件可以验证JTAG配置是否成功。JTAG配置通过下载电缆使用SOF、Jam或者JBC文件直接对FPGA进行配置,这种配置方式只能用于调试阶段,因为,掉电后FPGA中的配置数据将丢失。

被动串行配置

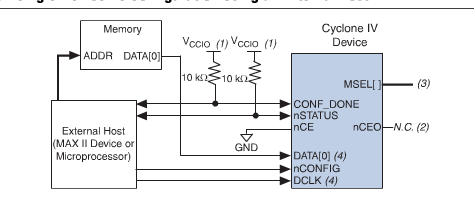

被动串行PS配置方式是Altera Cyclone IV系列FPGA配置方式中比较常用的方式。但是,在工程应用中若采用这种配置方式,FPGA需要连接一个智能主机(比如复杂可编程逻辑器件CPLD/微控制单元MCU等)以给其提供配置时钟和配置数据。

在该配置方式下,智能主机在保证与存储配置数据的闪存通信无误的情况下,只需向FPGA提供一个DCLK信号和一个DATA0信号即可实现对FPGA的配置。另外,该DCLK信号还可以实现多种频率以满足用户对配置时间的需求,这是该配置方式的一大亮点。

本文介绍了以Altera型的FPGA芯片为例介绍了FPGA的上电过程,并描述了三种常见的配置模式,用户可以根据不同的需求来采用对应的配置模式,每种配置模式下对应的配置数据类型也是不相同的。

今天的内容就到这了,如果您对文章内容方面还有疑问,可以扫描下方二维码,会有专门的老师帮你解决。

扫描失败可添加微信号:18138814636

加入发烧友VIP会员获取更多学习资料请点击下方链接:

﹌﹌﹌﹌﹌﹌﹌﹌﹌﹌﹌﹌﹌﹌﹌﹌﹌﹌﹌﹌﹌﹌﹌﹌﹌﹌﹌﹌﹌﹌﹌﹌﹌﹌﹌﹌﹌﹌﹌﹌﹌﹌﹌﹌﹌﹌﹌﹌﹌﹌﹌﹌

免责声明:内容整理自网络,版权归原作者所有,如涉及作品版权问题,请及时与我们联系,谢谢!

————你可能错过的往期干货,更多干货请点击文末阅读原文————

向上划动即可查看更多哦

7、55页PPT!很火的MOS管电路工作原理及详解,没有之一!

1、大神教你DIY | 如何用一块FPGA开发板制作音乐盒?!

3、四旋翼 DIY高大上!用STM32单片机搞定四旋翼无人机飞控

5、史上最具创意鬼才10大DIY详细集锦,你赶紧看看吧!(收藏版)

电子发烧友学院精选

2、【学院推荐】LabVIEW与PLC如何进行Modbus通信?

4、【学院推荐】LabVIEW编程实例:手把手教你按键监视小软件的实现

5、【学院推荐】PCB工程师不得不看:超级实用AD常用快捷键总结

电子发烧友活动推荐

1、关于ESD原理及防护,这篇文章太专业了!点赞!(征文)

3、超强的四轴无人机飞控源代码,支持STM32所有系列(附项目资料)

4、11个电源设计小技巧,看完提高一半的工作效率!(附资料下载)

5、从菜鸟到高手,学习arm32位单片机的必经之路,给大家分享个人经验!

7、学好LLC开关电源设计,你必须要弄懂的原理知识(文末送资料大礼包)

电子发烧友电路精选

2、20个超经典模拟电路,工程师你知道几个?(收藏:附答案下载)

7、太牛了!电路图符号超强科普,不懂物理也能轻松看懂电路图!(推荐收藏)

电子发烧友资料精选

2、STM32大神笔记,超详细单片机学习汇总资料(干货分享)

3、工程师快速提升技能就看这份资料——固态继电器(SSR)使用指南

6、测量电子电路设计资料大全(电路图集+设计方案+制作流程)

电子发烧友热文推荐

7、55页PPT!很火的MOS管电路工作原理及详解,没有之一!

电子发烧友拆解及DIY推荐

1、大神教你DIY | 如何用一块FPGA开发板制作音乐盒?!

3、四旋翼 DIY高大上!用STM32单片机搞定四旋翼无人机飞控

5、史上最具创意鬼才10大DIY详细集锦,你赶紧看看吧!(收藏版)

电子发烧友学院精选

2、【学院推荐】LabVIEW与PLC如何进行Modbus通信?

4、【学院推荐】LabVIEW编程实例:手把手教你按键监视小软件的实现

5、【学院推荐】PCB工程师不得不看:超级实用AD常用快捷键总结

电子发烧友活动推荐

1、关于ESD原理及防护,这篇文章太专业了!点赞!(征文)

3、超强的四轴无人机飞控源代码,支持STM32所有系列(附项目资料)

4、11个电源设计小技巧,看完提高一半的工作效率!(附资料下载)

5、从菜鸟到高手,学习arm32位单片机的必经之路,给大家分享个人经验!

7、学好LLC开关电源设计,你必须要弄懂的原理知识(文末送资料大礼包)

电子发烧友电路精选

2、20个超经典模拟电路,工程师你知道几个?(收藏:附答案下载)

7、太牛了!电路图符号超强科普,不懂物理也能轻松看懂电路图!(推荐收藏)

电子发烧友资料精选

2、STM32大神笔记,超详细单片机学习汇总资料(干货分享)

3、工程师快速提升技能就看这份资料——固态继电器(SSR)使用指南

-

FPGA

+关注

关注

1635文章

21837浏览量

608305 -

时序

+关注

关注

5文章

392浏览量

37526

原文标题:FPGA上电加载时序介绍

文章出处:【微信号:elecfans,微信公众号:电子发烧友网】欢迎添加关注!文章转载请注明出处。

发布评论请先 登录

相关推荐

FPGA上电加载时序介绍

FPGA上电时序加载过程详解

详解FPGA上电加载时序

FPGA配置引脚说明及加载时序

基于多片FPGA自动加载系统的设计

TMS320C61416控制FPGA数据加载设计

不同场景的FPGA外围电路的上电时序分析与设计

FPGA配置模式选择 FPGA上电加载时序介绍

基于DSP芯片TMS320C6416实现上电Flash自行加载FPGA的应用设计

FPGA上电加载时序介绍

FPGA上电加载时序介绍

评论