近年来,由于PMIC、WiFi/BT组合、收发器、图像传感器、模拟/数字功能等智能手机功能的巨大推动力,WLP市场对扇入的需求异常旺盛。目前,WLP领域的扇入市场预计将从2018年的29亿美元稳步增长到2024年的44亿美元,CAGR为6.5%。

扇入式WLP封装通常需要在晶圆级进行全功能测试,然后是机械刀片切割。然而,机械刀片切割可能会导致前侧切屑或背面切屑,这将导致在SMT工艺之前无法检测到的良率问题。此外,由于要求更薄的外形是消费产品的主要发展趋势之一,die在机械上更加易碎,这给供应链参与者带来了新的挑战。

随着薄扇入WLP die升级到大规模生产,这一良率损失不能再不解决,因为成本越来越敏感。厂商对这种潜在的失败非常警惕,并且已经开始积极地寻求解决方案。他们正在寻求改善目前的工艺,以更好的性能和提高板级的可靠性,实质上就是为扇入WLP的die提供侧壁保护。同样重要的是,基于200毫米和300毫米的晶圆都支持扇入式WLP的生产。因此,无论原始晶圆的大小,这种解决方案必须能够管理和处理die。超越扇入式WLP,扇出式封装,能满足所有的要求,已被评估为最佳选择之一,并作为最终采用的技术,以解决这些重大挑战。

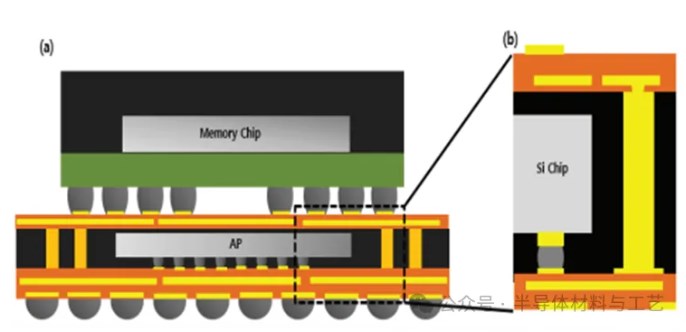

高通已与OSAT合作,通过扇出式封装改进PMIC侧壁保护。高通公司第一次从ASE转向Deca的扇出式封装技术——M系列,用于处理PMIC扇入WLP die周围的侧壁保护。虽然它是Deca的技术,但处理仍然是由ASE完成的。Deca的M系列是一种坚固的,完全成型的扇出工艺,为晶圆级芯片级封装(WLCSP)技术提供高可靠性。在高通的PMIC案例中,Deca的M系列提供了一个4面die保护,可以解决die的侧壁开裂。由于成本考虑,对背面切屑的保护是不处理的。高通的新PMIC采用了Deca的M系列技术,并用于三星Galaxy S10(采用高通骁龙855),这是前所未有的。

Deca公司的M系列由于其在BLR中的可靠性和更好的裂缝和跌落测试结果等优点而被高通公司选为PMIC die的封装技术。M系列是一种芯片优先的表面处理工艺,在焊料和die之间有一个自然增加的EMC层。这也可以看作是一个应力缓冲层,使更大的焊锡球被放置在更好的螺距,提供显着的更高的可靠性。此外,该工艺还优化了M系列电磁兼容的性能,其力学性能与FC CSP中的IC基板类似,给人以深刻的印象。

Deca这个M系列技术在商业上的胜利向其他竞争技术发出了强烈信号,造成了整个扇出供应链的连锁反应。据了解,M系列的BLR性能比eWLB和扇入高出约3倍,并且在类似的厚薄FC CSP范围内。这有四个重要的原因:首先,在WLP裸硅die中,业界已将扇出封装作为首选技术,因为切割会导致切屑,而且更薄的尺寸标准会加剧这种情况;其次,在扇出封装技术中,最流行的eWLB是由许多大公司,如ASE、Amkor(前Nanium)和JCET集团(前StatsChipPAC)授权和使用的,因为它是一个芯片优先的面朝下流程。这种工艺流程在die和焊料之间没有额外的EMC层,这是提高BLR性能的有利因素;第三,虽然FC CSP在BLR性能上与M系列相当,但在移动应用中,趋势是更薄,因此,由于IC基板厚度的增加,FC CSP失去了吸引力。据了解,M系列甚至可以超过薄FC CSP的BLR性能;最后,物有所值。尽管Deca的M系列ASP高于eWLB,是扇入WLP的两倍,但由于可靠性和质量的提高,良率的提高远远超过了M系列ASP的高利润率。Deca的M系列对客户的吸引力是由于它的技术价值,而不是降低成本。

此外,将M系列工艺流程和最终结构与台积电的inFO进行比较,因为两者都是芯片优先面朝上流程,尽管这两种技术服务于不同的市场细分和设备领域。值得注意的是,台积电的inFO并没有额外的类似Deca的M系列的EMC层,台积电在die和焊料之间只有PBO薄膜。另外,台积电inFO的Cu Stud比Deca的M系列短,增加了一层Cu RDL。据信,台积电正试图通过更大的Cu RDL来补偿光刻的有限分辨率,这不同于Deca的专有自适应模式,该工艺是为了克服模移问题而开发的,其中RDL VIA与Cu Stud的值为+/-0.2um。

最主要的好处在于,扇出封装扩展了I/O面积,提高了die集成的限制和灵活性,所有这些都是在较薄的厚度范围内完成的。显然,现有的扇出封装解决方案,如eWLB和inFO将继续专注于I/O的“扇出”,另一方面,Deca的M系列为扇入die提供了可靠的侧壁保护解决方案,这是一个新的好处。这种方法与传统的扇出封装市场有着显著的区别,并有助于解决许多可制造性、成本、量产和可靠性问题。总之,Deca的M系列在低密度扇出封装或核心扇出市场上取得了令人印象深刻的突破。

来源:Favier Shoo,Yole Développement半导体和软件部门技术和市场分析师;

Santosh Kumar,Yole韩国首席分析师和封装、装配和基材研究总监

编译:南山

声明:本文内容及配图由入驻作者撰写或者入驻合作网站授权转载。文章观点仅代表作者本人,不代表电子发烧友网立场。文章及其配图仅供工程师学习之用,如有内容侵权或者其他违规问题,请联系本站处理。

举报投诉

-

wlp

+关注

关注

0文章

14浏览量

10748 -

Deca

+关注

关注

0文章

2浏览量

4307 -

扇出式封装

+关注

关注

0文章

1浏览量

3789

发布评论请先 登录

相关推荐

解析PPLN晶体在量子技术快速商业化的关键作用(一):应用技术

量子技术,曾经似乎是仅存在于科幻小说中的天方夜谭,但如今逐渐深入到我们的日常中改善我们的生活。而在前端的科研领域,量子技术同样令人兴奋,影响也将越来越显著,而非线性光学(NLO)晶体将在该技术

解析PPLN晶体在量子技术快速商业化的关键作用(一):应用技术

(NLO)将在该技术的商业化过程中发挥关键作用。

*本文来源于英国Covesion公司的白皮书《Non-linear Optical Crystals Used for Quantum

政策与技术并行,共推Robotaxi商业化进程?

高级别自动驾驶的发展离不开政策与技术的双重驱动。政府对“车路云一体化”建设的支持推动了基础设施的完善,同时高级别自动驾驶的监管体系逐步完善,为自动驾驶商业化进程提供了政策保障。从技术角

星闪技术2024年商业化落地成果显著

日前,互联网研究机构艾瑞咨询发布了一份关于星闪技术发展的报告。报告指出,2024年星闪技术实现了商业化落地的高速发展,并取得了令人瞩目的显著成果。 在

华天科技硅基扇出封装

来源:华天科技 在半导体封装领域, 扇出(Fan-Out)技术 正以其独特的优势引领着新一轮的技术革新。它通过将芯片连接到更宽广的基板上,实现了更高的I/O密度和更优秀的热性能。由于

两大巨头合作,加速光纤准直封装商业化!

技术商业化。 这一新达成的许可协议,旨在提升量子技术在各行业(涵盖医疗保健至通信领域)中的核心组件可靠性,从而加速量子技术的整体进步。 Infleqtion公司总裁蒂姆·巴兰斯(Tim

宏景智驾智能驾驶系统的技术迭代及商业化之路

近日,宏景智驾创始人及 CEO 刘飞龙博士作为清华车辆工程专业毕业学长受邀在以“汇聚清华智慧,共谋智能车城”为主题的清华汽车行业校友走进临港活动中进行演讲。 在此次演讲中,他深入探讨了当前智能驾驶市场的发展前景,以及宏景智驾是如何根据市场趋势进行技术升级和商业化量产。

华申瑞利完成Pre-A轮融资,加速EMB技术商业化步伐

的成就不仅为新能源汽车制动系统领域注入了强劲的动力,也标志着华申瑞利在干式线控制动技术EMB(Electro-Mechanical Brake)的研发与商业化进程中迈出了更加坚实的一步。

萝卜快跑爆火的背后,美格智能如何助力无人车商业化?

无人车商业化进程已经迈入加速赛,美格智能将继续坚持研发投入,与产业伙伴共同构建面向智能汽车产业的新质生产力,助力无人车商业化加速发展!

大板级扇出式先进封装研发生产基地项目,签约璧山

领域。 其中,大板级扇出式先进封装研发生产基地项目总投资不低于1亿元人民币(或等值新加坡元),企业计划在璧山建设大板级扇出式先进

文远知行与联想车计算战略合作,推进自动驾驶商业化落地

文远知行与联想车计算达成战略合作,共同推进L4级别自动驾驶解决方案的商业化落地,这一举措无疑为自动驾驶领域注入了新的活力。这次合作不仅彰显了双方在自动驾驶技术方面的深厚积累,也预示着自动驾驶技术

令人惊讶!Deca的扇出式封装技术的新商业化

令人惊讶!Deca的扇出式封装技术的新商业化

评论