集成电路设计自动化软件领导企业新思(Synopsys)近日宣布,面向三星7LPP(7nm Low Power Plus)和更先进工艺的良率学习平台设计取得最大突破,也为三星后续5nm、4nm、3nm工艺的量产和良品率奠定了坚实基础。

量产探索平台(Yield Explorer)是一种复杂的芯片量产良品率学习平台,可用来分析芯片设计、晶圆厂生产、产品测试三大方面的数据,以便帮助工程师找到缺点、改进良品率、提高产能。

现代芯片设计和生产是极为复杂的过程,往往涉及几千个步骤,需要花费数月时间,而芯片的最终良品率取决于整体设计、性能和功耗需求等,因此要想提高芯片生产的成功率,需要对各种因素进行细致的分析。

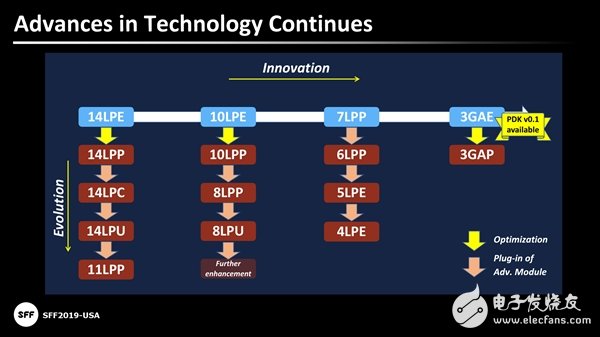

根据路线图,三星工艺近期有14nm、10nm、7nm、3nm三个重要节点,其中14nm会演化出11nm,10nm会演化出8nm,7nm则会演化出6nm、5nm、4nm。

而每种工艺往往又会根据性能、功耗的不同而分为多个版本,比如14nm分成了14LPE、14LPP、14LPC、14LPU,3nm则分成3GAE、3GAP,预计会采用全新的材料。

目前,三星已经完成5nm工艺的设计工作,正在加速推进投入量产,4nm则将在今年下半年完成开发,新思的新平台将在其中发挥巨大作用。

-

芯片

+关注

关注

458文章

51526浏览量

429477 -

三星电子

+关注

关注

34文章

15885浏览量

181567 -

新思

+关注

关注

0文章

21浏览量

29881

发布评论请先 登录

相关推荐

三星3nm良率仅20%,仍不放弃Exynos 2500处理器,欲打造“十核怪兽”

三星电子1c nm内存开发良率里程碑推迟

三星1c nm DRAM开发良率里程碑延期

三星重启1b nm DRAM设计,应对良率与性能挑战

三星芯片代工新掌门:先进与成熟制程并重

三星苏州先进封装厂将扩产

半导体工艺之生产力和工艺良率

三星3nm芯片良率低迷,量产前景不明

三星展望2027年:1.4nm工艺与先进供电技术登场

传三星电子12nm级DRAM内存良率不足五成

三星电子:加快2nm和3D半导体技术发展,共享技术信息与未来展望

受困于良率?三星否认HBM芯片生产采用MR-MUF工艺

新思宣布先进工艺良率学习平台设计取得最大突破 为三星后续先进工艺奠定基础

新思宣布先进工艺良率学习平台设计取得最大突破 为三星后续先进工艺奠定基础

评论