·经 Samsung Foundry 认证,Cadence 工具符合其严格的技术要求,可以助客户实现最佳PPA 目标

·Cadence流程在 Arm Cortex-A53 和Cortex-A57 CPU环境下完成 5LPE 工艺认证

中国上海,2019年7月9日——楷登电子(美国Cadence公司,NASDAQ:CDNS)今日宣布,采用极紫外(EUV)光刻技术的Cadence® 数字全流程解决方案已通过Samsung Foundry 5nm早期低功耗版(5LPE)工艺认证。经认证,Cadence工具符合Samsung Foundry的技术要求,可以帮助移动、网络、服务器和汽车市场高端产品的客户实现最佳功率、性能和面积(PPA)目标。

作为与Cadence长期合作的项目之一,我们已经确认Cadence数字全流程解决方案满足并超出5LPE工艺技术的设计要求,”Samsung Electronics设计技术副总裁Jung Yun Choi表示。“通过部署业界领先的最新Cadence数字流程,结合三星的先进节点工艺,客户可以满怀信心地为移动、网络、服务器、汽车、工业和人工智能等新兴高端市场打造创新产品。

三星在Cortex®-A53 和 Cortex-A57 CPU环境下完成了对Cadence数字流程的5LPE工艺认证。为了易于理解和使用,Cadence数字流程搭载了流程管理器,整个工具链采用一致的用户交互接口。

面向三星5LPE工艺优化的Cadence工具包括:GenusÔ综合解决方案、InnovusÔ设计实现系统、Joules™ RTL电源解决方案、Conformal® 等价性检查工具、Conformal低功耗工具、ModusÔ DFT软件解决方案、QuantusÔ提取解决方案、TempusÔ时序签核解决方案、VoltusÔ IC电源完整性解决方案、物理验证系统、光刻物理分析器和Cadence CMP预测工具。如需了解更多有关Cadence数字和验证全流程解决方案的信息,请访问www.cadence.com/go/dands5lpe.

通过与Samsung Foundry的持续合作,我们帮助客户在日益复杂的时代更快速、更轻松地创建先进节点设计”,Cadence公司数字及签核事业部产品管理副总裁KT Moore说道。“Cadence数字设计实现与签核全流程解决方案和三星5LPE工艺及Arm IP强强联合,为客户提供最新技术,助其优化PPA目标并推进创新。

Cadence高度集成的数字全流程解决方案可以快速实现设计收敛并提高可预测性,也为公司的整体智能化系统设计战略提供了支持,助力客户打造卓越的先进节点SoC设计。

关于Cadence

Cadence 公司致力于推动电子系统和半导体公司设计创新的终端产品,以改变人们的工作、生活和娱乐方式。客户采用 Cadence的软件、硬件、IP 和服务,覆盖从半导体芯片到电路板设计乃至整个系统,帮助他们能更快速向市场交付产品。Cadence 公司创新的“智能系统设计” (Intelligent System Design)战略,将帮助客户开发出更具差异化的产品,无论是在移动设备、消费电子、云计算数据中心、汽车电子、航空、物联网、工业应用等其他的应用市场。Cadence 公司同时被财富杂志评选为“全球年度最适宜工作的100家公司”之一。了解更多,请访问公司网站 www.cadence.com。

© 2019 Cadence Design Systems, Inc. 版权所有。在全球范围保留所有权利。Cadence、Cadence 徽标和 www.cadence.com/go/trademarks 中列出的其他 Cadence 标志均为 Cadence Design Systems, Inc. 的商标或注册商标。Arm 和 Cortex 是 Arm 有限公司(或其子公司)在美国和/或其他地区的注册商标或商标。其他商标均为各自所有者的资产。

-

三星电子

+关注

关注

34文章

15885浏览量

181611 -

EUV

+关注

关注

8文章

609浏览量

86374

原文标题:Cadence 数字全流程解决方案通过三星5LPE工艺认证

文章出处:【微信号:gh_fca7f1c2678a,微信公众号:Cadence楷登】欢迎添加关注!文章转载请注明出处。

发布评论请先 登录

相关推荐

NX CAD软件:数字化工作流程解决方案(CAD工作流程)

三星Galaxy S25 Edge通过3C认证

三星芯片代工新掌门:先进与成熟制程并重

英伟达加速认证三星AI内存芯片

三星半导体印度研究所采用是德科技S-FTL方案优化5G测试流程

三星否认HBM3E通过英伟达测试传闻

概伦电子NanoSpice通过三星代工厂3/4nm工艺技术认证

三星携手红帽成功构建全球首个CXL认证基础设施

三星电子宣布成功构建其首个红帽认证的CXL基础设施

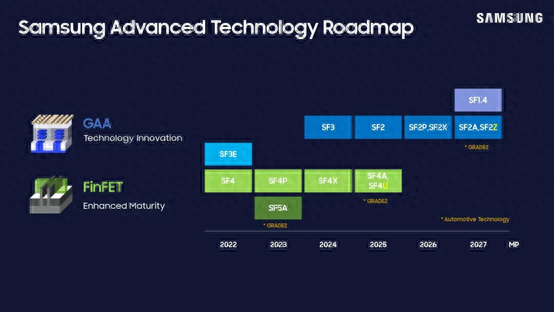

三星公布最新工艺路线图

Cadence 数字全流程解决方案通过三星5LPE工艺认证

Cadence 数字全流程解决方案通过三星5LPE工艺认证

评论