英特尔近日在旧金山召开的SemiCon West上公布了他们在半导体领域最新的研究成果,一共公布了三种新的3D封装工艺,为未来开启了一个全新的维度。芯片封装一直是芯片制造中的一个重头戏,在传统的2D封装技术已经发展到瓶颈之后,半导体制造商们把目光转向了3D堆叠工艺。Foveros是英特尔于2018年提出的3D封装工艺技术,将在今年晚些时候正式发售的LakeField处理器上率先使用。

3D堆叠工艺

芯片封装一直是芯片制造中的一个重头戏,在传统的2D封装技术已经发展到瓶颈之后,半导体制造商们把目光转向了3D堆叠工艺。Foveros是英特尔于2018年提出的3D封装工艺技术,将在今年晚些时候正式发售的LakeField处理器上率先使用。

Co-EMIB

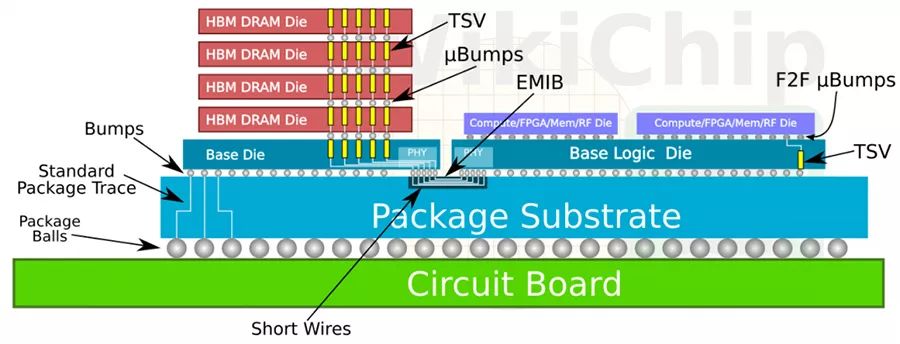

EMIB和Foveros是英特尔用于3D堆栈式封装的两项技术,前者允许芯片模块间的高速内联,后者允许堆叠模块间的垂直通信,这两项技术可以在低功耗的情况下提供非常高的带宽和IO密度。新的Co-EMIB技术是将EMIB和Foveros相结合,同样的,采用Co-EMIB技术的芯片保留了两项技术原有的优点,可以在低功耗高带宽的情况下连接模拟电路、内存以及其他的周边元件。

Co-EMIB示意图,图源WikiChip

ODI

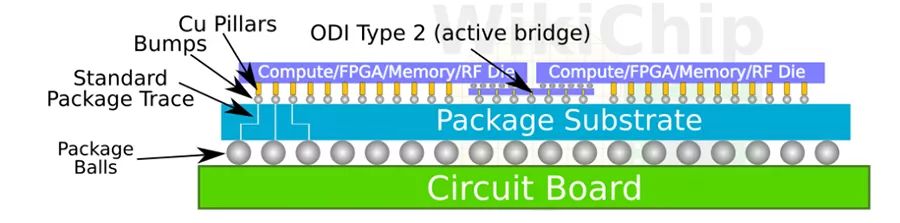

ODI全称Omni-Directional Interconnect,在3D封装中,芯片通信有两个维度,一是水平方向上的芯片间互相通信,另一个是垂直方向上的,比如一个计算模块与另一个独立计算模块通信就是水平方向上的,而计算模块与堆叠在其上的高速缓存通信就是垂直方向上的。新的ODI封装技术减少了与通讯总线接触的面积,这部分节约出来的面积就可以直接连通底层的供电,减少了中间层可能发生的漏电情况,大幅提升了供电性能。

ODI示意图,图源WikiChip

MDIO

MDIO是本次公布的最为概念性的技术,它是一种新的片上互联总线,相比目前使用的AIB(Advanced Interface Bus)物理层,新的总线将提供两倍的带宽和更高的电源效率。

总结

这次公布的三种新型技术都是对未来的芯片封装有着重要作用的技术,它们虽然不会地给我们的PC带来直观性的变化,但是他们给英特尔乃至整个半导体业界更高的灵活性去设计一枚处理器或者是SoC,并且采用3D堆叠技术会在性能上有所提升。在后摩尔定律时代,这种新的技术突破是未来半导体发展的坚实基础。

-

英特尔

+关注

关注

61文章

10043浏览量

172590 -

半导体

+关注

关注

335文章

27885浏览量

224271 -

3D

+关注

关注

9文章

2923浏览量

108204 -

封装技术

+关注

关注

12文章

558浏览量

68078

原文标题:挤牙膏不影响创新,英特尔公布三种3D封装新技术

文章出处:【微信号:mantianIC,微信公众号:满天芯】欢迎添加关注!文章转载请注明出处。

发布评论请先 登录

相关推荐

英特尔代工在IEDM 2024展示多项技术突破

英特尔宣布扩容成都封装测试基地

英特尔推出全新实感深度相机模组D421

立体视觉新手必看:英特尔® 实感™ D421深度相机模组

英特尔IT的发展现状和创新动向

英特尔是如何实现玻璃基板的?

英特尔计划最快2026年量产玻璃基板

英特尔CEO:AI时代英特尔动力不减

英特尔推出全新技术Thunderbolt Share

英特尔公布Gaudi 3 AI加速器中国特供版计划

Ansys和英特尔代工合作开发多物理场签核解决方案

最新技术!英特尔于IFS Direct Connect会议上公布3D芯片技术、逻辑单元、背面供电等未来代工技术!

挤牙膏不影响创新 英特尔公布三种3D封装新技术

挤牙膏不影响创新 英特尔公布三种3D封装新技术

评论