Tesla在4月底首度揭露新一代自驾计算机Full Self Driving(FSD)硬件「Hardware 3」(HW3),近日外界进一步解析这款自驾计算机,可见Tesla将电动车设计成好比一台可移动的智能型手机,但更注重电动车行车安全性,因此为HW3建立更多冗余性,避免任一元件失效或故障时,仍可确保Tesla电动车全自驾计算机的持续运作。

为让未来新一代自驾技术更适合导入电动车,预期Tesla在下一代Hardware 4(HW4)自驾计算机搭载的中央处理器(CPU)、存储器、绘图芯片(GPU)配置、影像讯号处理器(ISP)、镜头分辨率等均会进一步升级,提升HW4可带给Tesla电动车的更高行车安全性。

HW3主要运算、储存元件配置

根据CleanTechnica及The Street报导,Tesla HW3内建两颗自制系统单晶片(SoC),印有Tesla字样,由三星电子(Samsung Electronics)制造。搭载两颗SoC的原因是要建立冗余性,以及提供对行车结果判断的交互参照,并非用来提升整体HW3效能。在两颗Tesla自制SoC下方,各配置两颗快闪存储器用来储存作业系统。Tesla未透露储存容量,外界推测应有达500GB以上。

HW3两颗SoC左右两侧各配置有两颗LPDDR4存储器芯片,合计共配置8颗,虽然SoC是由三星代工生产,但这8颗LPDDR4存储器芯片是采用美光(Micron)产品。实际上美光有面向汽车产业的存储器芯片产品线。外界推测,Tesla在HW3采用美光存储器芯片、而非三星的产品,原因可能出在美光LPDDR4 RAM时脉速率达2133Mhz,比三星的1,600Mhz为高。

HW3两颗SoC尺寸均为260平方公厘,面积比iPhone行动处理器约80~120平方公厘、英特尔(Intel) NB处理器最大约180平方公厘为大,但比NVIDIA的Xavier芯片350平方公厘为小。

Tesla自驾SoC配置NPUNVIDIA芯片所无

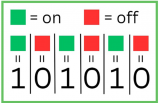

在两颗SoC内部,Tesla配置有GPU、两个神经网络处理器单元(NPU)、CPU、影像讯号处理器等处理器单元,以及DRAM控制器。Tesla称整体SoC和相机镜头取得资料的路径有些相似,首先资料透过Input以每秒最快25亿画素的最大速率进入SoC,之后进入DRAM,这也是该SoC内首个且最主要的瓶颈,因该DRAM是SoC内运行最慢的元件。

接着资料再回到SoC,经过SoC内每秒可处理10亿画素的影像讯号处理器,再这部分会将自驾系统摄影机传感器取得的原始RGB资料转换成实际可用的资料,之后再进入NPU,而在此阶段资料会先被储存进SRAM阵列。

Tesla的NPU配置高达64MB的SRAM,分成两个各32MB的SRAM,用来提供两个NPU支援,对此Tesla认为是一大优势。外界分析,这样的容量或足以储存、渲染及处理所有车用摄影机和传感器输入的单帧(frame)。

所有资料均经由称为「芯片上网络」(Network on a Chip;NoC)的主要通道进行传输,然后是LPDDR4DRAM,通过此资料则以每秒68GB频宽传输。对此Tesla表示已足够,但还可以更好。外界预期Tesla下一代HW4可望进一步提升。

HW3的SoC内建GPU时脉1GHz,效能达600GFLOPS,Tesla称目前用来执行部分后期处理(post-processing)任务,这可能包含创建人类可以理解的图片及影像。从Tesla的介绍,预期下一代HW4的SoC可能会内建体积更小的GPU。

其他不适合由NPU处理的一般通用处理任务,则是由SoC内建CPU负责运算。该CPU内建12个时脉2.2GHz的64位元安谋(Arm) Cortex A72,亦即为内建3个4核心的CPU。

外媒指出,在任何情况下,HW3的新一代SoC效能比前一代HW2内建芯片好上2.5倍。HW2是搭载NVIDIA的Xavier芯片,效能为21~30TOPS,新一代HW3内建SoC则有144TOPS。

值得注意的是,相较于Tesla HW3内建SoC上有两个NPU,NVIDIA为多种目的所设计的Xavier芯片未配置有NPU,即使如此,Xavier仍可运用软件及部分聚焦深度学习(DL)的硬件成功进行模拟。整体而言,Tesla为HW3设计的SoC是一款专用处理器,能够在相当具体处理任务上做得更好,但在一般任务处理用途上可能就不是太管用。

CPU仍采Cortex A72疑为节省成本

外媒不解为何Tesla在HW3的SoC内建CPU中是采用安谋Cortex A72,因为Cortex A72架构早在2015年就已推出,此后安谋还陆续推出更先进的A73、A75核心,甚至不久前再发布新一代A77架构。

对此Musk曾表示,采用2015年版A72架构的原因,是由于A72是两年前Tesla开始设计这款SoC时的最先进核心架构。但外界认为,Tesla采用A72核心可能是出于成本考量,因比较便宜,如果多执行绪效能比单执行绪效能重要,这样的配置是可以被接受的,因此才可见Tesla在其SoC内建CPU中,未另外配置1或2个较新的核心,仅内建3个较旧的4核心。

下一代Hardware 4预料再提升安全性硬件配置全面升级

Tesla下一代Hardware 4(HW4)自驾计算机,预期肯定会进一步提升行车安全性。在此情况下外界预估,很可能HW4的新一代SoC内建CPU,会是采用目前安谋最新发表的Cortex-A75架构核心处理器,因刚好符合Tesla设计新一代SoC的时间点。藉此或有助进一步提高SoC功耗表现及减少内部空间消耗,为配置其他重要零组件腾出更多空间。

HW4存储器芯片可能也会升级至LPDDR5,有助显著加快速度及减少功耗消耗,但如果HW4内建SoC仍尚未完成设计、或要让成本下降,Tesla也可能改用LPDDR4X。LPDDR4X低电压特性也可节省功耗,SoC并行使用时也有助速度提升。

HW4也可能进一步采用更优化的NPU,并配置更高容量SRAM支援;影像讯号处理器也可能升级。外媒分析,Tesla希望其自驾系统SoC能够尽可能低成本又有高效能表现,这也是为何在HW3计算机中,在芯片输入端所能处理的资料量,和影像数位处理器中所能处理的资料量有差异的原因,因此HW4的SoC内部是否会搭载更高处理效能或第2个影像数位处理器,仍要看Tesla在成本、效能、高耗及空间上的取舍而定。

至于HW3的SoC内建GPU效能仍较中规中矩的原因,在于HW3的SoC并非将所有处理任务都交给内建NPU来处理,仍有一部分运算任务委由GPU执行,让Tesla程序设计人员有足够时间重新分配任何剩余的GPU运算任务,给NPU或CPU来执行,所以GPU在Tesla自驾计算机SoC中的配置仍有其必要性。预期HW4自驾计算机SoC内建GPU体积可能会更小,如此情况下NoC配置也会更少,有助腾出更多额外空间内建其他元件。

Tesla也可能会为HW4在电动车上配置全新分辨率更高、帧率更高的摄影机和新款雷达等传感器,藉此有助自驾计算机更准确辨识物体,以及可创造更长的测距。但HW4计算机的芯片处理能力也必须升级到足以处理高分辨率、高帧率影像的程度,才能相辅相成。

Tesla HW3内建SoC内部配置,左下搭载两个NPU。Tesla

Tesla执行长Elon Musk曾指出,全自驾功能只适用于电动车,不适合在内燃机引擎汽车上。外媒分析,在为电动车开发自动驾驶解决方案上,能源效率可能就是安全性之下,另一最需重视的面向,其他芯片制造商或汽车制造商可能在这方面,都还未能达到Tesla自驾计算机开发的程度。

自建自驾硬件开发封闭体系也存有风险

但对Tesla来说,即使其FSD自驾计算机为全球自驾车产业发展树立新的标竿,但仅供自用的封闭式生态发展模式,即使带起全球自驾车发展浪潮,对自身技术扩大普及可能也没有太大帮助,却反而可能协助NVIDIA等自驾计算机竞争对手相对壮大。

Tesla同样自行研发HW3自驾计算机的SoC,但自驾技术不是只有硬件端,自驾AI算法、自驾安全模式等软件面的配合同样不可或缺。在全球AI技术仍不断变化及演进下,未来若自驾计算机和芯片在适应这些新AI算法的灵活性上不足,恐导致业者落后于全自驾技术开发浪潮中,这也是自制全自驾计算机和SoC的Tesla需注意的部分。

-

特斯拉

+关注

关注

66文章

6350浏览量

127067 -

英伟达

+关注

关注

22文章

3866浏览量

92320

原文标题:【解析】特斯拉HW3全自驾计算机:甩尾英伟达

文章出处:【微信号:DIGITIMES,微信公众号:DIGITIMES】欢迎添加关注!文章转载请注明出处。

发布评论请先 登录

相关推荐

特斯拉HW3全自驾计算机:甩尾英伟达

特斯拉HW3全自驾计算机:甩尾英伟达

评论