L6562A建模1

今天我们开始以L6562A为例来介绍如何使用Simpis对芯片进行行为级别建模。

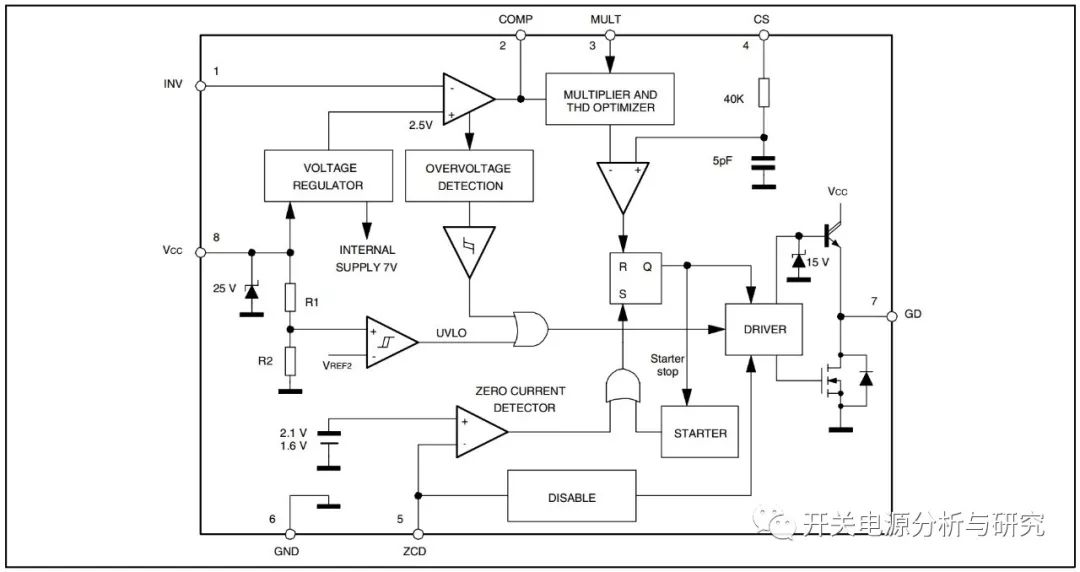

L6562A是一款基于BCM(临界导通模式)的PFC控制器。我们先看一下它的框图:

以及各个引脚的功能:

INV:电压反馈引脚,用于稳定输出电压;

COMP:误差比较器输出,需要加上补偿网络使电压环稳定,以及实现高功率因数和较低的THD;

MULT:内部乘法器的输入管脚,用来为内部电流环提供板正弦参考信号,实现PFC(使输出电流与电压同相位,都为半正弦形状);

CS:电流采样信号引脚,采集流过MOS管的电流信号,输入到内部比较器,与内部半正弦调制信号比较,产生PWM信号;

ZCD:生压电感去磁感应输入引脚,当检测到流过升压电感的电流下降到零时,会在内部产生一个下降沿信号信号触发驱动电路开启,打开开关,开始下一个周期;

GND:内部参考地信号;

GD:内部驱动信号,用于驱动外部MOS管;

Vcc:芯片供电引脚;

我们对照框图简单介绍一下它的工作原理:MULT引脚采样前端整流桥的输出电压信号(半正弦波形),该信号作为电流信号的调制整形参考信号。CS引脚一方面是采样电感电流信号,使用前述半正弦调制整形信号来调制电感电流信号包络。INV是电压环反馈引脚,配合COMP引脚的补偿电路实现稳定的电压环。ZCD引脚监测磁芯状态,用来开启下一个周期。

还是需要强调一点,我们建立的行为级别模型是基于数据手册规格参数表和原理描述以及我自己对于这个的理解,并不能表示真实的电路到底是如何实现的,每个人对于某一功能或参数的理解以及实现方法可能都不一样,所以大家不用纠结,只是给大家参考一下,大家有更好的想法可以告诉我。

我们从几个方面来讨论L6562A的建模,我们会分几次给大家介绍。

供电部分

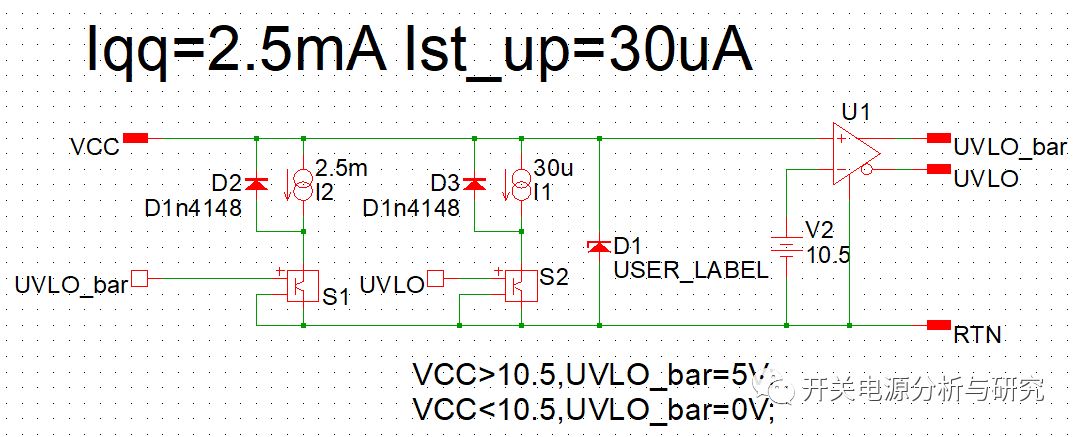

输入欠压检测电路:

当输入供电电压高于10.5V时,UVLO_bar信号输出为高,表明没有出现欠压现象,若输入供电电压低于10.5V时,UVLO为高电平,表明输入电压欠压;2.5mA表征启动后的静态电流;30uA表征未正常启动(欠压)下的静态电流;(参照规格书中的Istart_up和Iq)

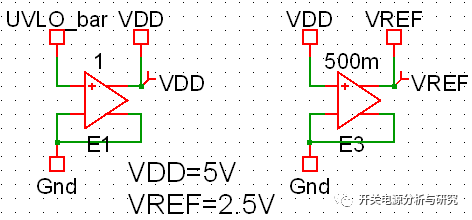

内部参考与供电信号:

VDD为内部电路供电,VREF是内部电压环参考电压;

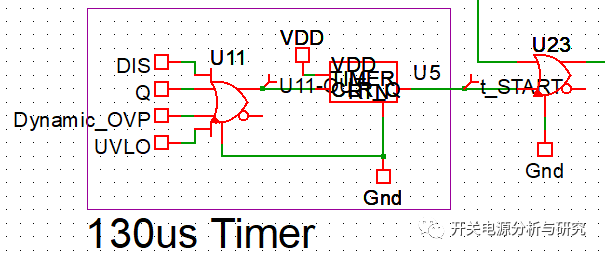

时钟电路

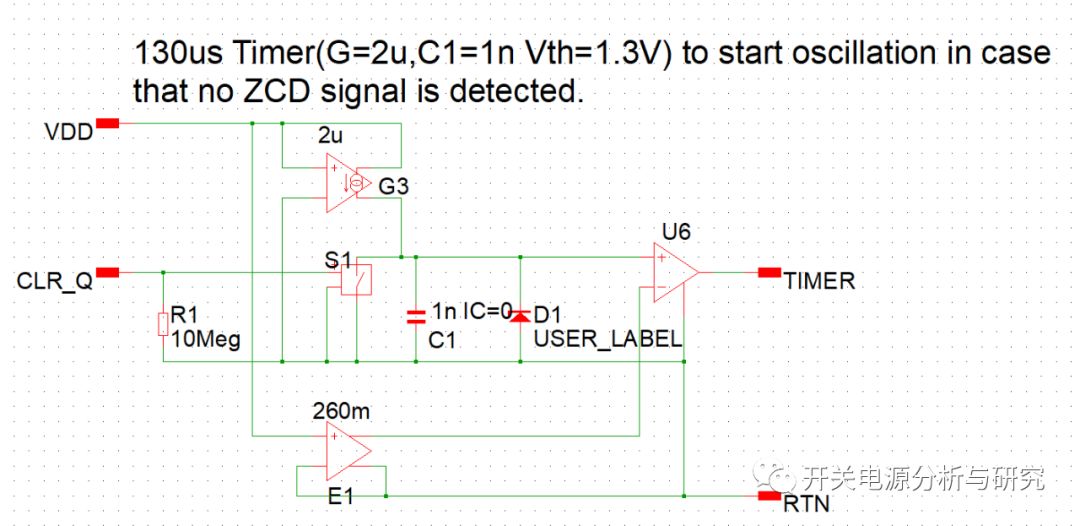

数据手册框图中画出了一个STARTER,它与ZCD引脚实现的ZERO CURRENT DETECTION电路输出的信号经过或的逻辑后输出到RS触发器的S端。这两个信号就是内部实现开关开启的触发信号。规格参数中的tSTART指定了内部一个固定时钟,其周期典型值为130us,其电路表示及其内部电路实现如下:

其实现原理非常简单,就是通过控制一个电流源对一个电容冲放电,当电容电压高于参考值时输出高电平,否则输出低电平。当然这个时钟一般只在系统刚启动时工作,待进入稳态后该时钟就不起作用了。U11的四个输入信号是用来给电容放电或关闭时钟的。待进入稳态后系统周期低于130us,当开关管开启时Q为高电平,该信号会释放C1电流,这样该时钟模块永远不会输出高电平,即关闭了该时钟模块。DIS, Dynamic_OVP, UVLO都是在出现错误状态下关闭该时钟的信号。

-

芯片

+关注

关注

456文章

50967浏览量

424891 -

控制器

+关注

关注

112文章

16403浏览量

178617 -

电压

+关注

关注

45文章

5617浏览量

115972

原文标题:浅谈芯片建模2

文章出处:【微信号:xiaojiaoyafpga,微信公众号:电子森林】欢迎添加关注!文章转载请注明出处。

发布评论请先 登录

相关推荐

ADuC7026微控制器在125°C下运行时不断重启、这是正常行为吗?

使用C2000 MCU对用于数字控制的双向降压/升压转换器进行建模

使用PSpice仿真器对TI智能高侧开关中的热行为进行建模

L6562A对芯片进行行为级别建模控制器

L6562A对芯片进行行为级别建模控制器

评论