在制程工艺上,Intel从2015年到现在一直在魔改14nm工艺,10nm工艺说是今年6月份量产了,但在时间进度上确实要比台积电等公司落后了,AMD今年都出7nm的CPU和显卡了。

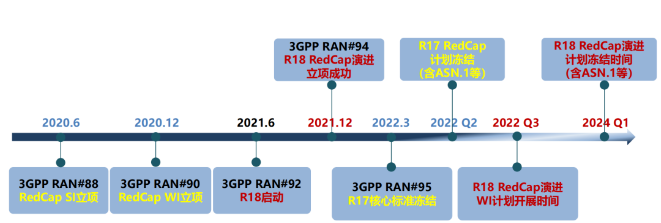

今年5月份的投资会议上,Intel宣布了新一代制程工艺路线图,14nm工艺(对标台积电10nm)会继续充实产能,10nm工艺(对标台积电7nm)消费级产品今年年底购物季上架,服务器端明年上半年。

再往后就是7nm了,Intel的7nm对标台积电5nm,预计会在2021年量产,不过首发产品是Xe架构的GPU加速卡,CPU的话估计要到到2022年了。

日前韩国媒体曝光了Intel的内部资料,详细介绍了7nm工艺以及处理器架构、傲腾、安全等方面的进展,如下所示:

在制程工艺方面,10nm首发平台是Ice Lake处理器,6月份出货,其他10nm工艺产品到2020及2021年推出,前面也说了消费级、服务器级的10nm处理器要等到2020年了。

7nm工艺计划2021年推出,相比10nm工艺晶体管密度翻倍,每瓦性能提升20%,设计复杂度降低了4倍。

这是Intel首次公布7nm工艺的具体细节,晶体管密度翻倍没有什么意外,正常都应该是这样,不过每瓦性能提升20%,这个数据要比预期更低,也只能说明在10nm之后,Intel的先进工艺在性能提升也遇到瓶颈了。

还有Intel没有提及能耗的具体信息,作为对比的是,Intel之前表示10nm工艺相比14nm降低了60%的能耗或者提升25%的性能。

此外,7nm工艺还是Intel首次使用EUV光刻工艺,有助于提升工艺微缩。

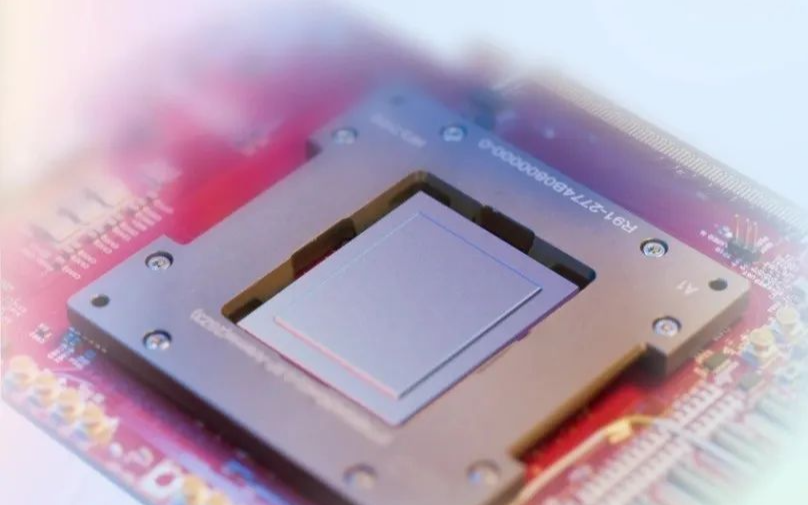

7nm工艺的首款产品就是Xe架构的GPU加速芯片,主要应用于数据中心AI及高性能计算。

处理器架构方面,现在的服务器端是14nm Cascade Lake,主要是增加了DL Boost指令集加速AI性能。

桌面级还有酷睿i9-9900KS,全核5GHz的9900K加强版了。

Ice Lake,这是10nm工艺Sunny Cove核心的全新产品,3x倍无线速度、2倍视频转码速度、2倍图形性能、3倍AI性能这些也是之前说过的了。

Ice Lake的核显架构升级到Gen11,32位浮点性能达到1TFLOPS以上,EU单元至少64个。

存储芯片方面,Intel今年上半年已经推出了傲腾H10,整合了傲腾内存及QLC闪存,9月份还有傲腾M10及M15新品,这是新一代傲腾内存,不过具体规格不详。

安全性方面,Ice Lake处理器主要增加了GFNI、SGX、PCFONFIG等指令,Ice Lake下一代的Tiger Lake会支持CET增强指令,Atom处理器中的下代Tremont架构也会增加SGX、GFNI等指令集。

-

intel

+关注

关注

19文章

3483浏览量

186183

发布评论请先 登录

相关推荐

7纳米工艺面临的各种挑战与解决方案

台积电分享 2nm 工艺深入细节:功耗降低 35% 或性能提升15%!

时间复杂度为 O(n^2) 的排序算法

4nm!小米 SoC芯片曝光!

CISC(复杂指令集)与RISC(精简指令集)的区别

PCB与PCBA工艺复杂度的量化评估与应用初探!

台积电升级4nm N4C工艺,优化能效与降低成本

龙芯:自主研发CPU提升性能,单核通用性能提高20倍

Intel超低功耗新U失去超线程!但多核性能可提升几乎1.5倍!

Intel7nm工艺进程曝光 每瓦性能提升20%设计复杂度降低4倍

Intel7nm工艺进程曝光 每瓦性能提升20%设计复杂度降低4倍

评论