最近在一个婚礼招待会上,我试图和一个和我坐在同一张桌子上的绅士交谈。不幸的是,有一个女人坐在我们之间,与坐在我身边的其他人进行对话。随着接收的所有骚动在背景中,谈话很难开始。在我们之间进行另一次讨论虽然使我们的谈话变得不可能。我们所拥有的是串扰!

对话过程中的串扰可能非常烦人,但PCB布局上的串扰可能是灾难性的。如果不纠正,串扰可能会导致您的成品板完全无法工作,或者可能会受到间歇性问题的困扰。让我们来看看串扰是什么以及如何减少PCB设计中的串扰。

如何减少PCB设计中的串扰?

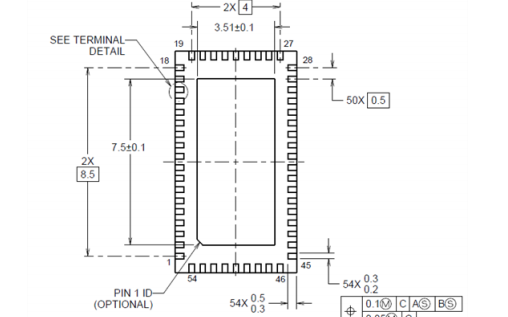

串扰是无意的印刷电路板上迹线之间的电磁耦合。这种耦合可能导致一条迹线的信号脉冲超过另一条迹线的信号完整性,即使它们没有物理接触。当平行迹线之间的间距很紧时,就会发生这种情况。即使迹线可能为了制造目的而保持最小间距,但对于电磁目的而言可能还不够。

考虑两条彼此平行的迹线。如果一条迹线中的差分信号具有比另一条迹线更大的幅度,则它可以积极地影响另一条迹线。然后,“受害者”轨迹中的信号将开始模仿侵略者轨迹的特征,而不是传导自己的信号。当发生这种情况时,就会产生串扰。

串扰通常被认为是在同一层上彼此相邻的两条平行轨迹之间发生的。但是,在相邻层上彼此相邻的两条平行迹线之间发生串扰的可能性更大。这被称为宽边耦合,并且更可能发生,因为两个相邻的信号层被非常少量的芯厚度分开。该厚度可以是4密耳(0.1毫米),有时小于同一层上两条迹线之间的间距。

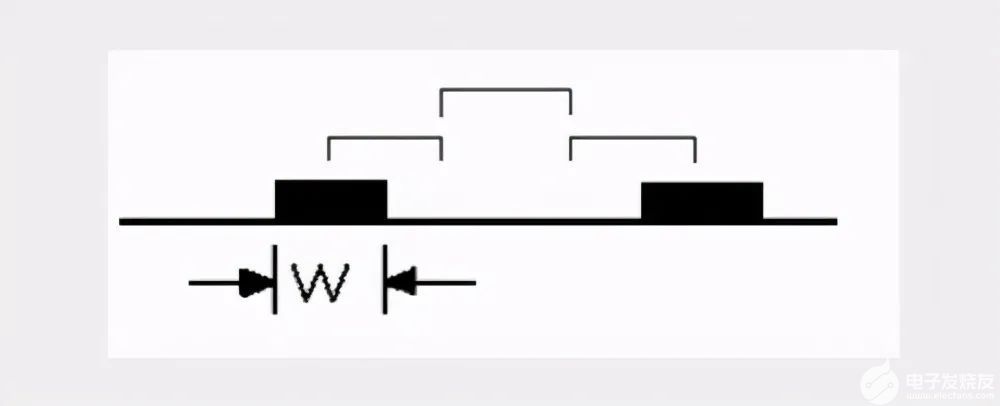

< p> 消除串扰的走线间距通常大于常规走线间距要求

消除设计中串扰的可能性

幸运的是,你不受相声的摆布。通过设计电路板以最大限度地减少串扰情况,您可以避免这些问题。以下是一些设计技术,可帮助您消除电路板上串扰的可能性:

在差分对和其他信号路由之间保持尽可能大的距离。经验法则是间隙=迹线宽度的3倍。

在时钟路由和其他信号路由之间保持尽可能大的差异。相同的间隙=迹线宽度经验法则的3倍也适用于此。

在不同的差分对之间保持尽可能大的距离。这里的经验法则略大,间隙=走线宽度的5倍。

异步信号(如RESET,INTERRUPT等)应远离总线并高速度信号。它们可以在接通或断开或上电信号旁边布线,因为在电路板的正常操作期间很少使用这些信号。

确保相邻的两个信号层在电路板堆叠中彼此交替将交替水平和垂直布线方向。这将减少宽边耦合的可能性,因为不允许迹线在彼此之上平行延伸。

减少两个相邻信号层之间潜在串扰的更好方法是在微带配置中将层与它们之间的接地平面层分开。地平面不仅会增加两个信号层之间的距离,还会为信号层提供所需的返回路径。

您的PCB设计工具和第三方应用程序可以帮助您消除串扰

如何您的设计软件可帮助您消除高速PCB设计中的串扰

PCB设计工具内置了许多功能,可帮助您避免设计中的串扰。通过指定布线方向和创建微带叠层,电路板层规则将帮助您避免宽边耦合。使用网络类规则,您将能够为更容易受串扰影响的网络组分配更大的跟踪间距。差分对路由器将差分对路由为实际对,而不是单独路由它们。这将保持差分对迹线彼此之间以及与其他网络之间所需的间距,以避免串扰。

除了PCB设计软件的内置功能外,还有其他工具这可以帮助您消除高速PCB设计中的串扰。有不同的串扰计算器可帮助您确定路由的正确走线宽度和间距。还有信号完整性模拟器来分析您的设计是否存在潜在的串扰问题。

如果允许发生,串扰可能是印刷电路板上的一个大问题。既然您知道要寻找什么,那么您将准备好防止串扰发生。我们在此讨论的设计技巧以及PCB设计软件的功能将帮助您创建无串扰设计。

-

pcb

+关注

关注

4332文章

23205浏览量

401167 -

电路设计

+关注

关注

6679文章

2470浏览量

205949 -

封装

+关注

关注

127文章

8081浏览量

143659 -

华强pcb线路板打样

+关注

关注

5文章

14629浏览量

43285

发布评论请先 登录

相关推荐

什么是小间距QFN封装PCB设计串扰抑制?

解决PCB设计消除串扰的办法

PCB设计中QFN封装的串扰抑制分析

高速PCB设计中如何消除串扰?

高速PCB设计中如何消除串扰?

评论