当夏天结束时,我聚集了我的家人,前往州博览会,感受神奇的兴奋。在这一年中,展览会场地空无一人,小小的尘埃滚过贫瘠的景观。但是,当博览会开幕时,展览场地充满活力。有大象耳朵的摊位,有动物和示威的建筑物,还有带尖叫孩子的游乐设施。这是一个充满活力的杂耍行为。

将印刷电路板与高速信号放在一起,包括设计,组件和高速信号的杂耍行为。这些高速信号为不必要的传输线创造了机会,从而对电路板造成严重破坏。大部分混乱都发生在PCB布局本身内。

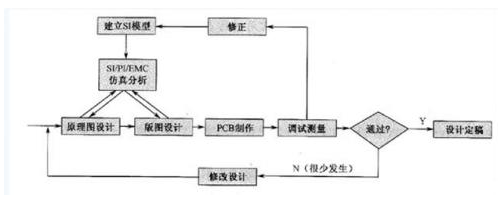

了解布局造成的这种破坏可以在铺设电路板时实现分辨率。了解您所应用的布局技术是否是PCB设计中信号完整性分析的最佳实践。可以通过执行冗长的铅笔分析或使用信号完整性模拟工具来发现它。阅读完之后,我会让你决定你认为对你的电路板更有效。

信号完整性模拟工具不足

信号完整性模拟工具,魔术变得混乱。阻抗计算器返回错误的阻抗计算。计算与PCB设计规则中定义的材料的层叠和介电常数相矛盾。模拟器假设建模的返回路径,因此如果地平面中存在不连续性,则它们不包括在计算中。 3D场解算器返回非常错误的差分对的计算阻抗。

该工具很简单,不支持PCB布局的常规选项,同时牢记设计规则。这包括刚性弯曲的规则和模拟。其仿真环境产生难以理解的波形。进一步研究需要复杂的手动命令来评估普通操作。对于其3D场解算器也是如此。由于用户界面没有选择来分析电气长迹线,因此在布置电路板以实现高速信号完整性时没有信心。

使用智能EDA工具优雅地使用脑力

解释结果的时间间隔

< p>花费数小时来分析模拟工具结果以分析炫目错误。浏览菜单需要细致的工作。时间沉没穿过阻抗计算器,揭示了使用不正确的参数来计算走线阻抗。花时间发现模拟器使用的参数与PCB布局的净规则不匹配。谁会猜到?

如果平面材料的固有电容和介电常数没有正确的参数,那么计算出的阻抗确实会减少高速信号的反射和振铃。

隐藏的环境异常(例如缺少钻取文件)会导致模拟器失败。鉴于设置模拟所需的大量PCB编辑器和设置,丢失钻孔文件会导致错误,导致设置过程混乱。它会导致对编辑器和设置菜单中选择的参数进行质询和重新质询。

通过帮助页面和应用程序说明进行搜索会导致在分析模拟高速信号以保证信号完整性的工具时浪费更多时间。最后,获得说明模拟结果的波形经常显示垃圾。如果没有优雅的用户界面可以在我的指尖上使用强大的工具来将它们正确地驱动到我的电路板上,这是令人沮丧的。在一天结束时,诚信仍然可以争夺。

识别和解决完整性的合格工具

如果工具中的阻抗计算器使用了PCB设计规则中设置的材料参数,那会不会很好?将工具端口信息存储在其总体设计规则中以计算阻抗,可以确保印刷电路板将从制造商处返回,并使用正确的组件和布局来补充电路设计。

使用模拟器使用参数从PCB设计规则中获得对结果的信心。在工程师和布局设计人员解决信号完整性问题和解决方案的那些日子里,获取波形显示在原理图捕获和PCB布局期间的仿真结果将有助于建设性地改进设计。它消除了进行分析的猜测,并从铅笔沉思中应用最佳实践,等待PCB制造,然后验证信号完整性。

AltiumDesigner®采用精确的波形分析

Altium Designer 18在PCB层堆栈管理器中有一个阻抗公式编辑器。通过下拉菜单可以在PCB布局环境中轻松访问层堆栈管理器。阻抗公式编辑器包含适用于所有拓扑的正确路由阻抗公式,包括嵌入式,双链路和差分网络的微带到带状线。在编辑器中可以轻松访问每个拓扑的默认公式。这允许直接访问每个拓扑的公式,以便在工具中轻松修改。作为替代方案,如果更方便,也可以通过查询助手访问和编辑阻抗公式。

通过层堆栈管理器轻松访问阻抗公式编辑器

一旦反射和振铃的阻抗已经融入PCB布局,信号完整性模拟器可以设置为高分析速度信号行为。模拟器接受设计者定义的信号刺激。 PCB设计器还包括高速信号网络的参数特性,如过冲和下冲值,飞行时间和电源网络限制。

模拟器使用这些值在波形分析窗口中显示结果。由此产生的波形显示了信号完整性问题,例如由于PCB布局或滤波分立特性而在高速线路上引起的振铃,反射,串扰或电压降。 PCB设计人员能够调整阻抗以实现最大信号完整性,并继续执行波形分析,直到设计无噪声。

Altium Designer 18是一种功能强大且易于使用的原理图捕获和PCB布局工作时允许阻抗设置为高速轨迹的工具。其统一的环境使其易于使用,使您能够在印刷电路板制造之前获得设计中信号完整性所需的结果。

如果您正在寻找包含易于使用的EDA工具用于设计PCB布局以实现最大信号完整性的工具,请与Altium专家交谈。

-

pcb

+关注

关注

4421文章

24024浏览量

427016 -

测试

+关注

关注

9文章

6496浏览量

131771 -

模拟信号

+关注

关注

8文章

1237浏览量

54848 -

华强pcb线路板打样

+关注

关注

5文章

14629浏览量

44760

发布评论请先 登录

高速PCB设计分析:如何进行模拟和信号完整性的检查?

高速PCB设计分析:如何进行模拟和信号完整性的检查?

评论