阻抗控制PCB

在高频应用中,信号不会因为它们在PCB中的路径而降级。

在PCB设计中通过叠层计算阻抗控制时需要注意的四个问题

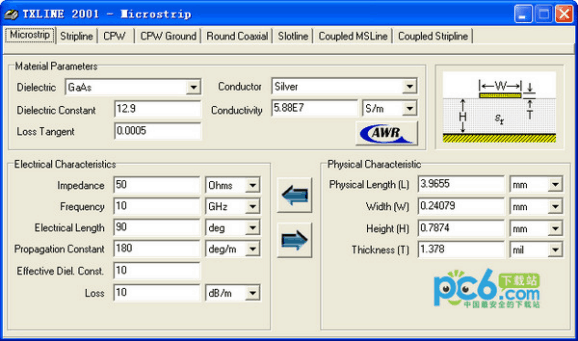

在高速PCB设计过程中,堆栈设计和阻抗计算是迈向顶端的第一步。阻抗计算方法非常成熟,不同软件的计算方法也没有差别。阻抗计算和过程之间的一些“权衡”相对麻烦。主要目的是实现我们的阻抗控制目的,同时也确保处理方便,并最大限度地降低处理成本。

下面我们总结一下设计时阻抗计算的一些注意事项PCB层叠起来可以帮助您提高计算效率。

线宽相当宽,不太好。

因为在这个过程中有一个很薄的限制,所以宽度没有限制,所以如果你为了调整阻抗调整的线宽而稍后达到极限,那么要增加它会很麻烦成本或放宽阻抗控制。因此,计算的相对宽度意味着目标阻抗略低,例如,单线阻抗为50欧姆。我们可以计算到49欧姆,并尽量不计算到51欧姆。

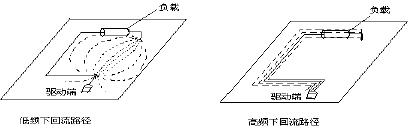

整体呈现趋势

整体呈现出一种趋势。在我们的设计中我们可能有多个阻抗控制目标,所以整体太大或太小,所以不要看起来类似于100欧姆太大,90欧姆太小而不能大而小。

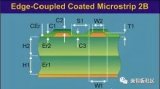

考虑残余铜率和胶水量

-

pcb

+关注

关注

4331文章

23197浏览量

400859 -

PCB设计

+关注

关注

394文章

4703浏览量

86634 -

可制造性设计

+关注

关注

10文章

2065浏览量

15746 -

华强pcb线路板打样

+关注

关注

5文章

14629浏览量

43246 -

华秋DFM

+关注

关注

20文章

3495浏览量

4811

发布评论请先 登录

相关推荐

PCB设计中通过叠层计算阻抗控制时需要注意的四个问题

PCB设计中通过叠层计算阻抗控制时需要注意的四个问题

评论