在半导体领域,“摩尔定律”可谓是无人不知、无人不晓。可以说在过去几十年,半导体产业在摩尔定律的推动下高速发展。但是现在,随着晶体管缩放尺寸逐渐逼近物理极限,半导体工艺制程的推进也越来越困难,“摩尔定律”已死的声音也开始不绝于耳。不过,即便如此,科学界也依然希望通过一些新的技术来继续推动摩尔定律的前进。

“摩尔定律”已死?

摩尔定律是由英特尔创始人之一的戈登·摩尔(Gordon Moore)于半个世纪前提出来的。其内容为,“当价格不变时,集成电路上可容纳的晶体管的数目,约每隔18-24个月便会增加一倍。”

自摩尔定律提出之后的几十年,整个半导体产业也确实按着摩尔定律在持续快速的前进,但是自28nm之后,摩尔定律便开始呈放缓态势,其所带来的经济效益也开始降低。

虽然去年上半年台积电的7nm工艺已经量产,而且5nm也已经在路上,接下来3nm甚至是1nm或许仍然还有路可以走,但是这毫无疑问将会更加的困难。

而更为令人悲观的是,虽然随着工艺的提升,晶体管密度还可以进一步增加,但是能够带来的性能提升或功耗的降低却越来越少。比如从28nm到16nm,面积缩小了40%,速度提高了30%-40%,但是如果选择提升速度,那么功耗就没法降低多少。而在28nm之前,每一代制程工艺的升级,功耗都能够降一半多,面积降一半多,速度提升一倍多。但现在,这样的好事情已经一去不复返了。

除此之外,随着工艺制程从10nm向7nm、5nm、3nm、1nm的继续演进,所需要付出的代价也更具高昂。摩尔定律所带来的经济效益(即在价格不变的情况下,每两年性能提升一倍甚至更多)也将会不复存在。

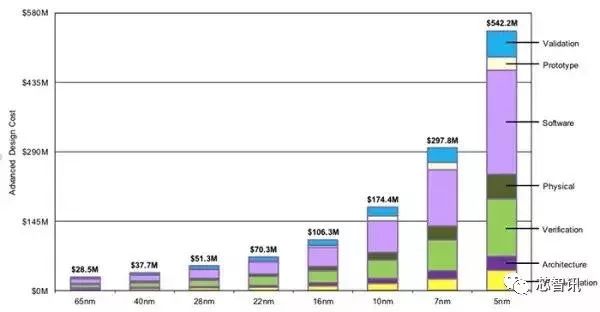

此前,国外Semiengingeering网站曾发布过一篇工艺和芯片开发费用的文章。文中指出28nm节点的芯片开发成本为5130万美元;16nm节点则需要1亿美元;7nm节点需要2.97亿美元;5nm节点,开发芯片的费用将达到5.42亿美元;由于3nm还处于最初期的开发阶段,所以其开发成本至今还难以确定,3nm的开发费用有可能超过10亿美元。

此外,先进的晶圆厂建设同样需要大量的现金支持,以采用最新的设备来提升工艺制程,这将进一步拉高芯片的制造成本。比如7nm之后的5nm就必须要用到最新的EUV极紫外光刻技术,而目前全世界仅有ASML可以供应EUV***,而且一台EUV***的售价就高达1亿多美元。

显然,随着制程工艺的不断逼近物理极限,不仅在技术实现上越来越困难,所需要的设备越来越复杂,而且芯片开发成本也急剧增长,如果芯片厂商没有足够的实力,芯片出货没有足够的出货量,将很难承担高昂的成本。

全新的“自组装”技术

在“摩尔定律”的推进越来越困难,甚至“摩尔定律”已死声音越来越多的当下,包括英特尔在内的众多半导体企业也纷纷寄希望于通过“内核架构创新”(比如采用非冯·诺伊曼系统架构)、芯片工艺由原来的2D转向2.5D/3D堆叠、自旋电子、神经元计算、量子计算等方法来继续推进“摩尔定律”的经济效益。

对于以上的这些新技术可能大家或多或少都有了解和接触过,而在去年在德国举办的TED演讲当中,来自美国的研究人员Karl Skjonnemand为延续“摩尔定律”提出了一种全新的思路,即利用“分子工程和模拟自然的方法”来实现晶体管的“自组装”(self-directed assembly),从而极大的降低半导体制造的成本。

▲根据资料显示Karl Skjonnemand目前是美国的一家专注于未来的芯片制造开发所需先进的纳米材料公司的技术总监,他拥有20年亚太、欧洲和美国项目管理经验。

而在介绍“晶体管自组装”技术之前,我们有必要先来了解下,传统的半导体制造工艺流程。

那么相对于传统的半导体制造工艺,所谓的晶体管的“自组装”技术又有何优势呢?

Karl Skjonnemand认为,在传统的芯片当中,晶体管的微型结构特征有非常多都是重复的,是一种高度周期性的结构。因此,他想在替代技术中利用这种周期性,他想采用自组装材料,自然的组建周期性结构,来构建晶体管,让这些材料来完成精图案的制作,而不是试图在已经越来越困难的图案投射技术上突破。

自组装原理在大自然中随处可见,比如我们的脂质膜到细胞结构,再到DNA能够复制,并且一代代的遗传下去,就是一种自然组装技术。因此,Karl Skjonnemand认为,自组装技术可以应用到芯片制造当中。

他介绍了一种名为“嵌段共聚物”(block copolymer)的自组装材料(一种有机半导体)——由两条长度只有几十纳米的聚合物链条,但是这些聚合物链彼此排斥。可以将它们强制组合在一起,在系统中创造一种“嵌入式窘组”。而一块不大的材料,可包含几十亿这样的聚合物链,相似的化合物粘结在一起,同时互斥的化合物则会相互分离。这些化合物四处移动,直到变成一个特定的形状。

Karl Skjonnemand表示,天然的自组装形状是纳米级的,有规律和周期性,还很长,这就是我们在晶体管排列中所需要的,重要的是,它们能够提供比传统晶体管蚀刻更为精细的细节。

所以我们可以利用分子工程来设计不同的尺寸和不同的形状,以及不同周期性的不同形状,比如说,我们选择一种对称分子,他的两条聚合物链长度相似,则自然的自组装结构就是长的曲线形,像指纹一样,指纹线的宽度和间距,不仅取决于聚合物链的长度,还取决于系统内部窘组的级别。

我们还可以创造更复杂的结构,如果我们使用非对称分子,其中一条聚合物链显著短于另外一条。在这种情况下,短链就会在中间形成一个牢固的球,被包裹在更长的相互排斥的聚合物链当中,形成一个自然的圆柱体。这个圆柱体的尺寸,及圆柱体之间的距离和周期性,取决于我们选择的聚合物链的长度以及内嵌窘组的水平。

换句话说,利用分子工程,可以获得自组装的纳米结构。这些结构可以是线形的,圆柱形的,同时也符合我们设计的周期性。我们利用化学工程来制造晶体管所需的纳米级特征,但是具备了自组装这些结构的能力,只解决的一半的问题,因为还需要排列这些结构,使得晶体管可以形成电路。

对于这个问题,Karl Skjonnemand表示,可以使用宽导向结构来固定自组装结构。将他们锚定到位,使得剩余的自组装结构可以平行排列,从而与我们的导向结构保持一致。比如我们想做一个精细的40nm长的线形,对于传统的投射技术是非常困难的。我们可以先制作一个120nm的导向结构,使用普通的投射技术,这个结构将会把3个40nm长的线形排列在一起。使得这些材料可以自动的进行最复杂的精细复写。

不过,这其中依然有着其他的挑战,比如,整个系统都需要完美的排列。因为结构中任何微小的缺陷都会导致晶体管的失效。所以需要利用化学清洗的方法来消除纳米级别的最小失误。

“自组装”何时能走向商用?

其实,在Karl Skjonnemand之前,已经有很多的科研机构尝试将自组装技术应用于半导体芯片制造,并且近几年也取得了一些突破。

早在2012年,比利时的微电子研究中心(IMEC)就在自己的工厂里安装了世界上的首个自组装生产线。在那里,科学家改进材料和设计,减少自组装结构的误差。

此外,纽约州立大学也在阿尔巴尼(Albany)的纳米尺度工程中心(Center for Nanoscale Engineering)里运营着一条自组装的生产线。

在2014年的Semicon West半导体行业会议上,IMEC的流程技术研发副总裁安·斯特更(An Steegen)就曾表示,自组装技术看起来可以作为极紫外光刻法的替代方法,延长现有光刻法的寿命。IMEC现在可以用自组装技术设计出和英特尔最新的芯片相似的结构,尺度可小至14纳米。斯特更当时表示,自组装技术有望替代EUV技术。

纽约州立大学纳米尺度工程中心纳米工程副教授克里斯托弗·波斯特(Christopher Borst)在Semicon Westl论坛上也曾表示,其生产线现在可以可靠地产生重复的线条和鳍状结构,可以精细到18nm。“我们制造了一些让人印象深刻的结构,”波斯特说。“这种方法在材料和制造能力上已经没问题了。”

2016年初,美国国家标准与技术研究所(NIST)与IBM的研究人员开发了一种沟槽(trenching)技术,能被用以通过定向自组装来打造半导体芯片。显然,这种沟槽技术与前面Karl Skjonnemand介绍的用于打造自组装半导体芯片所需的“导向结构”作用类似。

在2017年,来自麻省理工学院和芝加哥大学的一群研究人员就宣布声称已经找到了一种方法,可以开发出更窄的线宽,并可望能应用在标准的大规模经济型生产设备中,而这种方法就是利用了“自组装”技术。

麻省理工学院的副教务长兼化学工程教授Karen Gleason表示,现在,先进的芯片工艺通常需要非常昂贵的极紫外光(EUV)光学技术,或是通过扫描芯片表面的电子束或离子束建立逐行扫描影像,这些方法都过于缓慢且昂贵。

麻省理工学院的研究人员提出的方案是,首先使用目前已被大量采用的光刻技术,用于在芯片表面上产生线路图案。而后使用“嵌段共聚物”的材料层,会自然地分离到交替的层或是其他通过旋涂溶液形成的可预测图案。嵌段共聚物是由两种不同高分子聚合物形成的链状分子。

“两个嵌段的尺寸可确定在沉积时将自行组装的周期层尺寸或其他图案。而后一个保护性的聚合物层会被放置在嵌段聚合物上,通过化学气相沉积(chemical vapor deposition,CVD)的方式完成这一过程。这个过程是一大关键,它对嵌段聚合物的自组装造成约束,迫使其形成垂直层而非水平层,底层的光刻图案将引导这些层的定位,但共聚物会自然地导致其宽度要比基线的宽度更小。同时由于顶部聚合物层还能图案化,因而该系统可用于建立更加复杂的图案,如微芯片的互连。”

麻省理工研究人员表示,目前大多数芯片都使用现有的光刻技术,CVD本身很容易理解,因此实施新技术会更加简单。不需要改动设备,使用的也都是熟悉的材料。

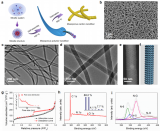

而在2018年,香港中文大学化学系缪谦教授研究团队发明了具有独特自组装结构的有机半导体材料,设计合成了带有不同功能基团的六苯并苝衍生物,并在其晶体结构中发现了一种罕见的分子堆积方式。这些六苯并苝衍生物具有扭曲的共轭骨架,在晶体中形成独特的砖砌结构,保持基本相同的二维π-π堆积模式而不受各种功能基团的影响。同时,缪谦教授研究团队还在此基础上结合有机薄膜晶体管与微流管道成功制备了高选择性、高灵敏度的化学和生物传感器。

▲六苯并苝衍生物的堆积模式

通过上图,我们可以看到该有机半导体的堆积模式具有高度一致的周期性结构,而每个结构的长宽均不到2nm。

当然,从目前来看,利用“自组装”技术来打造半导体芯片仍处于实验室或者试验生产阶段,要想走向大规模商用还需要解决一些问题,比如前面Karl Skjonnemand提到的需要解决“结构中任何微小的缺陷”,此外,还需要有一套对应的开发工具来便于芯片设计公司利用自组装技术和材料来进行开发。

不过,相对于传统的半导体制程技术来说,“自组装”技术确实将有助于继续推动芯片制造工艺的提升,同时极大的降低先进芯片制造的成本。

“通过自组装材料,继续扩展计算和数字革命。这可能是分子制造新时代的曙光。”KarlSkjonnemand说到。

-

芯片

+关注

关注

455文章

50697浏览量

423042 -

摩尔定律

+关注

关注

4文章

634浏览量

78988

原文标题:芯片制造行业的新方向:“自组装”技术解析

文章出处:【微信号:icsmart,微信公众号:芯智讯】欢迎添加关注!文章转载请注明出处。

发布评论请先 登录

相关推荐

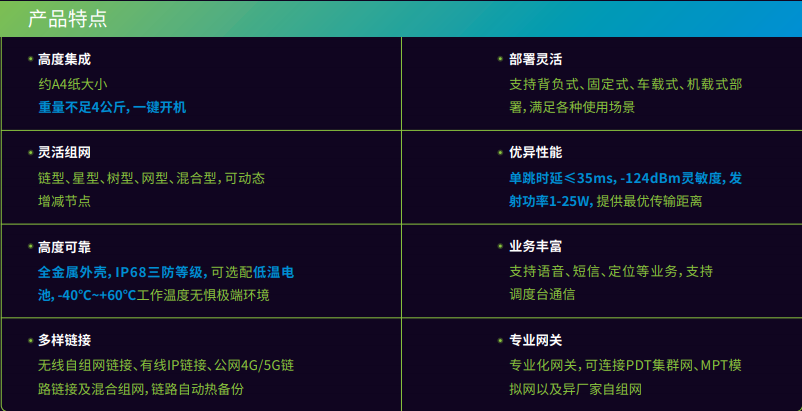

sMesh宽带图像自组网系统

SmartLink窄带语音自组网系统

芯片“自组装”何时能走向商用?

芯片“自组装”何时能走向商用?

评论