Chiplet与先进封装设计中EDA工具面临的挑战

Chiplet和先进封装通常是互为补充的。Chiplet技术使得复杂芯片可以通过多个相对较小的模块来实现,而先进封装则提供了一种高效的方式来将这些模块集成到一个封装中。

- 专栏巨霖

- 9小时前

- 131

- 0

- 0

Broadcom使用Cadence Spectre FMC Analysis进行时序变化分析

对于最新的微型半导体制作工艺而言,制程工艺变化和器件不匹配带来了深远影响。复杂制程工艺也会影响器件生产的可变性,进而影响整体良品率。 蒙特卡洛(MC)仿真使用重复的随机抽样方法,将工艺变化与电路性能和功能联系起来,从而确定它们对良品率的影响。然而,要进行全面的设计空间研究,设计团队需要完成大量的 MC 仿真才能达到必要的可信度。

- 专栏Cadence楷登

- 2天前

- 734

- 0

- 0

Cadence解决方案助力高性能传感器封装设计

在技术和连通性主宰一切的时代,电子和机械设计的融合将彻底改变用户体验。独立开发器件的时代已经过去;市场对创新、互联产品的需求推动了业内对协作方法的需求。

- 专栏Cadence楷登

- 2天前

- 548

- 0

- 0

华大九天版图寄生参数分析工具Empyrean ADA介绍

在集成电路设计中,寄生参数是决定芯片性能的关键因素之一,尤其是在先进工艺节点下,其影响愈发显著,甚至可能成为影响芯片成败的决定性因素。

- 专栏华大九天

- 2天前

- 177

- 0

- 0

华大九天牵头制定车规级EDA团体标准

近日,中国电子工业标准化技术协会正式发布两项团体标准——《车规级泛模拟集成电路电子设计自动化工具技术要求》(T/CESA 1384-2025)和《车规级平板显示电路电子设计自动化工具技术要求》(T/CESA 1385-2025)。这两项标准由华大九天牵头,联合行业多家单位共同制定,旨在为车规级EDA的开发和应用提供技术规范,填补国内相关领域标准空白,加速中国新能源汽车产业高质量发展。

- 专栏华大九天

- 2天前

- 642

- 0

- 0

芯华章以AI+EDA重塑芯片验证效率

近日,作为国内领先的系统级验证EDA解决方案提供商,芯华章分别携手飞腾信息技术、中兴微电子在IC设计验证领域最具影响力的会议DVCon China进行联合演讲,针对各个场景下验证中的“硬骨头”问题,用实际案例诠释“AI+EDA”如何重塑验证效率,让大家实实在在的看见国产验证EDA技术落地的扎实与生态协同创新的力量。

- 专栏芯华章科技

- 3天前

- 227

- 0

- 0

EDA²与华大九天达成战略合作

为加速多元EDA生态发展,推动产业协同创新,EDA²与华大九天正式达成战略合作,双方将携手共建“汉擎天地社区”,通过资源整合与技术互补,打造开放、共享、高效的多元EDA模拟工具生态平台,推动集成电路设计产业多元化发展。

- 专栏华大九天

- 3天前

- 162

- 0

- 0

概伦电子以AI技术驱动EDA革新

2025年4月15日,概伦电子受邀出席慕尼黑上海电子展“2025 AI技术创新论坛”。公司副总裁马玉涛博士发表《AI时代模拟与定制电路设计的挑战与机遇》开幕演讲,系统阐释AI技术在电子设计自动化(EDA)领域的创新实践与产业突破。

- 专栏概伦电子Primarius

- 5天前

- 296

- 0

- 0

概伦电子集成电路工艺与设计验证评估平台ME-Pro介绍

ME-Pro是概伦电子自主研发的用于联动集成电路工艺与设计的创新性验证评估平台,为集成电路设计、CAD、工艺开发、SPICE模型和PDK专业从业人员提供了一个共用平台。

- 专栏概伦电子Primarius

- 5天前

- 488

- 0

- 0

基于1.35M Instance设计的GPU加速实例

CPU是计算机的核心部件,由运算器、控制器、寄存器组和内部总线等部分组成。常见的x86架构CPU核心数相对较少,一般在8 - 32核左右,主要是为了解决复杂的逻辑运算和顺序执行指令的任务。它在处理单线程任务时效率很高,能够快速执行复杂的指令集,例如进行数学计算、程序的流程控制等操作。

- 专栏芯行纪

- 6天前

- 203

- 0

- 0

概伦电子大手笔并购锐成芯微100%股权及纳能微45.64%股权 EDA+IP深度协同

概伦电子加码半导体核心技术布局;4月11日晚间,国内EDA(电子设计自动化)龙头企业概伦电子(688206.SH)发布重磅公告,上海概伦电子股份有限公司拟通过发行股份及支付现金的方式购买成都锐成芯微科技股份有限公司(以下简称“锐成芯微”)100%股权及纳能微电子(成都)股份有限公司(以下简称“纳能微”)45.64%股权,并募集配套资金(以下简称“本次交易”)。锐成芯微共持有纳能微54.36%的股权,在取得锐成芯微100%股权及纳能微45.64%股权后,纳

- 专栏A面面观

- 7天前

- 527

- 0

- 0

Arm架构将占据半数 2025年出货到头部云服务提供商的算力

Neoverse 技术的部署已达到了新的高度:2025 年出货到头部超大规模云服务提供商的算力中,将有近 50% 是基于 Arm 架构。

- 专栏Arm社区

- 12天前

- 445

- 0

- 0

RISC V 开源芯片项目:PULP(Parallel Ultra Low Power)平台深度解读

一、项目背景与核心目标 PULP(Parallel Ultra Low Power)是由瑞士苏黎世联邦理工学院(ETH Zurich)和意大利博洛尼亚大学(University of Bologna)于2013年联合发起的开源多核计算平台。其核心目标是为 物联网(IoT)终端节点 和 边缘计算设备 提供 低功耗、高性能 的嵌入式解决方案。通过硬件与软件的协同优化,PULP在毫瓦级功耗下实现高效并行计算,满足传感器数据流处理、实时信号处理等需求。 *附件:pulp-master.zip 二、技术架构解析 1. 硬件设计 核心处理器

- 专栏eeDesigner

- 12天前

- 753

- 0

- 0

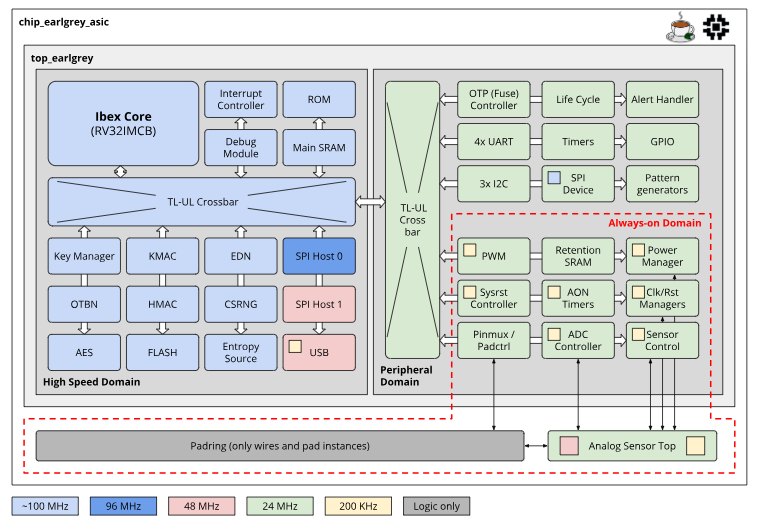

RISC V 开源芯片项目:OpenTitan 详细解读

OpenTitan 是由 Google 主导的开源安全芯片项目,旨在为硬件系统提供 可信的硬件信任根(Root of Trust, RoT) ,通过透明化设计和开源协作提升硬件安全水平。以下是其核心解读: *附件:OpenTitan Earl Grey (Discrete Chip) Datasheet.pdf 一、技术定位与核心特性 开源硬件信任根 OpenTitan 的核心理念是通过开源设计实现硬件安全的透明化。其代码、文档和验证流程均开放,允许开发者审查和贡献,减少对专有设计的依赖。这种透明性被认为是抵御硬件攻击的关键,例

- 专栏eeDesigner

- 12天前

- 529

- 0

- 0

原华秋 KiCad 发行版 9.0.1 发布

“ 华秋发行版的定位是为中国用户服务,解决一些因某种原因无法合并到主干但对中国用户来说非常重要的问题;同时通过预装一些插件,打通供应链、设计到制造的壁垒。9.0.1 版本现已发布. ” 为什么需要华秋发行版? 华秋电子在去年11月的 KiCon 发布了基于 8.0.6 的首个发行版: 发布后得到了很多小伙伴的积极反馈,但还是会有一些疑问,最主要的问题有两个:“发行版和官方KiCad有什么不同?为什么要做发行版?”,“又一个自主可控?”

- 专栏KiCad

- 16天前

- 206

- 0

- 0

IC设计企业芯弦半导体完成Pre-A+轮近亿元融资 新增三一重工旗下创投企业等股东

据企查查企业数据显示;专注于“汽车与能源”电控专用“嵌入式处理器和特色模拟IC”的高新集成电路设计企业芯弦半导体(苏州)有限公司发生工商变更,新增三一重工旗下无锡三一创业投资合伙企业(有限合伙)、苏州工业园区元禾重元叁号股权投资合伙企业(有限合伙)、广州海汇科创创业投资合伙企业(有限合伙)等新股东。此外;芯弦半导体的注册资本由约439万人民币增至约522万人民币。 据悉;芯弦半导体拥有四大产品线,涵盖车规级MCU,

- 专栏A面面观

- 19天前

- 531

- 0

- 0

广立微SEMICON China 2025圆满落幕

近日,为期三天的半导体盛会——SEMICON China 2025在上海新国际博览中心圆满落幕。广立微全面展示了其在EDA软件、测试设备及良率提升的综合创新能力,赢得了业内的高度关注与赞誉。

- 专栏广立微Semitronix

- 20天前

- 432

- 0

- 0

Andes晶心科技携手proteanTecs,为RISC-V内核带来性能和可靠性监测

2025年4月1日 — RISC-V处理器核的领先供货商Andes晶心科技 (Andes Technology Corporation) (TWSE: 6533) 与先进电子产品健康和性能监测解决方案全球领导者 proteanTecs 于今日宣布建立战略合作伙伴关系。达成此次合作后,两家公司的共同客户能够将 proteanTecs 的单晶片监测 IP 无缝集成至Andes晶心科技的 RISC-V 处理器。客户可以利用 proteanTecs 的实时分析软件应用来优化效能、降低功耗、检测故障,并在生产过程和整个运营生命周期中提升系统的整体可靠性。 Andes晶心科技

- 专栏AndesTech

- 20天前

- 371

- 0

- 0

AI驱动半导体与系统设计 Cadence开启设计智能化新时代

近日,楷登电子(Cadence)亚太区资深技术总监张永专先生受邀于上海参加了 SEMICON CHINA 2025,并发表了题为《AI 驱动半导体与系统设计》的演讲。他从 EDA 企业视角出发,深入剖析 AI 为行业带来的机遇与挑战,分享 Cadence 运用 AI 技术在半导体与系统设计领域的创新应用成果并展示 Cadence 推动行业前沿创新的思路与实践。 EDA 的 AI 机遇:技术融合催生变革 在 AI 驱动的时代浪潮下,各行业积极探索如何借助 AI 释放创造力、提升生产力。得益于摩尔定律,

- 专栏Cadence楷登

- 21天前

- 595

- 0

- 0