国产FPGA公司高云半导体荣获 “年度汽车产业链突破奖”,引领车规芯片发展

4月25日-26日,由《中国汽车报》有限公司、上海车展管理有限公司、汽车电子产业投资联盟联合主办,爱集微咨询(厦门)有限公司协办的“2025汽车半导体生态大会暨中国车规芯片技术路演”在国家会展中心(上海)圆满举行。广东高云半导体科技股份有限公司(简称“高云半导体”)受邀出席本次大会,并凭借在汽车电子领域的卓越表现,荣获了由汽车电子产业投资联盟、《中国汽车报》和爱集微联合评定的"年度汽车产业链突破奖(2024-2025)"。 "年

- 专栏高云半导体

- 6天前

- 190

- 0

- 0

FPGA的Jtag接口烧了,怎么办?

在展开今天的文章前,先来讨论一个问题:FPGA的jtag接口烧了怎么办?JTAG接口的输入引脚通常设计为高阻抗,这使得它们对静电电荷积累非常敏感,由于JTAG接口需要频繁连接调试器、下载线缆等外部设备,插拔过程中极易因摩擦产生静电。JTAG接口经常会有带电拔插的情况,这不可避免地会产生静电或浪涌电流。JTAG接口的引脚直接与FPGA内部的测试访问端口(TAP

- 企业小眼睛科技

- 6天前

- 190

- 0

- 0

原Cadence收购Arm基础IP业务,谁是赢家?

电子发烧友网报道(文/梁浩斌)最近EDA公司密集收购半导体IP公司,就在上周国内EDA厂商概伦电子宣布收购锐成芯微100%股权和纳能微45.64%股权之后,4月16日,国际EDA巨头Cadence在官网上发文宣布与Arm达成最终协议,收购Arm的Artisan foundation IP业务,包括标准单元库、嵌入式内存和GPIOs等产品。 一直以来,EDA企业都通过积极的并购和与半导体IP协同的模式进行扩张,并购IP公司是EDA整合产业链、提升技术壁垒、应对市场挑战的关键策略。 Artisan 业务状况

- 专栏Hobby观察

- 7天前

- 1845

- 0

- 0

喜讯!米尔电子与安路科技达成IDH生态战略合作,共筑FPGA创新生态

以芯为基,智创未来。近日,领先的嵌入式模组厂商-米尔电子正式与国产FPGA企业安路科技达成IDH生态战略合作。双方将围绕安路科技飞龙SALDRAGON系列高性能FPSoC,联合开发核心板、开发板及行业解决方案,助力开发者开发成功,加速工业控制、边缘智能、汽车电子等领域的创新应用落地。米尔电子&安路科技IDH生态合作证书硬核技术+生态协同安路科技作为

- 企业米尔电子

- 8天前

- 837

- 0

- 0

Xilinx Ultrascale系列FPGA的时钟资源与架构解析

Ultrascale是赛灵思开发的支持包含步进功能的增强型FPGA架构,相比7系列的28nm工艺,Ultrascale采用20nm的工艺,主要有2个系列:Kintex和Virtex。Ultrascale+采用16ns,有3个系列:Artix,Kintex,Virtex。不仅是工艺制程方面,在其他方面也存在较大改进,如时钟资源与架构,本文将重点介绍Ultrascale的时钟资源与架构,Ultrascale+和Ultrascale大体上相似。

- 专栏FPGA设计论坛

- 9天前

- 402

- 0

- 0

京微齐力亮相2025慕尼黑上海电子展

此前,4月15日-17日,为期三天的2025慕尼黑上海电子展(Electronica China 2025)在上海新国际博览中心成功举办。京微齐力携多项产品及丰富的解决方案重磅亮相此次行业盛会,集中展示了企业的技术研发成果。期间,凭借多项实体化应用解决方案的展示,吸引了众多与会者关注,通过与行业同仁的深入交流,进一步了解用户对于产品的实际落地需求,精准把握市场风向。

- 专栏HME京微齐力

- 12天前

- 431

- 0

- 0

Altera大学成立,助力FPGA教学发展与人才培养

近日,全球 FPGA 创新技术领导者 Altera 宣布成立 Altera 大学,旨在以高效、便捷的方式助力 FPGA 教学发展与人才培养。Altera 大学为高校教授、科研人员和广大学子提供精心设计的课程、丰富的软件工具和可编程硬件,助力其深入探索 FPGA 技术。

- 专栏英特尔FPGA

- 14天前

- 358

- 0

- 0

英特尔向银湖资本出售Altera 51%股份

英特尔公司宣布已达成最终协议,将旗下 Altera 业务 51% 的股份出售给全球技术投资巨头银湖资本(Silver Lake)。

- 专栏英特尔FPGA

- 14天前

- 397

- 0

- 0

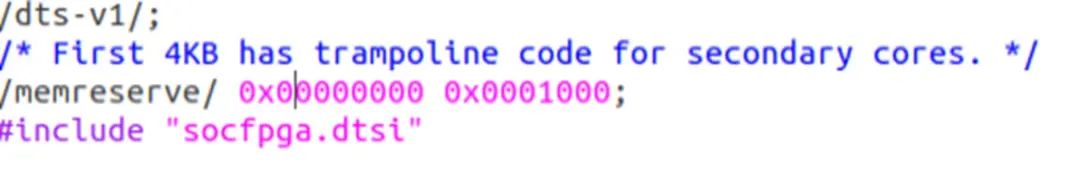

Linux系统中通过预留物理内存实现ARM与FPGA高效通信的方法

在嵌入式系统开发中,ARM 和 FPGA 之间的通信可以使用 ARM 侧的 DDR 作为通道。由于 FPGA 也可以直接访问到 ARM 侧 DDR,但 DDR 作为共享通信时,就不能被操作系统的内存管理子系统管理。因此,需要预留一部分物理内存,使其不被内核管理。接下来将为大家详细介绍在 Linux 系统中通过预留物理内存实现 ARM 与 FPGA 高效通信的方法,预留物理内存包括 memreserve、Linux 内核启动参数 cmdline 和 Linux Reserved-Memory 三种方案。

- 专栏骏龙电子

- 17天前

- 356

- 0

- 0

易灵思2025 FPGA技术研讨会北京站圆满结束

易灵思2025FPGA技术研讨会北京站于4月10日在北京丽亭华苑酒店圆满结束!本次研讨会吸引了来自全国各地的行业专家、工程师及企业代表踊跃参与,现场座无虚席,气氛热烈。

- 专栏易灵思官微

- 17天前

- 309

- 0

- 0

FPGA+AI王炸组合如何重塑未来世界:看看DeepSeek东方神秘力量如何预测

近期,DeepSeek这个名字在AI圈彻底炸开了锅并且关于DeepSeek的消息网络铺天盖地,短视频,朋友圈随处可见不少网友留言称其是“来自东方的神秘力量”又一次震撼海外人士心脏“这太疯狂了”“大模型圈的大黑马”“硅谷震惊了”“来自中国的学霸级AI”……从智能手机到自动驾驶,从数据中心到物联网,FPGA正悄然改变着我们的生活。未来,FPGA又将如何塑造世界?

- 企业小眼睛科技

- 19天前

- 409

- 0

- 0

高云半导体荣获“2024年度电子元器件行业国产品牌FPGA/处理器创新成长企业”

4月11日,华强电子网主办的“2025半导体产业发展趋势大会暨2024年度华强电子网优质供应商&电子元器件行业优秀国产品牌颁奖盛典”盛大举办。 高云半导体凭借其在国产FPGA行业十余年的深耕、突出的产品优势和出色的市场表现,成功荣获“2024年度电子元器件行业国产品牌FPGA/处理器创新成长企业”。 这一殊荣是对高云半导体在国产FPGA行业卓越成就的高度认可与肯定。高云半导体自公司成立至今,始终坚持长期主义,以产品为基础,质量为保证,技术驱

- 专栏高云半导体

- 19天前

- 329

- 0

- 0

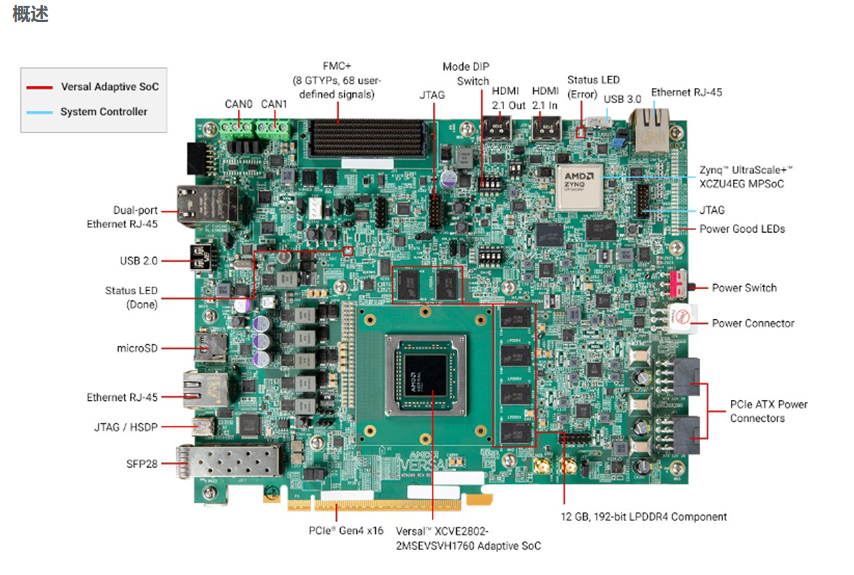

面向AI与机器学习应用的开发平台 AMD/Xilinx Versal™ AI Edge VEK280

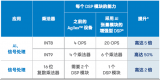

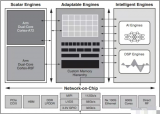

AMD/Xilinx Versal™ AI Edge VEK280评估套件是一款面向AI与机器学习应用的开发平台,专为边缘计算场景优化设计。以下从核心配置、技术特性、应用场景及开发支持等方面进行详细解读: *附件:VEK280_用户指南 开发手册.pdf 一、核心配置与架构 自适应SoC芯片 基于AMD Versal™ AI Edge系列VE2802自适应SoC,集成AI引擎机器学习(AIE-ML)和可编程逻辑单元(FPGA)。其核心资源包括: 304个DSP引擎 与 1,312个系统逻辑单元 ,支持高效并行计算; 228 TOPS INT8算力 ,适

- 专栏eeDesigner

- 22天前

- 773

- 0

- 0

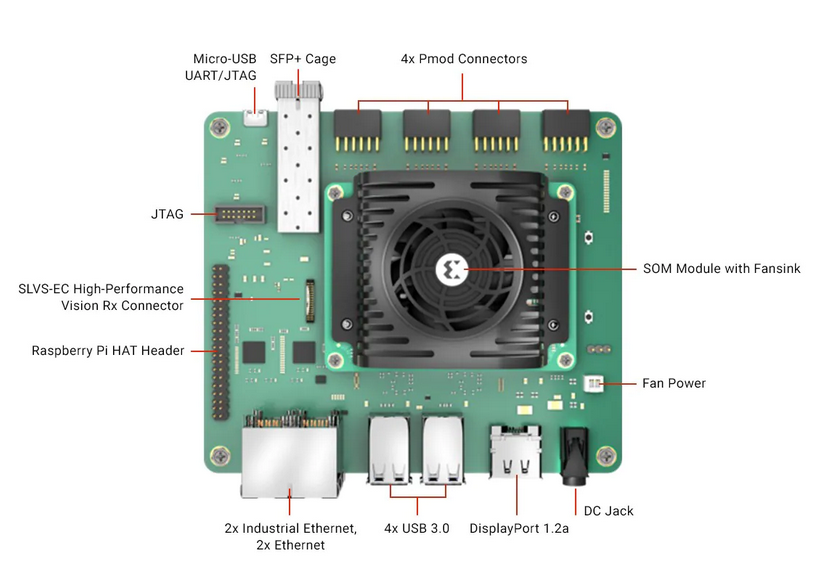

机器人开发套件 Kria KR260

AMD/XilinxKria KR260机器人入门套件是一款基于Kria K26 SOM的开发平台,设计用于机器人和工业应用。它具有高性能接口和原生ROS2支持,便于机器人和软件开发人员开发。KR260机器人入门套件提供基于ROS的开发体验,为机器人和嵌入式开发人员提供快速简便的工作流程。 *附件:Kria KR260 Robotics Starter Kit 数据手册.pdf 通过硬件加速释放机器人的潜力 用户指南 产品简介 Kria KR260机器人入门套件包括载卡、Kria K26 SOM和散热解决方案。该SOM非常紧凑,仅包括Zynq® Ultra

- 专栏eeDesigner

- 22天前

- 494

- 0

- 0

Altera Agilex 7 M系列FPGA正式量产出货

近日,全球 FPGA 创新技术领导者 Altera 宣布, Agilex 7 M 系列 FPGA 正式量产出货,这是现阶段业界领先的集成高带宽存储器,并支持 DDR5 和 LPDDR5 存储器技术的高端、高密度 FPGA。Agilex 7 M 系列 FPGA 集成超过 380 万个逻辑元件,并针对 AI、数据中心、下一代防火墙、5G 通信基础设施及 8K 广播设备等对高性能、高内存带宽有较高需求的应用进行了专门优化。

- 专栏英特尔FPGA

- 23天前

- 390

- 0

- 0

基于FPGA的FIFO实现

FIFO(First in First out)为先进先出队列,具有存储功能,可用于不同时钟域间传输数据以及不同的数据宽度进行数据匹配。如其名称,数据传输为单向,从一侧进入,再从另一侧出来,出来的顺序和进入的顺序相同。

- 专栏FPGA设计论坛

- 24天前

- 288

- 0

- 0

面向Altera FPGA和SoC的边缘就绪型AI工具套件

如今,边缘采集的数据量十分庞大。据 Gartner 预测,到 2025 年,将有多达 75% 的企业数据会在传统数据中心以外生成[1]。

- 专栏英特尔FPGA

- 26天前

- 359

- 0

- 0

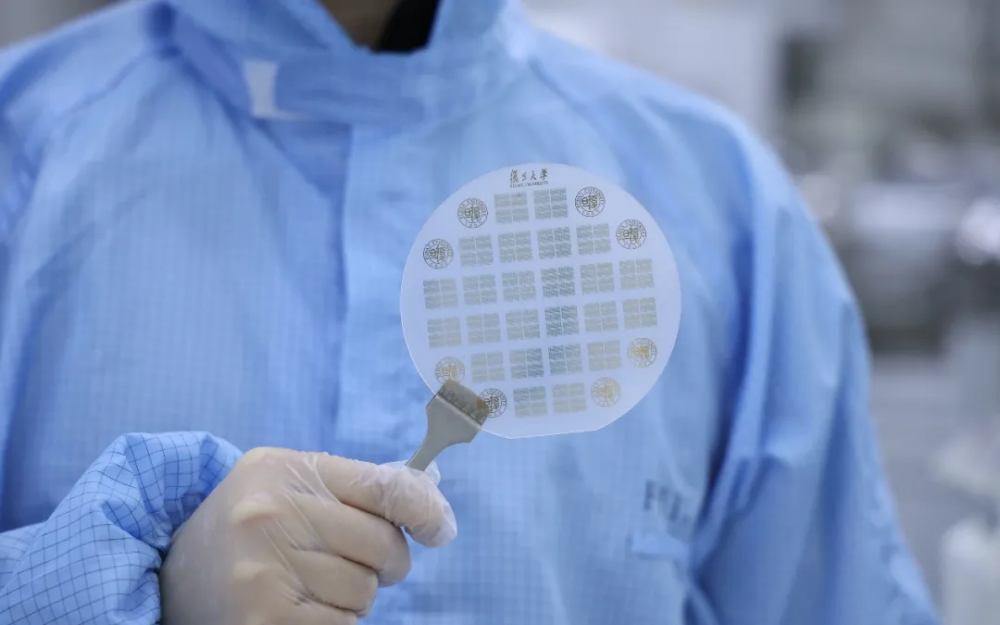

原全球首款二维RISC-V MPU!命名“无极”,来自复旦团队

电子发烧友网报道(文/吴子鹏) 近日,复旦大学集成芯片与系统全国重点实验室周鹏、包文中联合团队成功研制出全球首款基于二维半导体材料的 32 位 RISC-V 架构微处理器 ——“无极(WUJI)”。 “无极” 芯片,图源:复旦大学 据悉,该成果于北京时间 4 月 2 日晚间以《基于二维半导体的 RISC-V 32 比特微处理器》(“A RISC-V 32-Bit Microprocessor Based on Two-dimensional Semiconductors”)为题发表于《自然》(Nature)期刊。论文显示,这项成果突破了二维半导体电

- 专栏Felix分析

- 27天前

- 2080

- 0

- 0

FPGA在数字化时代的主要发展趋势

随着数字化时代的飞速发展,人工智能(AI)、大数据分析、自动驾驶等新兴领域的需求不断攀升。FPGA作为灵活可编程的硬件平台,正成为AI与高性能计算等领域的重要支柱。这一趋势不仅推动了FPGA架构的创新,也对开发者提出了新的要求。这篇文章将带您深入探讨FPGA发展趋势,并剖析这些变化对开发者的影响与挑战,为在新时代的技术浪潮中把握机遇提供参考。

- 专栏FPGA设计论坛

- 1月前

- 451

- 0

- 0