MCP19117 Touch Dimming LED Lighting

软体CVD 的架构原理与介绍:

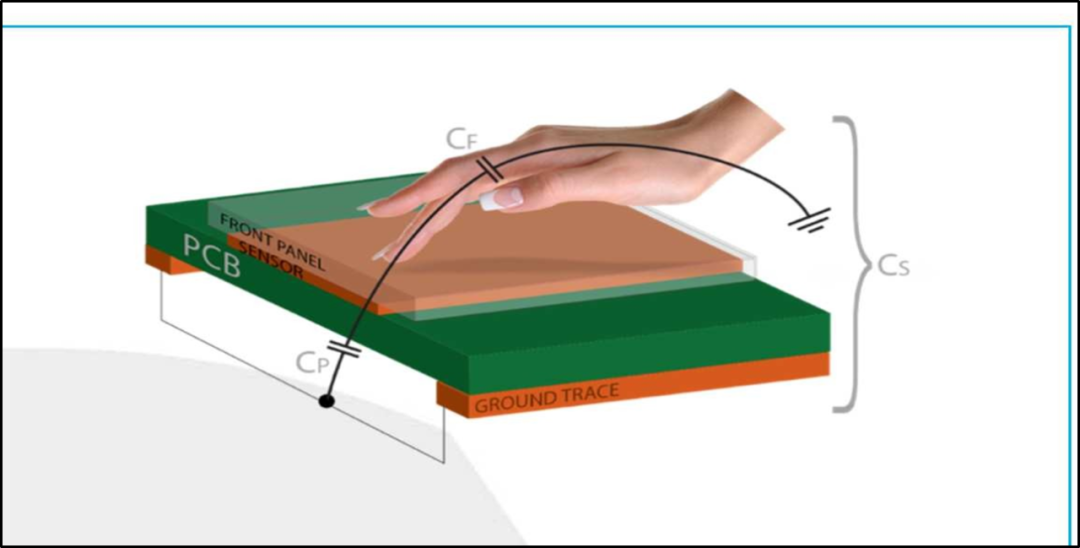

下图为一标准的触控点的电容分布简易图 。原本 PCB 的走线及触控点本身就有寄生电容的存在;人体本身也有寄生电容的存在。当手指靠近或碰触到触控感应点(Touch Pad) 时,这时 Cp 与 CF 就会因电容并联电量相加 Cs 就会变大。反之,触控点没有被触 摸也就没有外在的影响会去改变其寄生电容量。CVD 的内涵就是测量这单位时间内电容上 的电压变化来判断是否有触摸或接近感应点。

CP: 触控点的寄生电容

CF: 手指的电容

Cs: 触控点的电容总和 (并联效应)

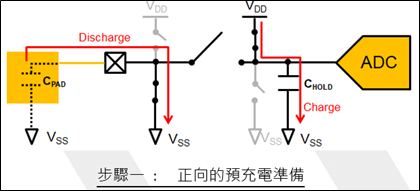

一 : 正向的预充电准备:

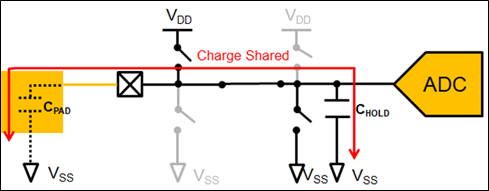

由下图可以很清楚的看出取样电容 (CHOLD) 透过内部的设定,将 CHOLD 接到 VDD 将其充电到 VDD。而外部的触控点 则是透过 I/O 脚接地将寄生电容的电荷先放光。

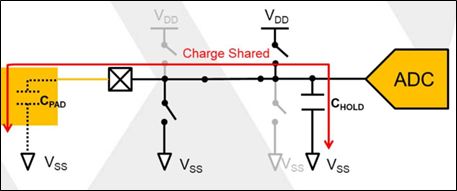

二 : CHOLD 开始放电取得电位的平衡并转换

关闭外部触控点的接地使其浮接,再来取样电容 (CHOLD) 透过 ADC通道的设定直接连接到外部的触控点,这时 CHOLD 的电荷就会往外流向触控点的寄生电容Cpad。因为外部的寄生容量很小,很快的这放电就会取得一个电荷的平衡电压点。这个时候启动 ADC 做转换就可以得到触控按键的正向充放电的数值。

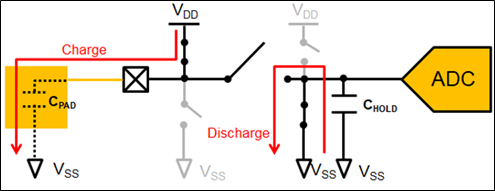

三 : CHOLD负向充、放电的切换

其实经由步骤一及步骤二的处理,我们已经可以分办出触控按键的动作。但为加强按键对杂讯的抗干扰能力,在步骤三里做了一次负向的充放电的动作。也就是将外面的寄生电容先充饱到 Vdd,CHOLD 则透过内部的 设定连接到地将电荷先放光。

四 : CPAD 与 CHOLD 之间的电位平衡

当触摸点的寄生电容 (CPAD) 充饱电荷之后,经由内部开关的切换连接到 CHOLD 时,电荷将取的平衡。这时启动 ADC 做转换以取得反向平衡电压数值。

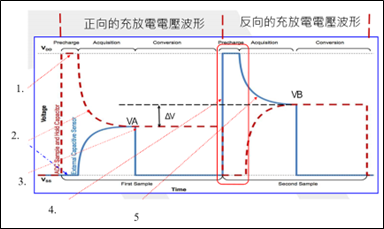

五 : 正向及负向 CPAD 及 CHOLD 的电压变化

此图很明显地画出正、负两种 充放电的电压变化。

CHOLD (红色)充电到 VDD ,CPAD (蓝色) 放电到 Vss 阶段。

CHOLD 向 CPAD 放电的阶段

大、小水库取的平衡的阶 段,ADC 开始转换

负向预充电开始,CPAD 充电 到 VDD,CHOLD 接地将电荷放尽 到 0 V 。

CPAD 向 CHOLD 放电取的电荷 上的平衡后进行 ADC 的转换

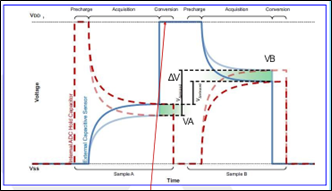

六 : 如何判断按键有被触摸?

如何判断按键有被触摸呢?

在 CVD 的波形图示里,VB点的转换电压值及VA 转换点的电压值之间的差异电压ΔV 就可以判断出是否有按键。此图所显示的是有按键及没有按键时的波形,同时也可以看出其ΔV 电 压的差异。借由此种判断触控按键 是否按下,这样的侦测方式可以得到更大的差值,大大的提高了触控的稳定。为了更有效率 ,在 ADC 对内部的取样电容( CHold)做转换时,软体立即切换至 Pad 的寄生电容开始做预充电的动作,如此预充电的做法可加快触控按键扫描的时间而不影响其精确度。

以上就是最简单的 C VD 原理说明。看起来似乎只要有ADC就可以做 CVD 的量测。

其实,只要是有内建 10-bit ADC的MCU,不管是 8、16 或 32-bit的MCU都可以实现软体 CVD 的功能。

PCB Layout 注意事项

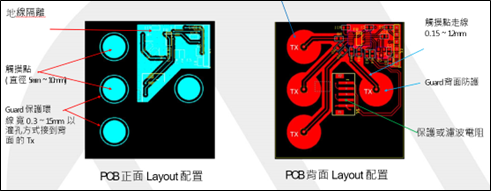

所有触控感应器都可以共同使用一条 Guard 的输出。mTouch 会以顺序扫描方式进行感测。所以 Guard 在主动驱动防护时,触控感应器在扫描的情况下是不会影响其它的感应器。

适当的在没使用到的区域补铺上、下层的地网,并增加灌孔以降低彼此之间阻抗达大最佳的抗干扰能力。

在 PCB Layout 的正面: 触控感应点(Pad)的大小不建议小于 5mm 的直径,理想的触控点的Layout 最好是大于 10mm 的直径。

在PCB Layout 的正面:围绕在触控感应点周围 Guard 环形线宽应该约 0.3 ~ 1.5mm 的宽度,并与触控感应点约有 0.3 ~ 2mm 的距离。

在PCB Layout 的背面:从触控感应器开始拉线到 MCU 之后接脚的这一段 PCB 走线也是很重要的,建议使用 0.15mm ~ 1.2mm 的线宽。该Guard Line 与触控拉线之间的间距可以小到 0.4mm,

最好以 Pad 的形状在背面 加入 Guard 防护 (如红色 PCB 背面的 Tx Layout 方式)。

为降低来自感应点高频杂讯干扰,在感应器拉线进入MCU接脚之前须串个10K (建议值)的电阻。

这电阻最大的功能是: 一. 保护感应器的输入脚避免 ESD 的损坏。

与内部电容形成一 个低通滤波器可将高频杂讯滤掉, (滤波电容尽量靠近 MCU 的接脚,如 此可获得较大的滤波效果)。

**本文内容(含图片)转载自Microchip 官方网站

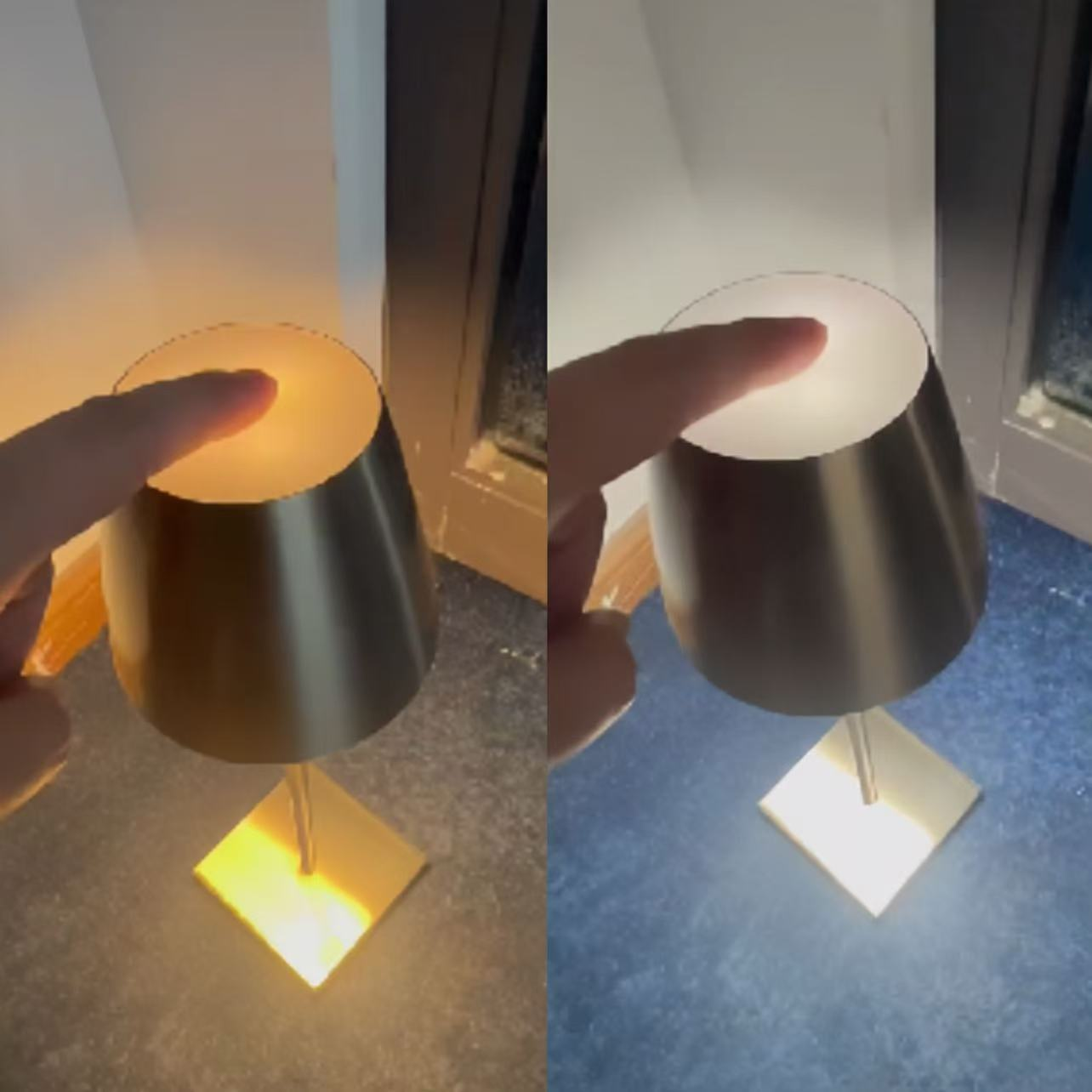

► 场景应用图

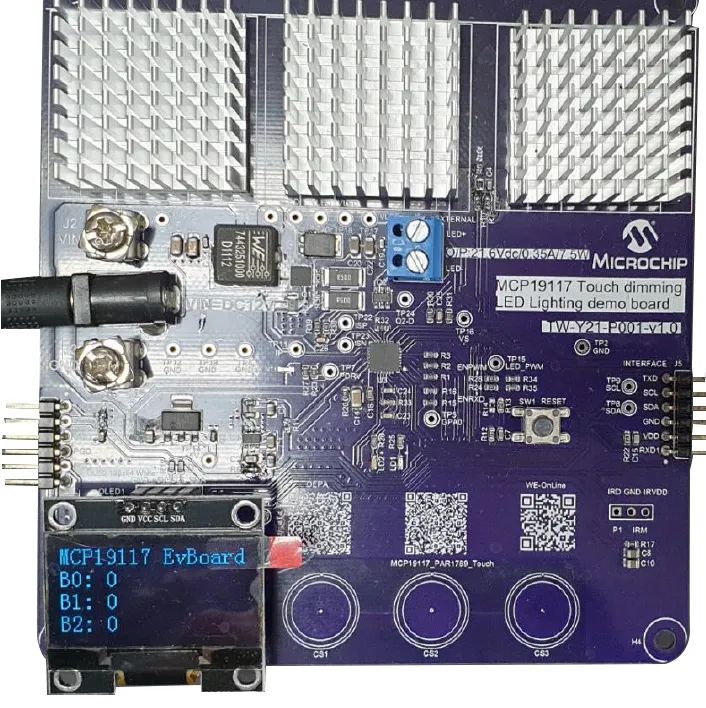

► 展示版照片

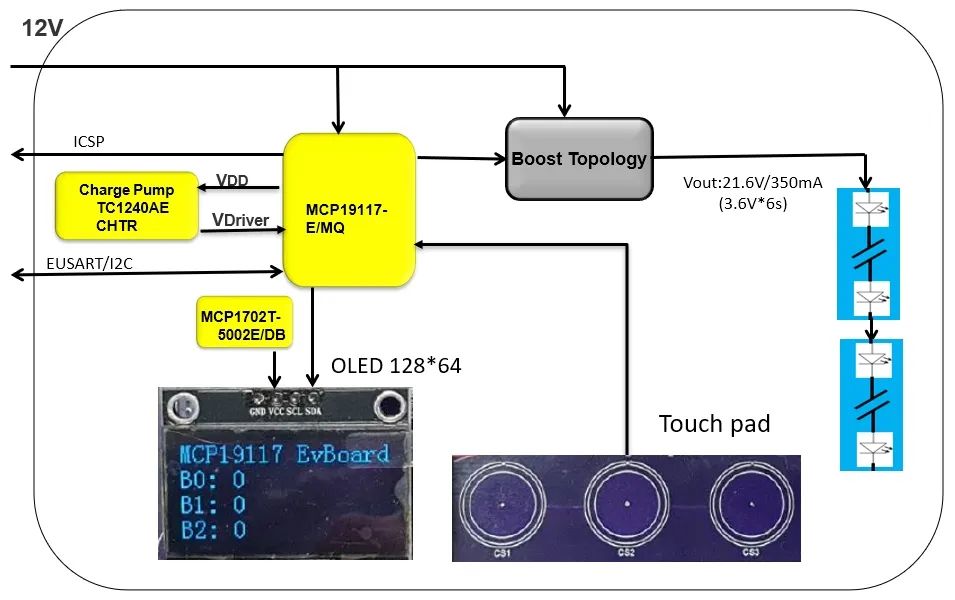

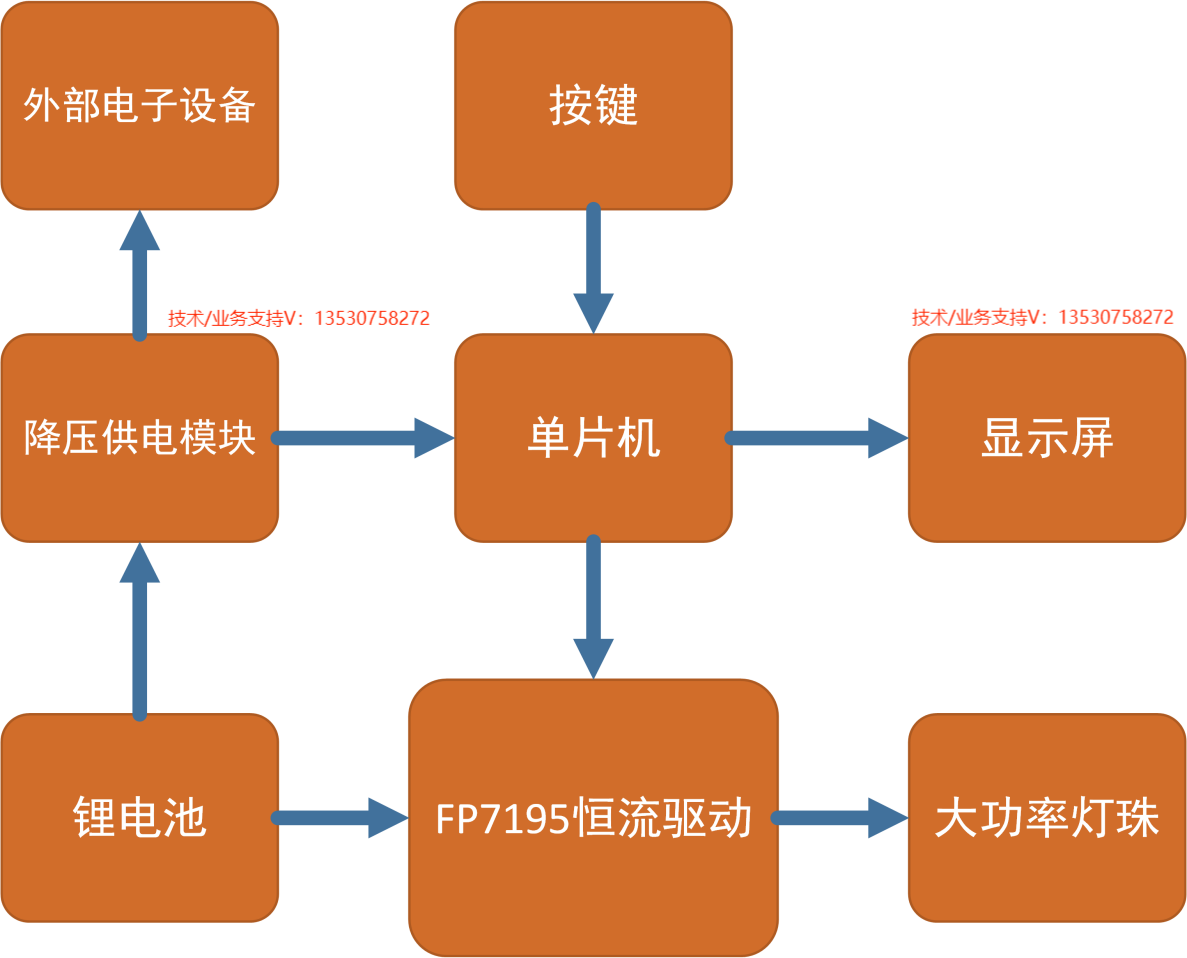

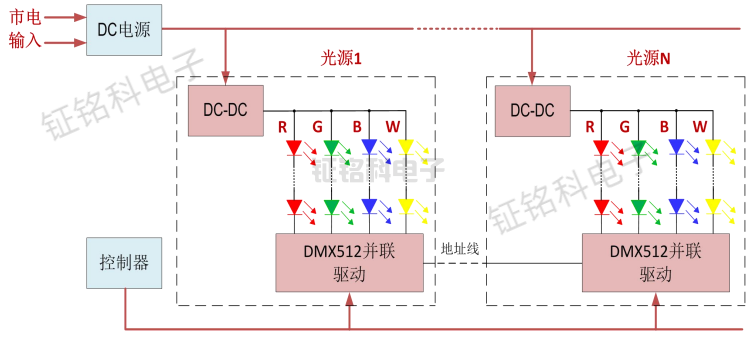

► 方案方块图

► 核心技术优势

DEPA 芯片内有高度整合之8位元MCU/ PWM 控制器/电源稳压器/ Gate Driver

1.芯片整合在5*5 mm 之QFN 包装可以有效缩减产品面积;

2.使用硬体ADC 与软体判断方式达到触控之功能、毋需专用IC

3.整合类比控制元件使稳定度可以提高;

4.拥有类比的反应速度与数位控制的灵活性;

5.免费的软体开发环境;

6.透过AUSART 或I2C 读取或设定设备之工况。

► 方案规格

1.Vin: 12V(Typ.)

2. Vout: 25V (OVP)

3. VLED: 3.6V * 6 = 21.6V

4. ILED: 350mA +/- 5%

5. 0% - 16 % PWM Dimming, 17-100% Constant Current Dimming.

-

led

+关注

关注

242文章

23306浏览量

661542

发布评论请先 登录

相关推荐

PWM在LED调光中的应用

SL8700 LED智能汽车氛围灯芯片 智能调光IC 支持0.1%调光深度

冷暖色触摸无极调光桌面小夜灯方案开发

多路共阳调光 0.1%PWM深度调光 12V24V48V60V100V150V磁吸灯台灯方案SL8700

晶丰明源42W DALI调光方案介绍

LED恒流IC领域的照明方案

调光电源控制器——电阻调光器

FS102WS是一款用于 LED 灯光开关控制及亮度调节的触摸IC

小区LED灯光亮化设计方案:SM18512PK

方案 | MICROCHIP MCP19117 触控式调光LED灯光控制方案

方案 | MICROCHIP MCP19117 触控式调光LED灯光控制方案

评论