分享产品试用报告,测试板卡是基于Xilinx Zynq-7000系列XC7Z010/XC7Z020高性能低功耗处理器设计的异构多核SoC工业级核心板。

以下为测评内容,欢迎阅读:

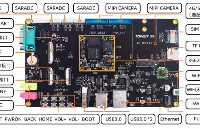

TLZ7x-EasyEVM是广州创龙基于Xilinx Zynq-7000 SoC设计的高速数据采集处理开发板,采用核心板+底板的设计方式,尺寸为160mm*108mm,它主要帮助开发者快速评估核心板的性能。核心板采用12层板沉金无铅设计工艺,尺寸为62mm*38mm,引出PL端和PS端全部可用资源信号引脚,降低了开发难度和周期,以便开发者进行快捷的二次开发使用。

底板采用4层无铅沉金电路板设计。Xilinx Zynq-7000 SoC集成PS端单核/双核Cortex-A9 ARM + PL端 Artix-7 架构可编程逻辑资源;PS 端最高主频可达 866MHz;使用 Vivado HLx,兼容 Xilinx 最新的 SDSoc 开发环境,为异构 Zynq 全可编程SoC 部署提供类嵌入式 C/C++应用的开发体验,可通过 C/C++开发算法,可加快算法开发进程。

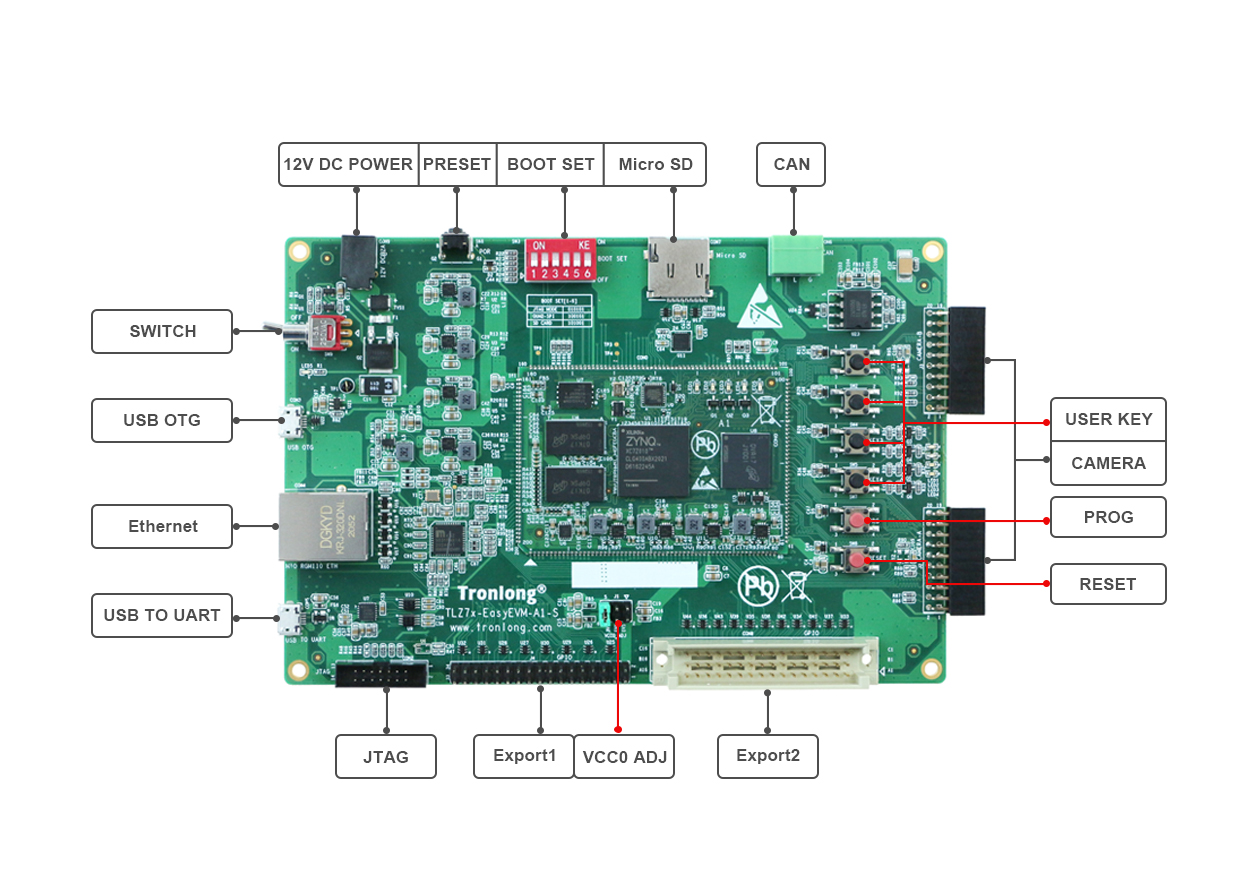

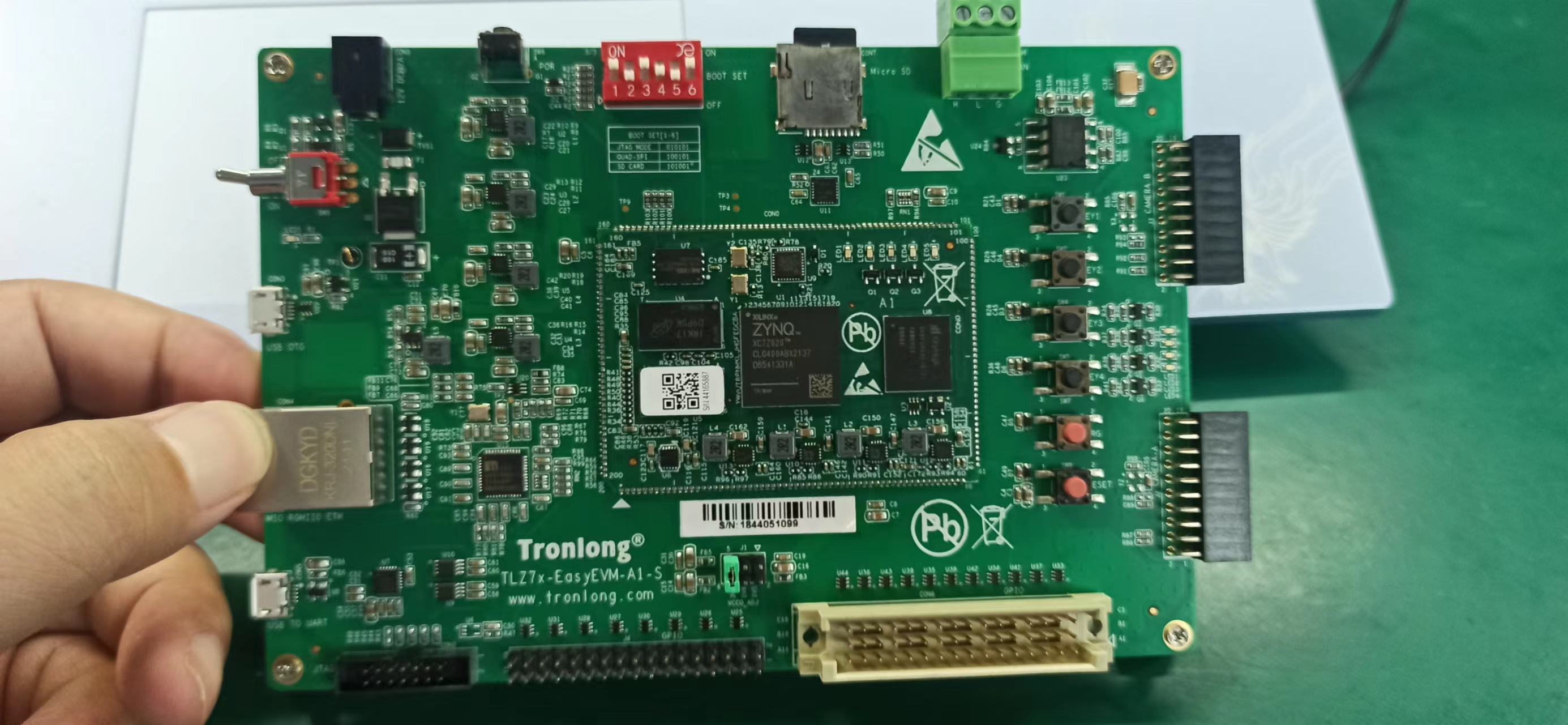

上图:

开发板:做工杠杠滴,工控首选。

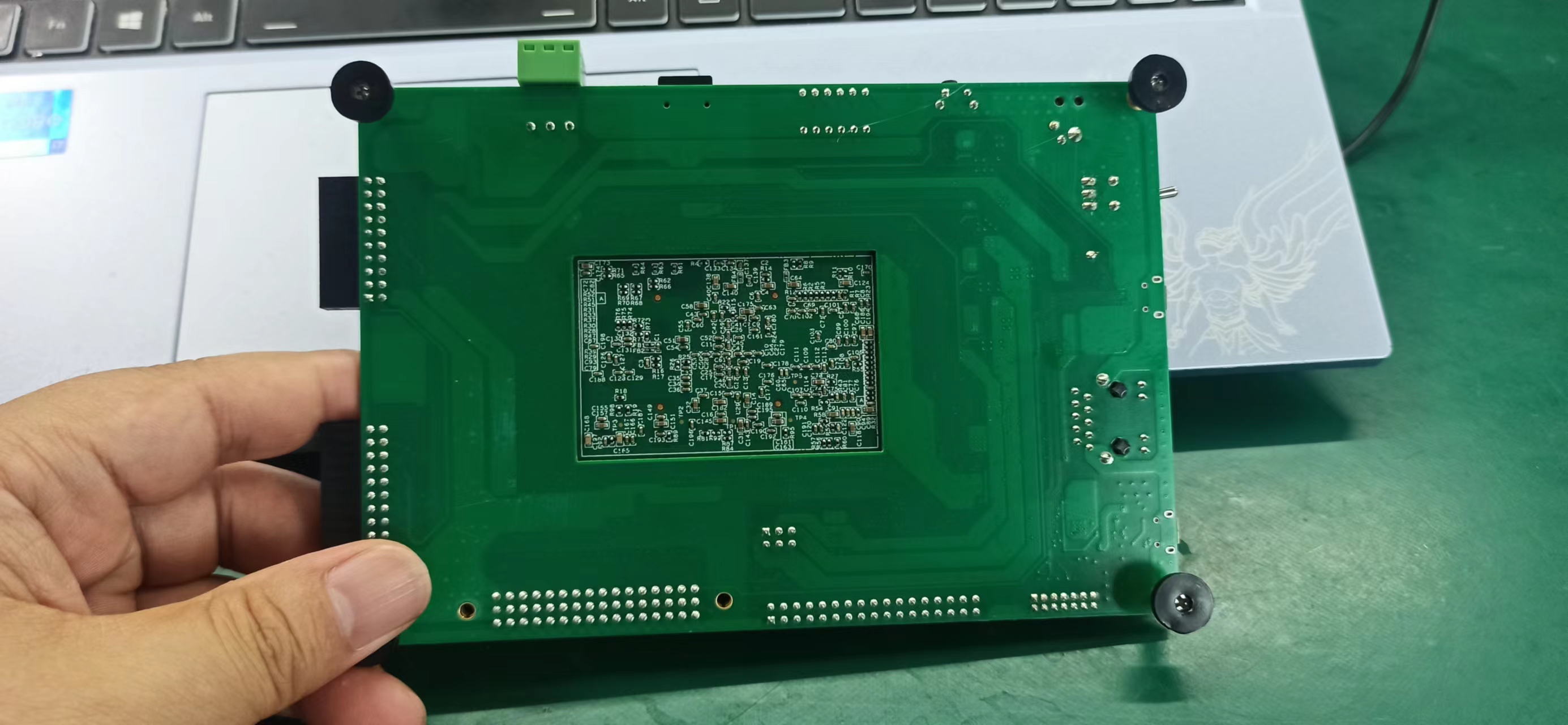

地板:

配件:

光盘虽然老,但是比起某云,读起来那是快得多。

地板资源:

1、USB HOST接口,PHY芯片型号为USB3320C-EZK。

2、千兆以大网接口,PHY芯片型号为KSZ9031RNXIA,这也是很常见的PHY。

3、一个USB转两路串口,一路串口连接PS侧UART,另外一路串口连接PL侧UART。

4、一个2x 7pin的JTAG接口,间距2.0mm。

5、一个2x 17pin的扩展GPIO接口,间距2.54mm。

6、一个GPIO/USB/HDMI扩展接口, 共3x16=48pin的欧式端子。

7、两个Camera接口,为2x 20pin排母,间距2.54mm。

8、1个VCC0_ADJ电压配置接口,用于配置FPGA端电压,1.5V、1.8V和3.3V可选

9、一个软复位按键。

10、一个PL端PROG按键。

11、四个用户按键(PS端1个,PL端3个)。

12、一个CAN接口,3pin绿色端子,间距2.54mm,CAN芯片型号为TI的ISO1050DUBIsolated CAN Transceiver。

13、一个TF卡接口。

14、一个1x 6bit拨码开关用作BOOT SET。

15、一个侧按复位按键。

-

嵌入式开发

+关注

关注

18文章

1028浏览量

47563 -

开发板

+关注

关注

25文章

5032浏览量

97373 -

硬件开发

+关注

关注

3文章

156浏览量

24166 -

全志科技

+关注

关注

4文章

104浏览量

16094

发布评论请先 登录

相关推荐

Xilinx XC7Z020双核ARM+FPGA开发板试用合集——硬件赏析

Xilinx XC7Z020双核ARM+FPGA开发板试用合集——硬件赏析

评论