关键词:光栅传感器,测量,细分

1 引 言

目前,各类伺服驱动器及其应用中广泛采用光栅装置作为速度测量、位置测量的敏感元件。而且,广泛采用两路正交方波的形式,系统的实时性要求极高。因此,对于光栅编码器的信号的细分等主要处理环节,一方面集中考虑提高分辨率的问题,同时,需要考虑实时性的问题。

尽管高速单片机、DSP等高速数字处理器件的应用可以极大地改善系统的实时性,但是做除法运算仍需较长的时间,大约为几百微秒,无法满足系统实时性的要求,因此,软件细分的方法受到了限制。

目前,有很多采取纯硬件进行细分的方法,如,电阻链细分,空间细分,锁相倍频,还有两种方法的结合使用等。上述几种方法在实际应用中被广泛采用,特别是电阻链细分,在低倍频的情况下是一种很好的方案。但是在高倍频的情况下,不可避免地出现大量使用比较器的情况,以及比较器死区(滞后区)问题,难以调节。空间细分的方法中,主要解决的问题是切割电平精准的问题,其中的三角波切割三角波的方案有很多优点,可以改变使用过零比较造成的细分误差。但是仍然存在大量使用比较器的问题,调节起来比较繁琐。锁相倍频细分的方法,一方面,成本较前两种高,另一方面,受环境温度的影响比较大,实际的应用中很少采用。本文从原理上考虑了一种新的细分方案,使用取绝对值,八卦限理论,利用ASIC器件(速度为纳秒级)对信号进行逻辑运算和处理等一整套纯粹硬件的信号细分方案,并通过调试和实际应用,验证了该方案的可行性。

2 细分原理及框图

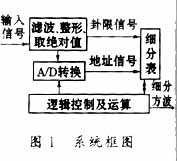

细分主要由以下几个部分构成,取绝对值、提取卦限信号、A/D转换、查细分表、逻辑运算等。系统框图如图1所示。

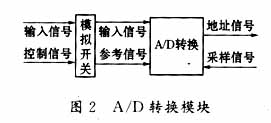

A/D转换模块对绝对值信号进行采样转化,如图2所示:模拟多路开关在卦限控制信号的作用下,对绝对值信号进行选择,其输出分别作为A/D转换的输入信号和参考信号。A/D转换受控于采样控制信号,其输出数据与采样时刻的相位信号对应。

如果将该数据与相位之间的对应关系用一张表来描述,就是我们所建立的细分表。但是由于细分倍数的不同,两者之间并不是一一对应关系。

3 硬件设计与调试

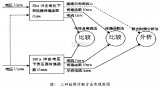

从原理上可以看出,该细分模块的技术关键是比较器整形产生的卦限信号和A/D模块产生的地址信号必须同步,这是能否正确细分的关键。因此,在电路设计过程中,比较器的滞后及其抗干扰能力是必须考虑和解决的问题。在抗干扰方面,采用差分放大,可以有效地抑制共模干扰。考虑其滞后问题,采用整形电路与取绝对值电路分离,可以通过调节各个运放的直流参数,使得卦限信号与绝对值信号能够近似同步,否则,产生的细分方波将会在过零处变得混乱。如图3所示,对其中sinx信号取绝对值及整形,这样一来,既方便了调试,也避免了干扰及比较器的滞后问题。

逻辑控制电路及运算模块主要完成对A/D转换模块的采样控制、读存储器(细分表)、运算输出细分正交方波等逻辑。整个模块由FPGA来实现。外围晶振提供10MHz的时钟,由分频模块进行分频,实现周期为2μs(满足系统最大500kHz的反馈要求)的脉冲列作为采样控制信号。在A/D转换模块完成采样转换并且转换结束信号/INT为低电平时,此时,卦限信号及地址信号在存储器的地址信号线上有效,在FPGA内部经过逻辑判断后,发出读(/RD)命令。读取的数据经锁存后提供给后序运算模块,经判断运算后输出正交细分方波。

4 检测及检测结果

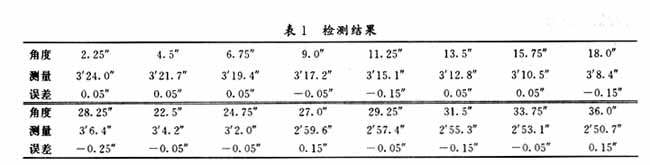

如图4所示,我们搭建了细分检测硬件平台,由标定系统一维平转台和同轴的圆光栅编码器构成。数显装置显示了标定转台实际转过的角度,同时,主机通过接口电路对细分方波进行计数并显示,经过多次测量,两显示值之间的差e≤1,即,小于等于一个当量,达到了设计目的。同时,通过伺服驱动的一维平转台系统及检测机构来定量地检测分析细分误差,初始位置:3′26.3″,末位置:2′50.7″,差值:3′26.3″-2′50.7″= 35.6″,36.0″-35.6″=0.4″,结果如表1所示。

5 结束语

采用纯硬件的手段可以满足系统实时性的要求,采样速度为2μs。同时,采用该方法可以实现高倍频细分,满足大多数系统对于两路正交反馈方波的需求,可以在光栅编码器信号处理中采用。

2 徐志辉,徐光辉.CPLD/FPGA的开发与应用.北京:电子工业出版社,2002

3 张善锺.计量光栅应用技术.北京:机械工业出版社,19844 Alice EFischer,David W Eggert.Applied C:An Intro-duction and More.北京:电子工业出版社,2002

电子发烧友App

电子发烧友App

评论