在日常工作和学习中,经常需要对作息时间进行控制,以规范工作、学习、休息等作息秩序,本文采用51系列单片机机实现对校园作息时间的控制设计,已完成对每天对作息最多40次打铃控制,同时具有对控制器日常时间调整及显示、打铃时间设置、掉电数据不丢失等功能。

系统硬件结构组成

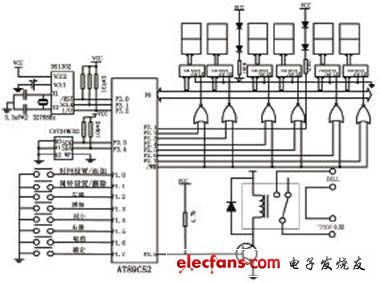

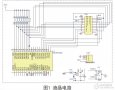

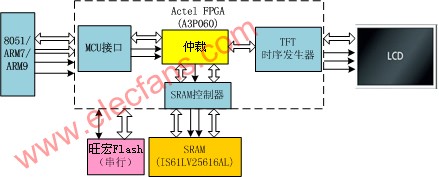

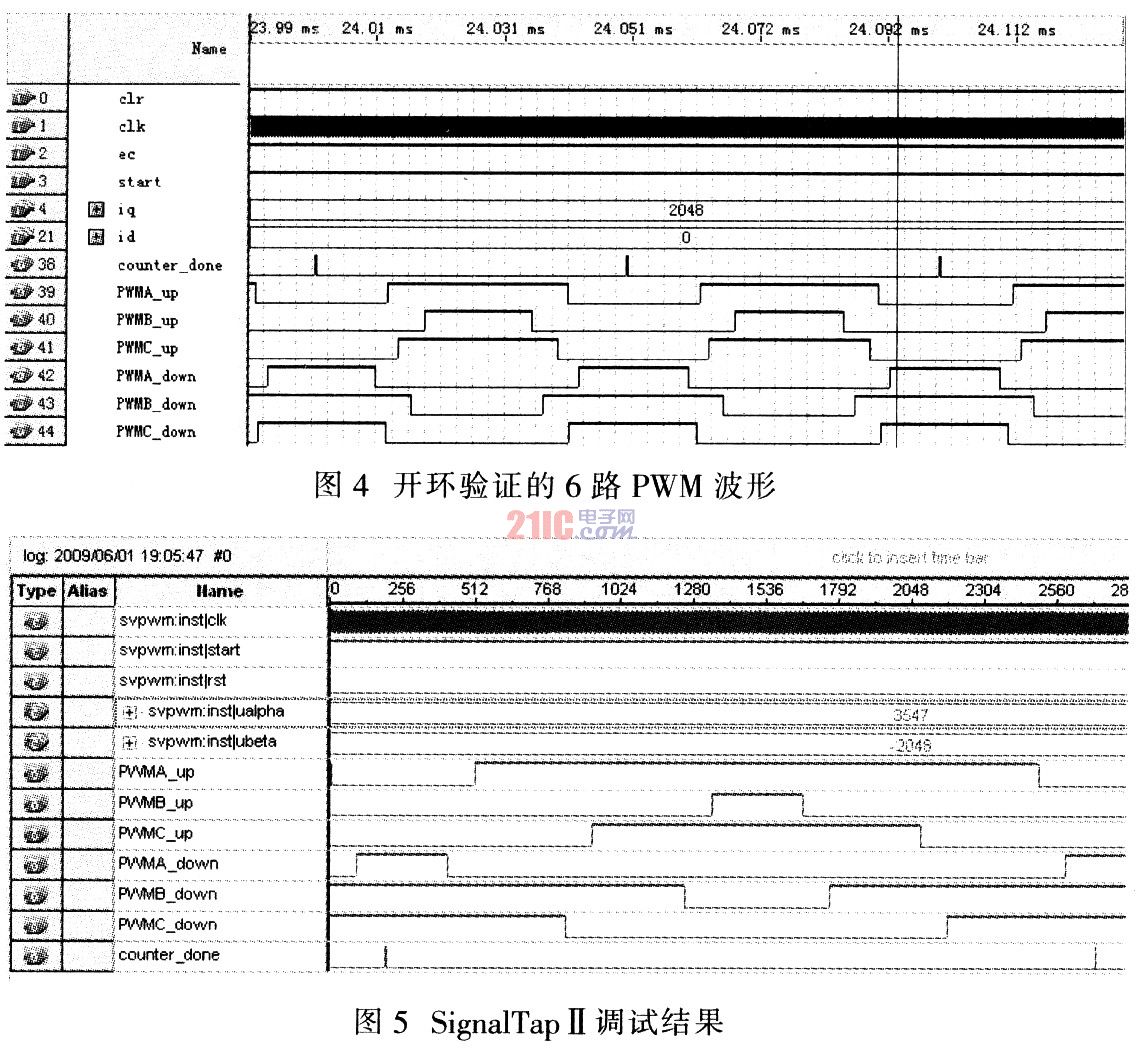

为实现上述功能,硬件方面主要采用AT89C52单片机实现对整个系统控制,采用DS1302时钟芯片完成对控制器时间的计时控制,同时采用24C02串行存储芯片保存打铃时间控制参数以免掉电丢失,设计8个按键分别用于对时间调整和打铃时间的设置和调整,并采用静态显示方法对6个数码管控制已完成对时间及打铃时间点等参数的设置和调整显示,采用继电器控制电路完成弱电对强电220V控制以完成对电铃的通断电控制从而控制铃声。具体电路图如图1所示。

图1 作息打铃控制器硬件原理图

本设计为防止掉电后所设置电铃时间点数据丢失,特用一片IIC协议串行通信的含有256字节的EEPROM芯片CAT24WC02作为存储芯片。IIC协议允许系统设计者只用两根线就可以将多达128个不同的设备连接在一起,极大的节省了单片机接口线,只需在这两根线上分别加一个10kΩ的上拉电阻,即可解决阻抗匹配问题。IIC器件通过各自的硬件连线方式来确定自己的地址,如本设计中CAT24WC02芯片地址为0000。对于没有IIC总线接口的单片机来说,使用任何两根线均可模拟IIC总线时序。在本设计中采用P3.3、P3.4分别来模拟SCL和SDA线,当SCL处于高电平时,SDA由高电平变成低电平时构成一个开始条件,对IIC总线的所有操作均须由开始条件开始;当SCL处于高电平时,SDA由低电平变成高电平时构成一个停止条件,此时IIC总线的所有操作均停止;当SCL为低电平且SDA线电平变化时,则数据由CPU输出到IIC总线;当SCL为高电平且SDA线电平不变时,则CPU读取IIC总线上的数据;当SCL为高电平且SDA电平变化时,IIC总线上位开始条件或停止条件;数据传输以8为序列进行,IIC器件在第9个时钟周期时将SDA置位为低电平,即送出一个确认(应答)信号ACK,表明数据已经被其收到。这里使用到以下4个公用函数:

void I2cStart(); //产生开始信号

void I2cStop(); //产生停止信号

void I2cSendByte(uchar ByteData) ;//发送一个字节数据

uchar I2cReceiveByte(); //接收一个字节数据

DS1302时钟电路

DS1302是美国Dallas公司推出的一种高性能、低功耗、带RAM的实时时钟芯片,它可以对年、月、日、星期、时、分、秒进行计时,具有闰年补偿功能,工作电压宽达2.5V~5.5V。采用三线接口与CPU进行同步通信,并可采用突发方式一次传送多个字节的时钟信号或RAM数据。DS1302内部有一个31字节用于临时性存放数据的RAM寄存器。DS1302控制电路图如图1所示,VCC1为后备电源, VCC2为主电源,在主电源关闭的情况下,也能保持时钟连续运行。DS1302由VCC1或VCC2两者中的电压较大者供电,当VCC2大于VCC1+0.2V时,VCC2给DS1302供电,当VCC2小于VCC1时,DS1302由VCC1供电。X1、X2为振荡源,外接32.768kHz晶振。RST是复位/片选线,通过把RST输入驱动置高电平来启动所有的数据传送。RST输入有两种功能:1、RST接通控制逻辑,允许地址/命令序列送入移位寄存器;2、RST提供了终止单字节或多字节数据的的传送手段,当RST为高电平时,所有的数据传送被初始化,允许对DS1302进行操作。如果在传送工程中置RST为低电平,则会终止此次数据传送,并且I/O引脚为高阻态。上电运行时,在 VCC≥2.5V之前,RST必须保持低电平。

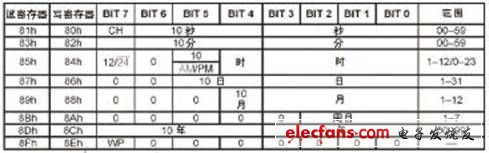

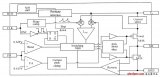

DS1302的控制字如图2所示,字节的最高位(第7位)必须是逻辑1,如为0则不能报数据写入到DS1302,位6如为0,则表示存取日历时钟数据,为1表示存取RAM数据;为5为至位1指示操作单元的地址,最低位(第0位)为0则表示要进行写操作,为1表示进行读操作,控制字节是从最低未开始输出。在控制指令字输入后的下一个SCLK时钟的上升沿时数据写入DS1302,数据输入从低位开始,同样,在紧跟8位控制指令字后的下一个SCLK脉冲的下降沿读出DS1302的数据,读出数据是从低位至高位。

DS1302共有12个寄存器,其中7个寄存器与日历、时钟相关,存放的数据位为BCD码形式,其日历、时间寄存器如图3所示。 DS1302还有年份寄存器、充电寄存器、时钟突发寄存器与RAM等相关寄存器。时钟突发寄存器可一次性顺序读写充电寄存器外的所有寄存器内容。DS1302与RAM相关的寄存器分为两类,一类是单个RAM单元,共31个,每个单元组态为一个8位的字节,其命令控制字为C0H~FDH,其中奇数为读操作,偶数为写操作;另一类为突发方式下的RAM寄存器,此方式下可以一次性读写所有RAM的31个字节,命令控制字地址写操作时为FEH,读操作时为FFH。

图2 DS1320命令控制字

图3 DS1320时钟、日历寄存器及控制字

系统软件实现

主程序流程

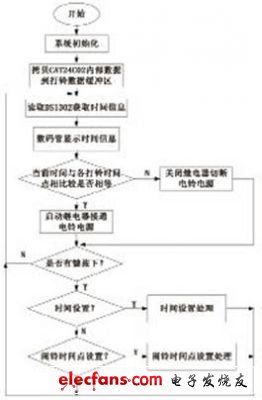

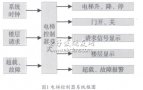

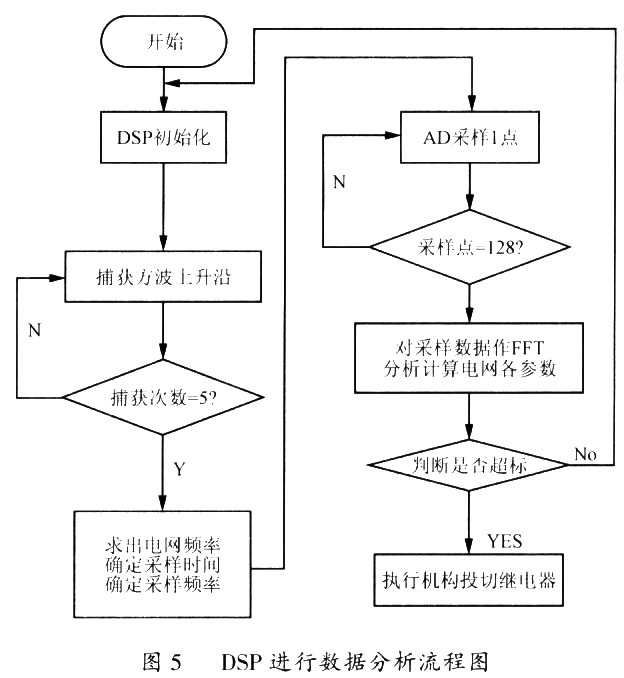

本系统主程序在考虑可设置每天最多40个打铃时间点,而时间点精确的分钟,因此每个时间点信息包括时、分两个字节存储,共需80字节作为打铃时间点存储缓冲区,此缓冲区在AT89C52内存中采用数组的形式定义,同时当打铃时间点设置好时,将此数据保存到CAT24WC02串行芯片中以防止掉电丢失,在下次启动首先从CAT24WC02芯片中读取数据保存到对应数据缓冲区中。运行主程序是首先读取时钟芯片时间数据并在数码管显示相关信息,随后将当前时间与各打铃时间点相比较看是否需要打铃,最后进行键盘信息处理,分别完成时间设定和打铃时间点设定等相关操作,具体流程如图4所示。

图4 主程序流程图

闹铃时间设置程序设计

本设计中共采用8个按键,其中时间设置按键和闹铃设置按键为复用键,由图4可知当运行主程序时,按下相应键则程序进入时间设置或闹铃时间设置程序处理中,在闹铃时间设置程序中,此二键亦分别用于添加闹铃和删除闹铃设置,当6位数码管显示信息均处于闪烁状态时,此时按下添加键,则表示新添加一闹铃时间点,按下删除键则表示删除对应闹铃时间点,如6位数码管显示信息不全闪烁,则此二键不起作用。左移和右移按键则分别用来选择所要设置数据位(时或分),选择对应位后相应数据进入闪烁状态,此时操作增加或减小键进入相应数值设置,当仅闹铃时间序号闪烁时,增加和减小键同时有依次进行查询所有闹铃时间点的功能。信息设置完后当按下确认键则表示信息设置完成,此时所设置闹铃信息会统一进行从小到大排序(用于查询时从小到大显示),然后分别保存到单片机相应内存和CAT24WC02串行EEPROM中以防掉电丢失。如按下取消键,则表示放弃所设置信息,此时重新从CAT24WC02串行EEPROM中读取原闹铃时间信息到单片机相应内存相应缓冲区。具体流程图如图5所示。

图5 主程序流程图

闹铃时间信息显示程序则由显示程序void Display专门负责,闹铃设置时的数据分别放在临时显示缓冲区,结合其闪烁状态值一起传递给显示程序进一步处理,从而决定哪位数码管显示信息进行闪烁,闪烁状态值FlagBit共有5个取值参数,分别为0、1、2、3、4,其中0表示不闪烁, 1表示闹铃时间分值闪烁,2表示闹铃时间时值闪烁,3表示闹铃时间序号闪烁,4表示全部显示数值一起闪烁。具体闪烁控制则由定时中断服务程序里对闪烁标志不断取反,显示程序里根据此标志位的变化进行闪烁控制。

时间设置处理程序则主要是通过按键设置好时间后对DS1302进行数据更新, 具体过程与闹铃设置程序类似,篇幅原因不在多述。

结语

实验初期本设计主要通过仿真软件完成,由于受实验条件影响,数码管显示部分采用静态显示方法完成,如考虑节约成本,在实际电路中本设计亦可采用动态显示电路或串行显示电路完成。

电子发烧友App

电子发烧友App

评论