相关器单元

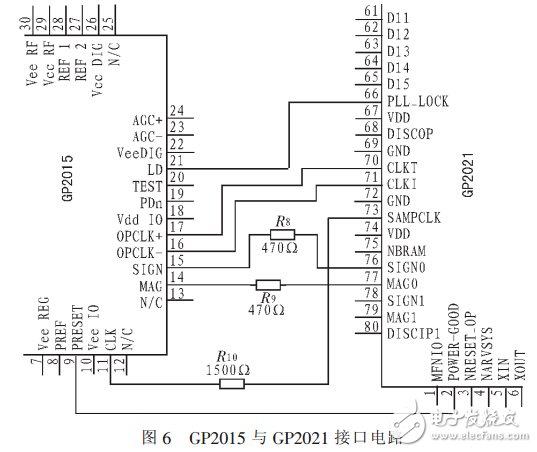

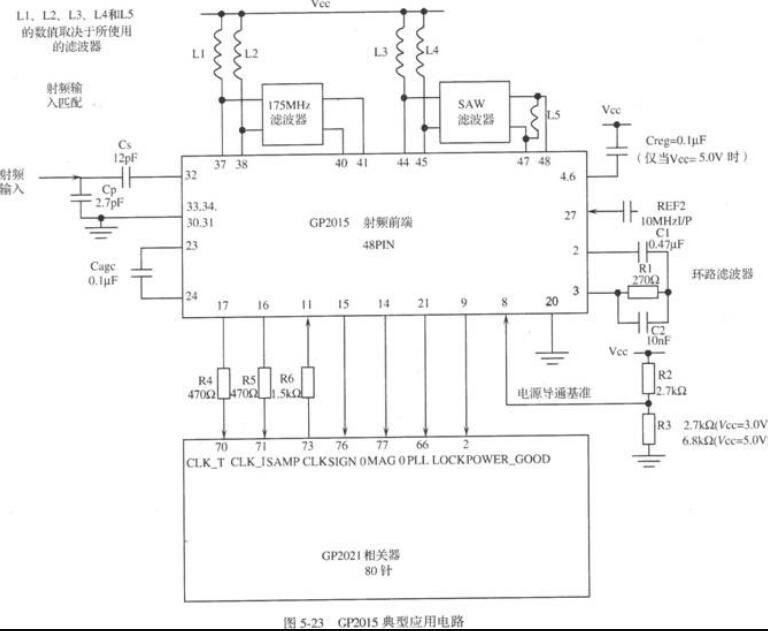

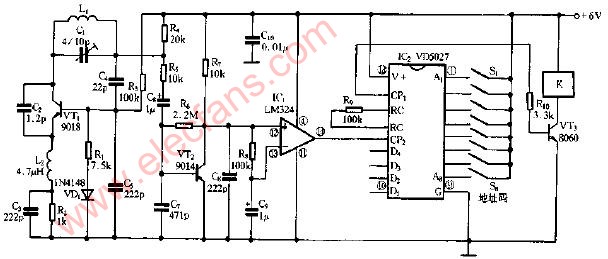

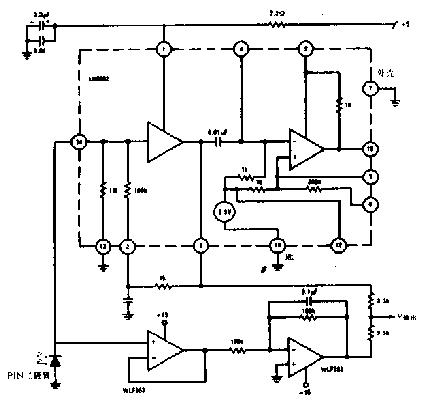

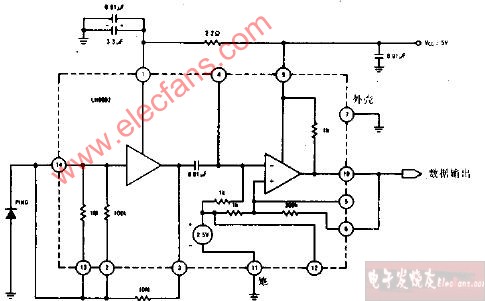

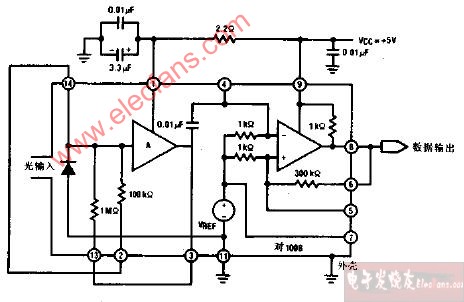

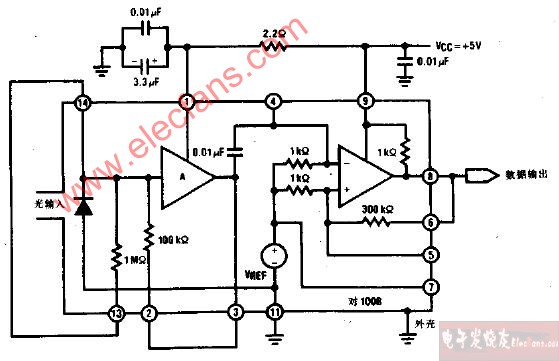

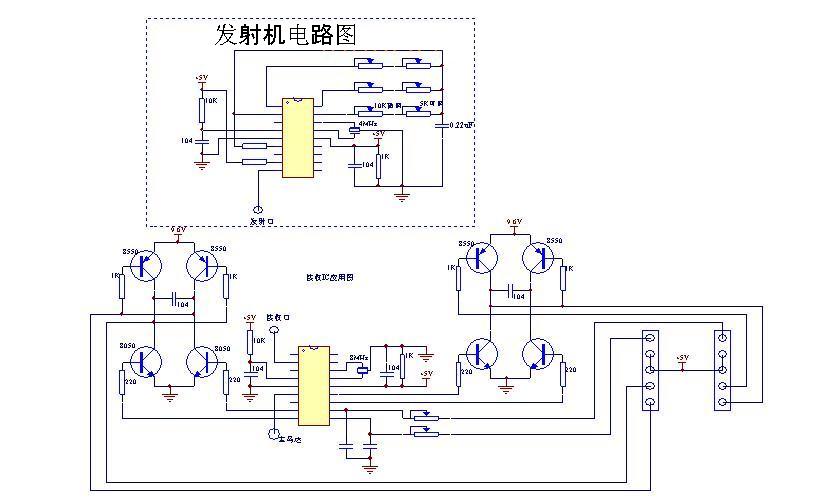

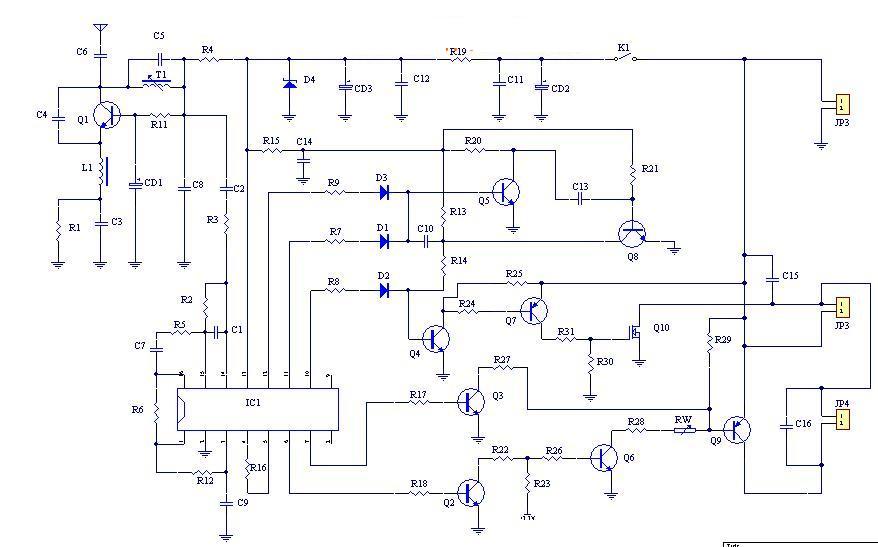

对于与GP2015的组合匹配电路,GP2021接收来自GP2015的40MHz的差分时钟信号、MAGO、SIGO 、PLLRDY和PRESET信号。将GP2015和GP2021的差分时钟引脚直接相连;MAGO、SIGO及CLK采用串联端接电阻,减少信号的反射。设计GP2015与GP2021接口电路原理图如图6所示。

微控制器单元

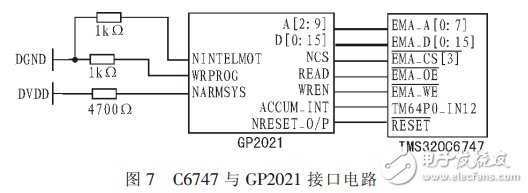

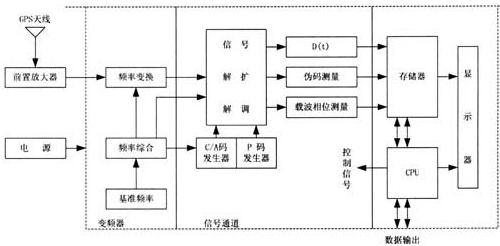

选用TMS320C6747对GP2021进行读操作和写操作,获取导航数据及控制GP2021的信号捕获和跟踪过程。GP2021提供了多种标准接口方式与C6747进行通信,包括ARM6、Motorola、 Intel486 、Intel80186的接口,接口的配置取决于GP2021片上标号为NARMSYS,WRPROG及NINTELMOT的引脚高低电平的组合逻辑,如表1所示。

可以将GP2021等价为异步随机存储器,采用C6747的外部存储器接口EMIFA与GP2021进行匹配。C6747的EMIFA接口包含3根控制线,13根地址线,16根数据线。将EMIFA的片选EMA_CS [3]与NCS相连,它的地址空间为0x62000000-0x63FFFFFF。EMIFA中其他的引脚就按功能进行相连。由于GP2021与C6747的地址总线、数据总线和控制总线的引脚都支持LVTTL,所以无需电平转换就可直接相连,不会出现逻辑错误。通过设置C6747中EMIFA接口片选信号EMA_CS的READ_SETUP、READ_STROBE、READ_HOLD、WRITE_SETUP、WRITE_STROBE、TA、WRITE_HOLD的时间就可以实现与GP2021数据传输。

另外GP2021中ACCUM_INT引脚输出一个间隔505.05us的信号,保证GP2021与C6747之间的接口正常传输。C6747内增强型的TIMER定时器具有通过TIMER外部时钟输入引脚捕获外部输入事件的功能。由此将TIMER的时钟输入引脚直接与ACCUM_INT相连。所以C6747与GP2021接口电路如图7所示。

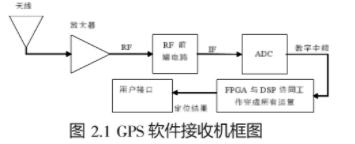

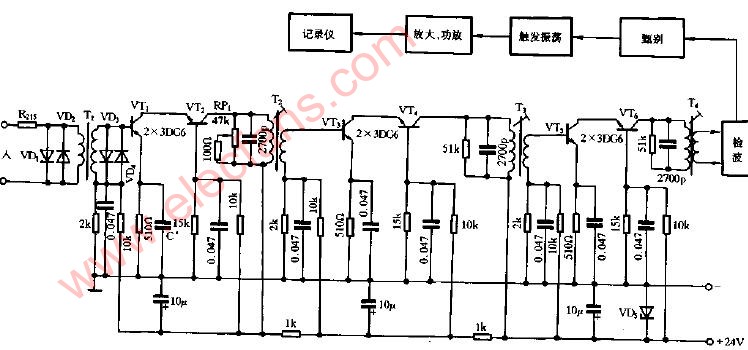

编辑点评:本设计经过单片机控制超声波谐振电路的频率和负载功率,结合GPS接收机硬件和软件进行了导航电文译码测试,成功地实现了对GPS卫星的捕获和跟踪。以GP2015、GP2021芯片组为核心架构,以C6747为相关计算处理器的GPS硬件电路设计,充分考虑了低功耗、高性能及小封装的弹载环境要求;以常用信号捕获算法为基础,给出了GPS定位软件的核心流程框图。

电子发烧友App

电子发烧友App

评论