本文为大家带来五种三人表决器电路设计方案,包括两款仿真电路及程序分析,三款逻辑电路设计的原理详解。

三人表决器电路设计方案一:VHDl的三人表决器电路设计

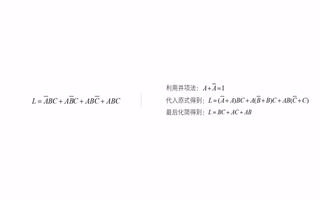

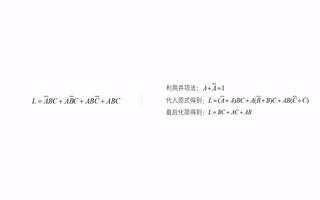

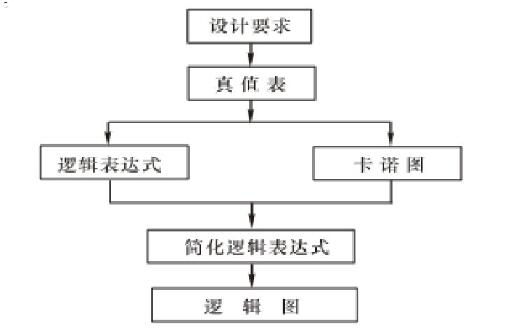

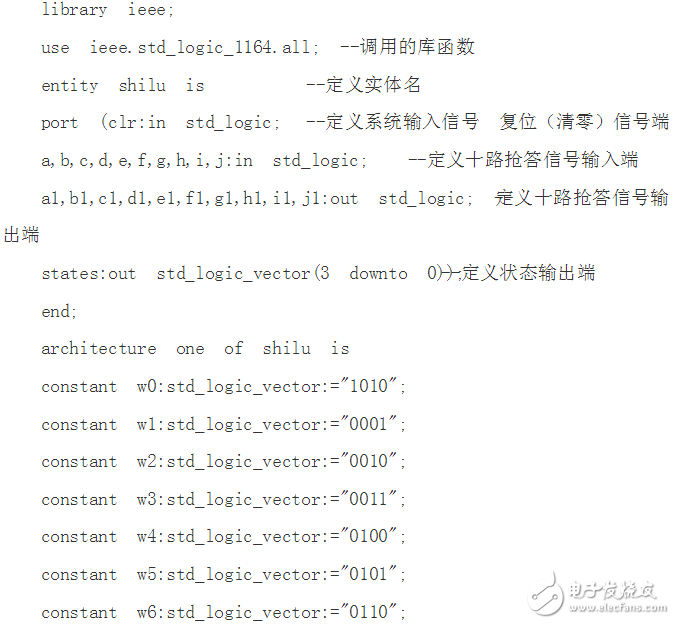

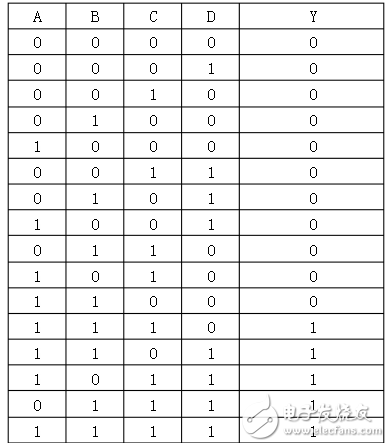

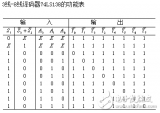

三人表决电路中,当表决某提案时,多数人同意,则提案通过,同时有一个人具有否决权,若全票否决,也给出显示。设输入为A,B,C,且A具有否决权,同意用1表示,不同意用0表示,输出X为1时表示提案通过,Y为1时表示提案全票否决,真值表如下:

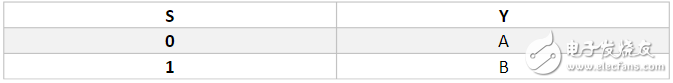

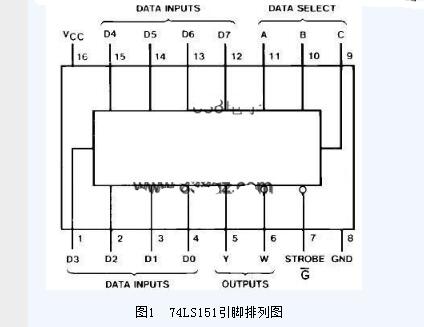

多路选择器实验中,2选1多路选择器能在选择信号的控制下,从2路输入信号中选择其中的一路数据,送到输出口,真值表如下:

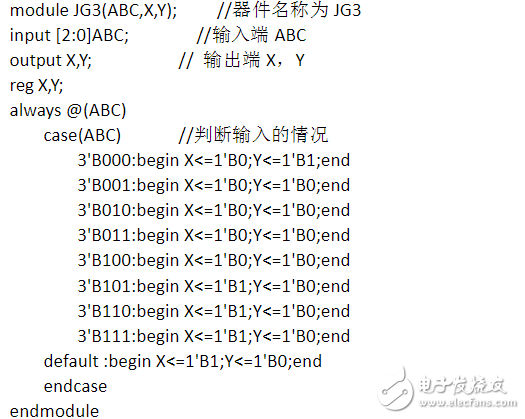

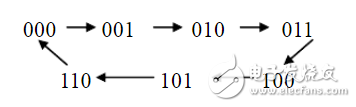

程序设计

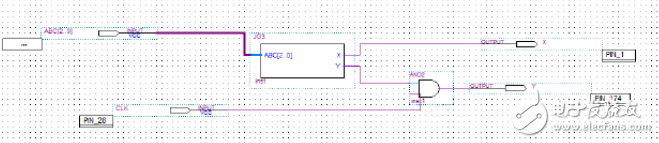

原理图

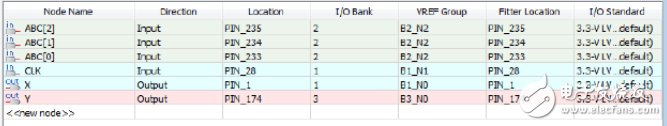

引脚锁定

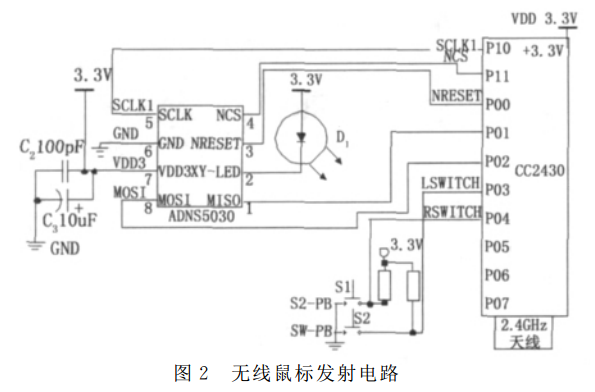

ABC[0]接键1,引脚号为pin233,ABC[1]接键2,引脚号为pin234,ABC[2]接键3,引脚号为pin235,CLK接clock0,引脚号为pin28,表决结果X接发光管D1,引脚号为pin1,Y接扬声器,引脚号pin174

仿真

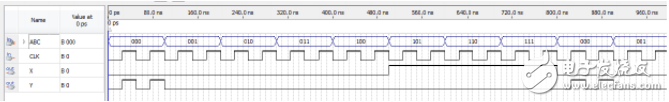

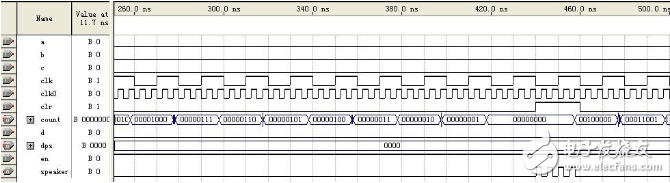

设置整个仿真域的时间为1us,ABC的周期为100ns,CLK的周期为25ns,仿真波形如下

由仿真波形图看出, 如果A为0,X一定为0,同时ABC多数为1时,X为1,并且当ABC三个都为0时,Y为1,符合三人表决电路要求。

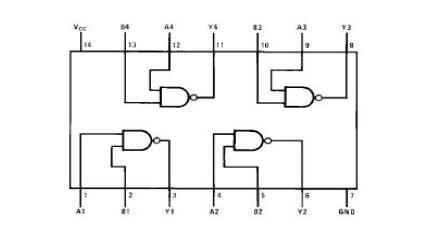

三人表决器电路设计方案二:基于74LS00的三人表决器电路设计

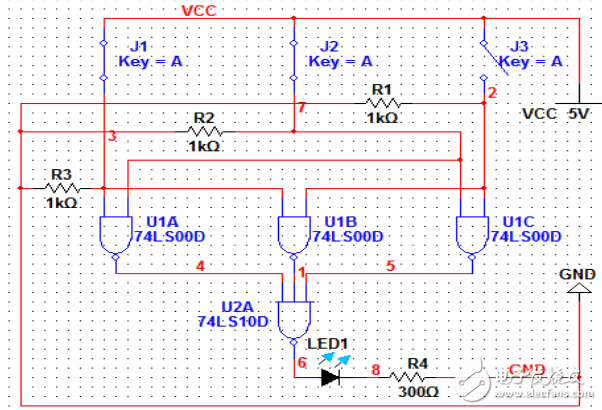

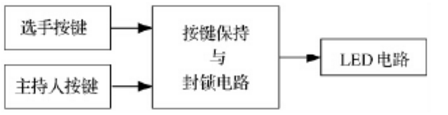

我们用发光二极管的状态来表示表决结果通过与否,当发光二级管点亮表示表决结果通过,熄灭表示表决结果不通过。三人A、B、C的表决情况用按钮来实现,按下按钮表示同意,不按表示不同意。

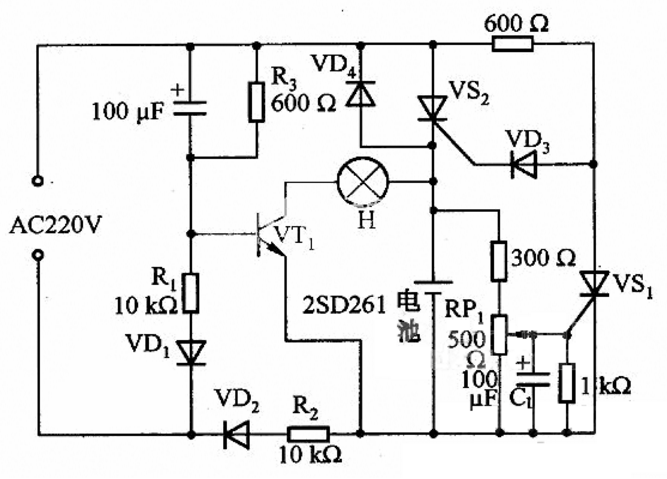

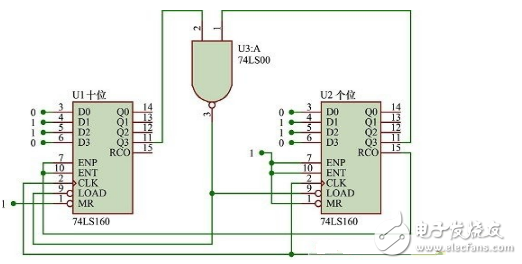

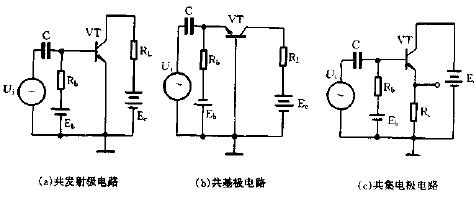

根据上述说明,结合前面的逻辑电路,可得到三人表决器的原理图为:

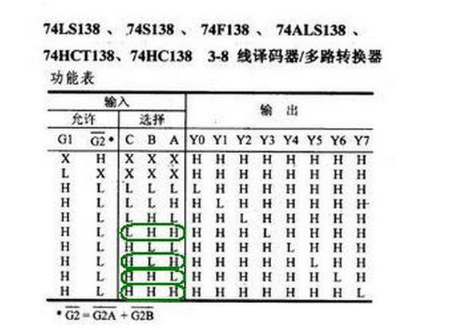

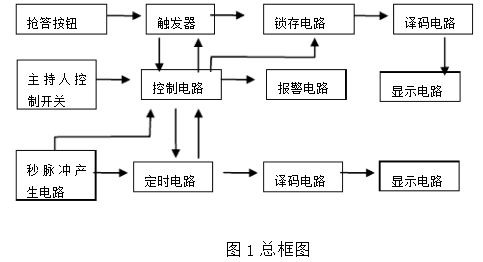

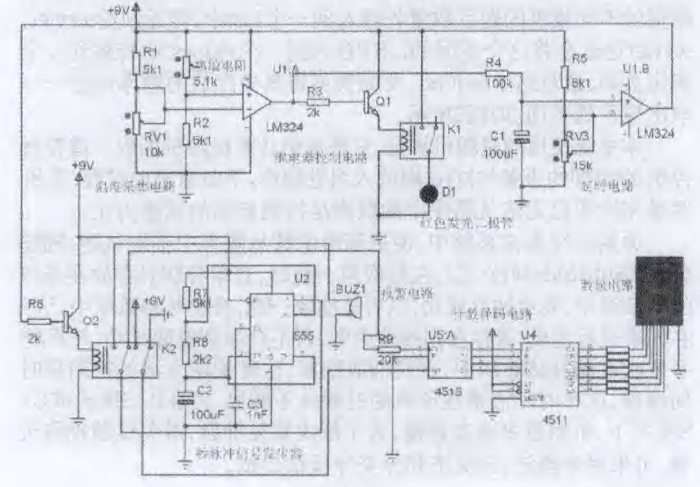

三人表决器电路设计方案三:74ls138和74ls20设计的三人表决器设计

详细电路设计方案:74ls138和74ls20设计的三人表决器

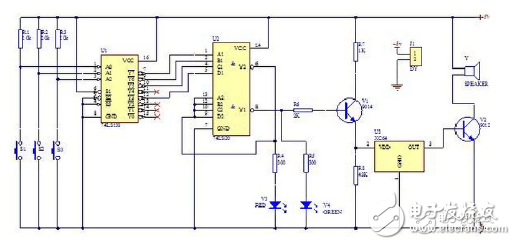

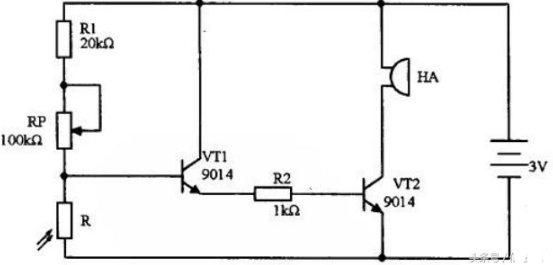

三人表决器主要由一个3-8位译码器(74LS138)和2个4输入与非门(74LS20)组成。通过三个按钮接受用户输入。按钮按下表示同意,不按下表是否决,当没有人按下按钮时,或只有一个人按下按钮时,例如,S1按下,而S2和S0未按下,则红灯亮,绿灯灭,蜂鸣器无声音,表示否决,当有两个人及以上的人按下按钮后,例如,S1和S2按下,则红灯灭,绿灯亮,蜂鸣器发音,表示通过。运用74LS138译码器和四输入与非门74LS20实现该逻辑功能。

电子发烧友App

电子发烧友App

评论