FET场效应管,Field Effect Transistor,包括结型和MOS管。

在初学的时候,非常容易和三极管混淆。三极管一般老师都会花大量的篇幅介绍,所以学生们相对熟悉。(因为是考试的重点)

反而FET管子,老师往往在模拟电子电路中一带而过,模棱两可。最后连管子符号都难以认全。

所以,本文总2句口诀,帮助记忆FET管,并介绍了FET的原理。

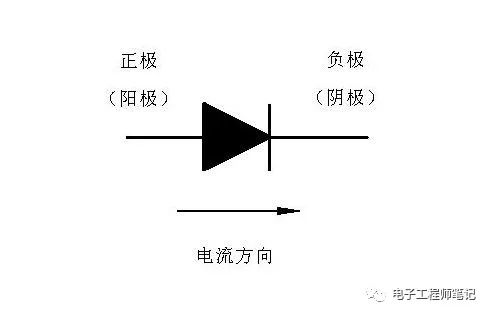

二极管我们都很熟悉,从P区到N区,我们称之为正向导通,如果我们把这种正向,用箭头表示,那就是P指向N,P→N。

一般的半导体符号,箭头的方向都是从P指向N,我们可以利用这一点,帮助我们记忆。

图2 二极管的符号与正向

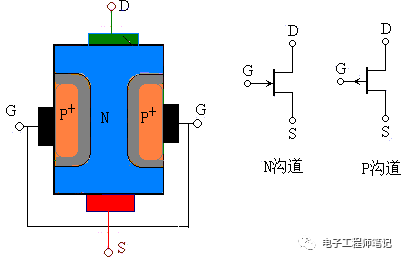

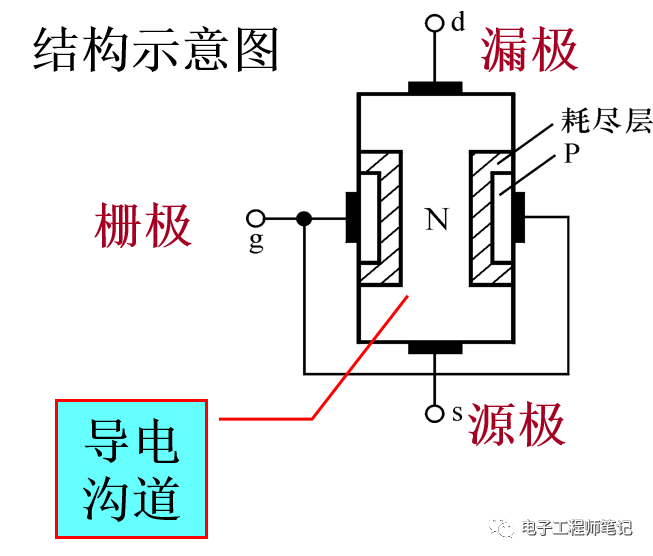

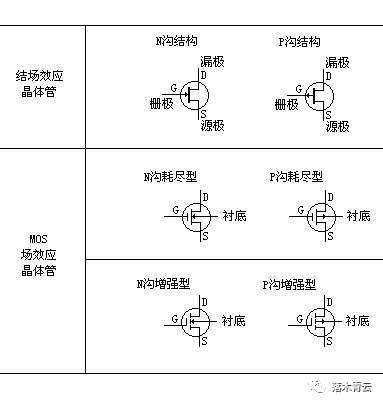

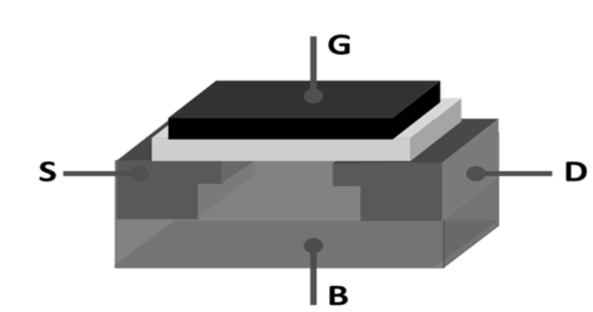

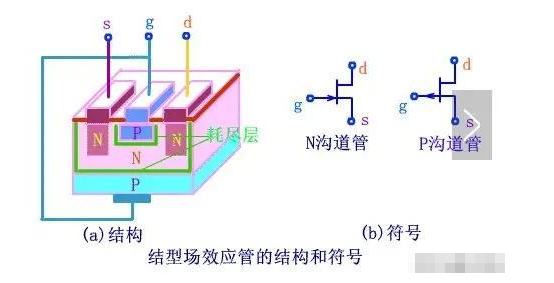

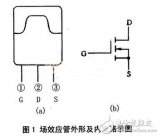

我们先来看下结型场效应管JFET,Junction FET的结构和符号:

图3 JFET的结构与符号

图3中,在同一块N型半导体上制作两个高摻杂的P区(橙色),并将它们连接在一起,引出的电极称之为栅极g,N型半导体的两端分别引出两个电极,一个称为漏极d,一个称为源极s。P区与N区交界面形成耗尽层(灰色),漏极与源极间的非耗尽层区域(蓝色)称为导电沟道。

所以,N沟通的符号就很好理解了:D为漏极,S为源极,G为栅极。箭头为什么向里,因为从P指向N。

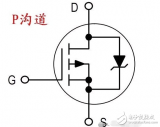

这也适用于MOS管。

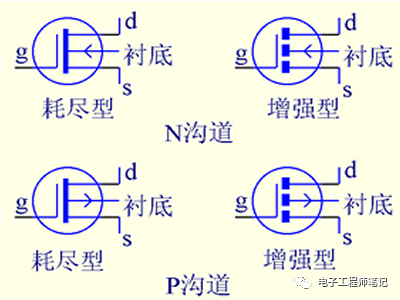

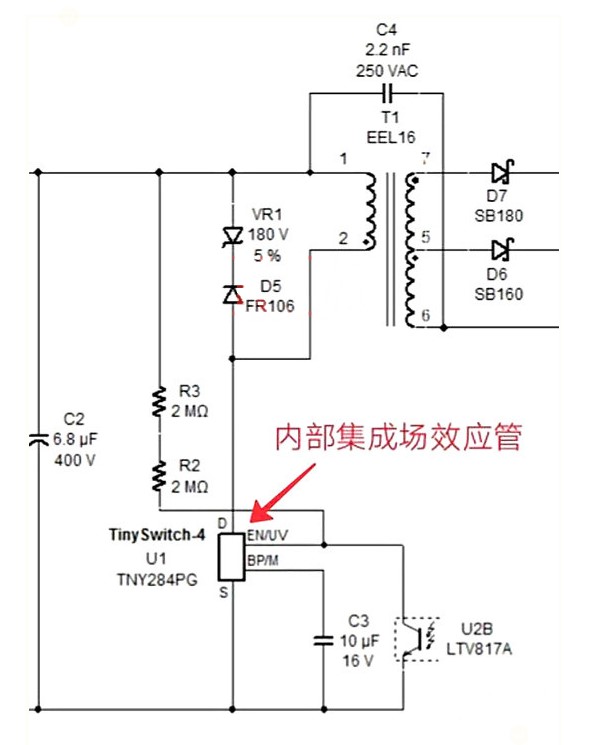

图4 MOS管的四种类型

我们的口诀就是:

箭头向里,指向N,N沟道场效应管;

箭头向外,指向N,P沟道场效应管;

FET的特点

场效应晶体管,是一种电压控制的、三端子、单极半导体器件,有N通道和P通道。

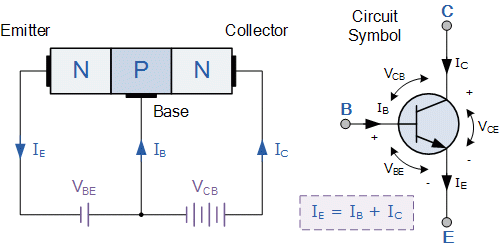

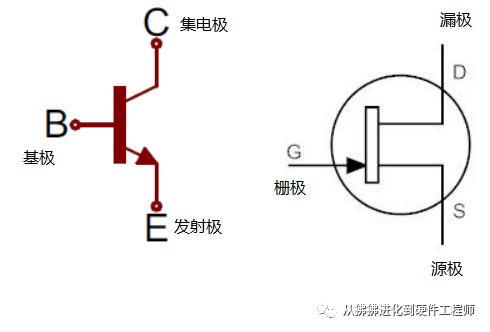

图5 三极管的特性

在双极性晶体管中,我们看到晶体管的输出集电极电流Ic与输入电流IB成正比,输入电流流入器件的基极端,从而使双极性晶体管成为"电流"控制的器件(β模型),因为较小的电流可以用来控制较大电流。

场效应晶体管,其输入端子的电压,称为栅极电压Vgs,控制流过它们的电流,从而使输出电流与输入电压成正比。由于它们的工作依赖于输入栅极电压产生的电场(因此称为场效应),这就使场效应晶体管成为"电压"操作器件。

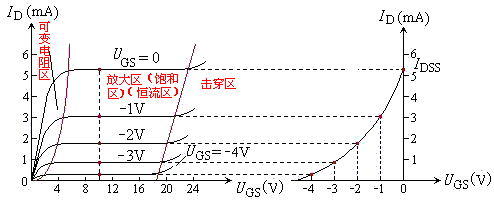

图6 N沟通JFET的输出特性曲线

与标准双极晶体管相比,场效应晶体管有一个主要的优点,即它们的输入阻抗(Rin)很高,而BJT相对较低。这种非常高的输入阻抗使它们对输入电压信号非常敏感,但是这种高灵敏度的特性也意味着它们很容易被静电破坏。

有两种主要类型的场效应晶体管,结型场效应晶体管JFET和绝缘栅场效应晶体管或IGFET,更普遍地称为标准金属氧化物半导体场效应晶体管或MOSFET。

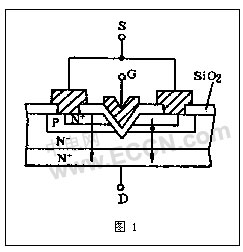

结型场效应管JFET

结型场效应晶体管(JFET)是具有形成N型或P型"通道"的高电阻率半导体材料,多数载流子在被称为漏极和源极之间流动。

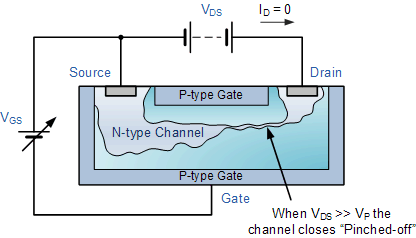

图7 JFET的结构示意图

结型场效应晶体管有N沟道JFET和P沟道JFET。

N沟道JFET的沟道掺杂为施主杂质,这意味着通过沟道流动的是电子。

同样地,P沟道JFET的沟道掺杂为受体杂质,这意味着流过沟道是空穴。

由于电子与空穴相比具有更高的迁移率,所以N沟道JFET的沟道电导率(较低电阻)大于它们的等效P沟道类型。

这使得N沟道JFET与它们的P沟道对应器件相比,是更有效的导体。

在该沟道内存在称为栅极端子的第三极连接,并且这也可以是与主通道形成PN结的P型或N型材料。

与三极管的比较

结型场效应晶体管的半导体"通道",是电压Vds引起电流Id流动的电阻性路径,因此结场效应晶体管在任一方向上都能同样良好地传导电流(漏极和源极基本可以互换)。

由于沟道在本质上是电阻的,因此,当我们从漏极端子到源端时,电位逐渐变小,沿着通道的长度形成电压梯度。

图8 等效电阻

结果表明,PN结在漏极端具有较高的反向偏置,在源端具有较低的反向偏压。这种偏置导致沟道内形成"耗尽层",其宽度随偏压而增大。

图9 栅极电压对漏极电流的影响

流经漏极和源端子中的电流大小由施加在栅极端子上的电压控制,该电压是反向偏置的。在N通道JFET中,此栅电压为负值,而对于P通道JFET则为正栅极电压。

JFET与双极晶体管器件之间的主要差别在于,当JFET结反向偏置时,栅极电流实际上为零,而双极结型晶体管的基极电流总是大于零的值。

N通道JFET的偏置

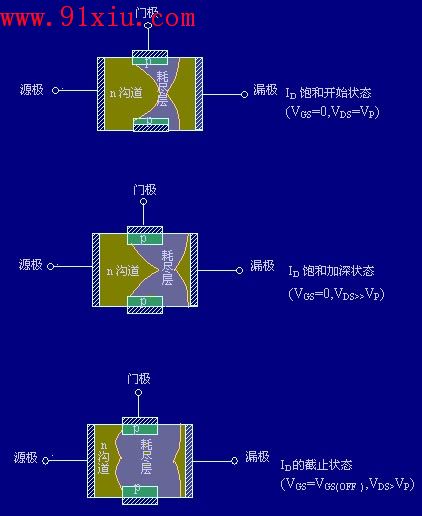

图10 沟道的夹断

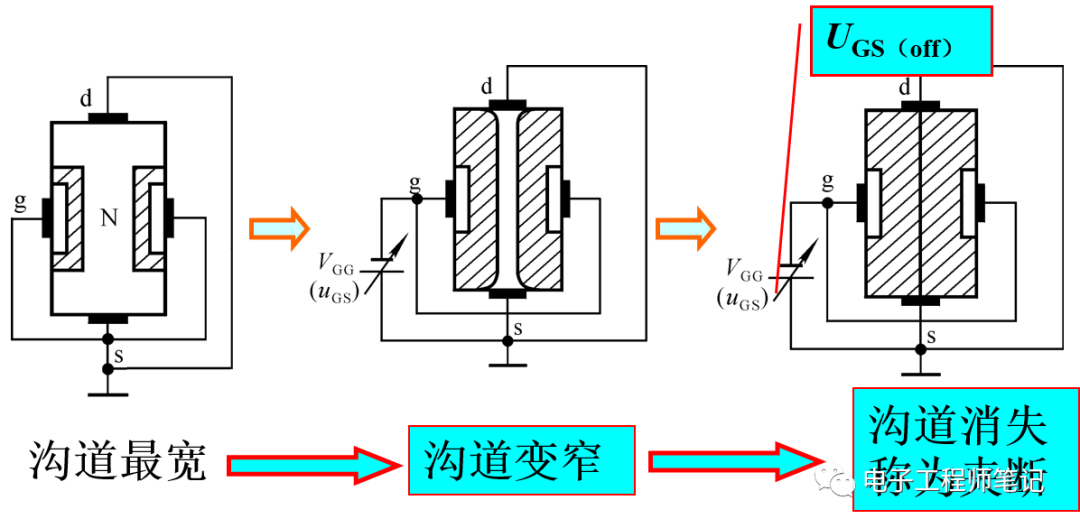

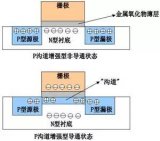

如果现在向栅极施加小的负电压(Vgs),耗尽区的尺寸开始增加减小沟道的总有效面积,从而减小流过它的电流,发生了一种"压榨"效应。

因此,通过施加反向偏置电压增加了耗尽区的宽度,这又减小了沟道的导通。

由于PN结是反向偏置的,所以很少的电流会流入栅极。

当栅极电压(Vgs)变得更负时,沟道的宽度会减小,直到漏极与源和场效应管之间不再有电流流动为止。

通道关闭的电压称为"关断电压",VGSoff。

那么,如果Vgs处于VGSoff~0V之间的一个固定值,若此时Vds=0V,则虽然存在由Vgs所确定的一定宽度的导电沟通,但由于d-s之间电压为零,多字不会产生定向移动,因而漏极电流iD为零。

若Vds>0,则有电流iD从漏极流向源极,从而使沟道中各点与栅极间的电压不再相等,而是沿沟道从源极到漏极逐渐增大,造成漏极一遍的耗尽层比靠近源极一边的宽。

也就是说,靠近漏极一边的导电通道比靠近源极一边的窄,见图9。

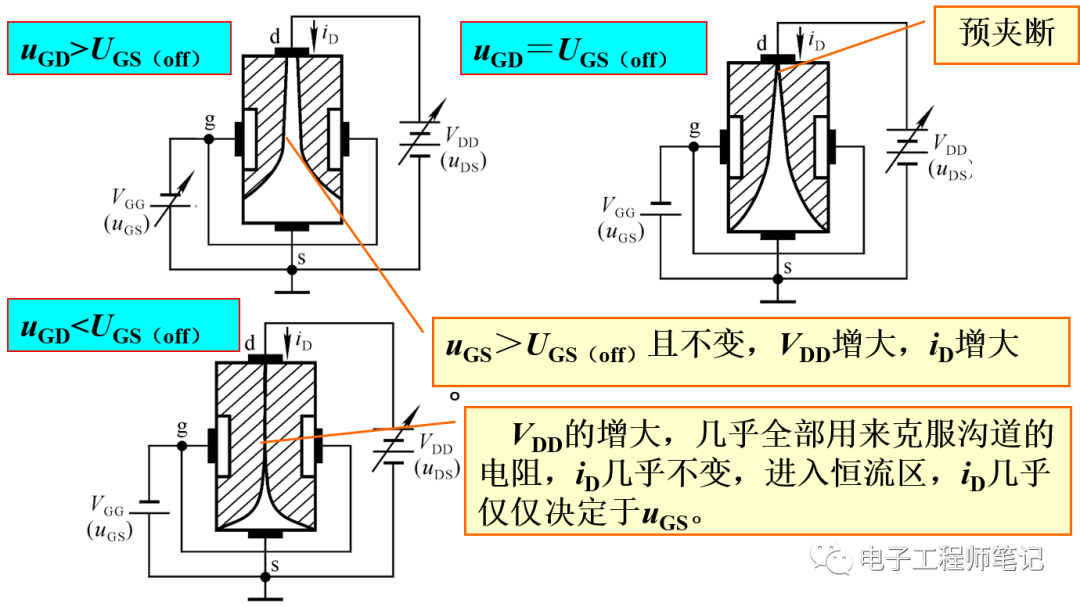

JFET通道预夹断

考虑栅极-漏极之间的电压VGD

VGD = VGS - VDS

所以当VDS从零逐渐增大使,VGD逐渐减小(负值的不断减少,绝对值是不断变大),靠近漏极一遍的导电沟道必将随之变窄。

但是,只要栅极-漏极间不出现夹断区域,沟道电阻仍将基本上决定于栅-源电压VGS,因此电流iD将随VDS增大而线性增大,d-s呈现电阻特性。

而一旦VDS的增大是的VGD等于夹断电压了,那么漏极一边就会出现夹断区。

图11 预夹断

如图9所示。

此时VGD=VGSoff为预夹断。

若VDS继续增大,则VGD

见图9。

此时,一方面自由电子从漏极向源极定向移动所受阻力加大(只能从夹断区的窄缝以较高的速度通过),从而导致iD减小;另一方面,随着Vds的增大,使d-s间的纵向电池增强,也必然导致iD增大。

实际上,上述iD的两种变化趋势相抵消,Vds的增大几乎全部降落在夹断区,用于克服夹断区对iD形成的阻力。

因此从外部看,在VGD

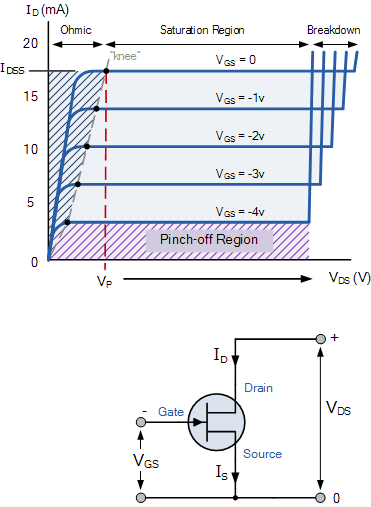

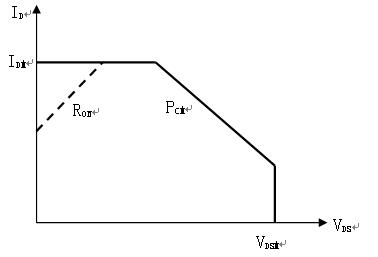

N-JFET的输出特性如下:

图12 输出特性曲线

施加到栅极的电压Vgs控制在漏极和源极端子之间流动的电流。

Vgs是指施加在栅极和源极之间的电压,而Vds指的是施加在漏极和源极之间的电压。

从设备流出的源电流(Is)等于流入它的漏电流,因此(id=is)。

上面显示的特征曲线示例显示了一个JFET的四个不同操作区域,这些区域如下:

可变电阻区域:

当Vgd>VGSoff时,直线的斜率也唯一地被确定,直线斜率的倒数为d-s之间的等效电阻。在此区域内,可以通过改变Vgs的大小来改变漏-源等效电阻的阻值。沟道的耗尽层非常小,JFET用作电压控制电阻器。

截止区域(夹断区域):

当Vgs比VGSoff还要小时,导电沟通被夹断,iD≈0。一般将使iD等于某一个很小电流(5μA)时的Vgs定义为夹断电压VGSoff。

恒流区(饱和区):

JFET成为良好的导体,由栅极-源极电压(Vgs)控制,而漏极-源极电压(Vds)几乎没有或没有影响。

P沟道结场效应晶体管的特性曲线与上述相同,但漏电流id随栅源电压的增加而减小。

对于正常操作,Vgs偏向于介于VGSoff和0之间。

与双极结型晶体管类似,作为三端器件的场效应晶体管能够具有三种不同的操作模式,因此可以在以下配置之一中的电路内连接。

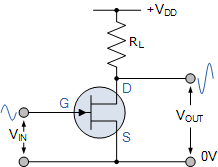

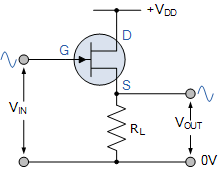

共源电路

图13 共源放大电路

在共源配置(类似于共发射极)电路中,输入被应用于栅极,其输出从漏极中取出,如图13所示。这是场效应晶体管最常见的工作方式,因为它具有高的输入阻抗和良好的电压放大能力,因此,共源放大器得到了广泛的应用。

FET连接的共源模式通常用于音频放大器和高输入阻抗。作为一种放大电路,输出信号为180°"失相"输入。

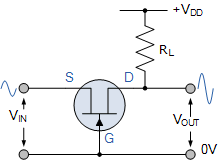

共栅电路

图14 共栅极放大电路

在共栅极结构(类似于共基)电路中,输入被施加到源上,其输出来自漏极,栅极直接连接到地面(0v),如图14所示。由于公共栅极具有较低的输入阻抗,但输出阻抗较高,因此在此配置中失去了先前连接的高输入阻抗特性。

这种类型的FET配置可用于高频电路或阻抗匹配电路中,因为低输入阻抗需要与高输出阻抗相匹配。输出与输入"同相"。

共漏电路

在共漏极配置(类似于共集电极)电路中,输入被应用于栅极,其输出来自源。共用漏极或"源跟随器"结构具有高输入阻抗和低输出阻抗以及接近单位电压增益,因此在缓冲放大器中使用。源跟随器结构的电压增益小于单位,输出信号与输入信号"同相"。

图15 共漏极放大电路

这种类型的配置被称为"公共漏极",因为在漏极连接上没有可用的信号,目前的电压,vdd只是提供了一种偏置。输出与输入同步。

审核编辑:汤梓红

电子发烧友App

电子发烧友App

评论