什么叫OC门?外接上拉电阻值如何确定? 一、什么是OC门 OC门,全称为开漏输出门,是一种电子器件。它通常用于数字电路中,用于连接一个逻辑电路和另一个逻辑电路,同时实现了逻辑电路间的隔离和信号转换

2023-09-12 11:36:32 501

501 数据流的控制和操作。不同于常用的逻辑门电路,OD门和OC门输出端口不需要上拉电阻,这是因为OD门和OC门本身具有固有的上拉功能。下面将分别逐一介绍它们的工作原理及具体应用情况。 1. OD门 OD门,全称Open Drain门,是一种常用于数字电路中的输出控制

2023-09-12 11:18:20 448

448 一、OC门——集电集开路门 1. 基本概念 OC门(Open Collector Gate)是数字电路中的一种逻辑门,它是开集输出门电路,其主要作用是将输入信号通过门电路进行处理,并将结果输出

2023-09-10 09:37:07 787

787

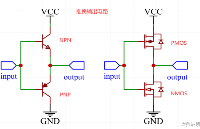

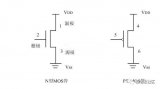

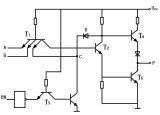

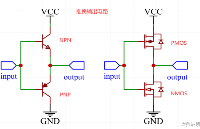

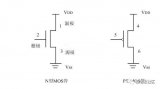

在工作中,会遇到OC门与OD门的称谓。而感性的认识一般为:OD门是采用MOS管搭建的电路,压(电压)控元器件。OC门是采用晶体管搭建的电路,流(电流)控元器件。而OD门的功率损耗一般是小于OC门,为什么?

2023-09-07 10:22:23 278

278 电子设计基础知识,讲一讲OC/OD门,开漏/推挽输出,以及图腾柱 ... 矜辰所致

2023-05-24 10:49:50 1359

1359

NAND门是一个逻辑门,如果其所有输入均为真,则产生低输出(0),否则产生高输出(1)。因此,NAND门是AND门的反面,其电路是通过将AND门连接到NOT门来创建的。NAND门与 AND 门一样,可以有任意数量的输入探头,但只能有一个输出探头。

2023-05-23 15:42:40 3725

3725

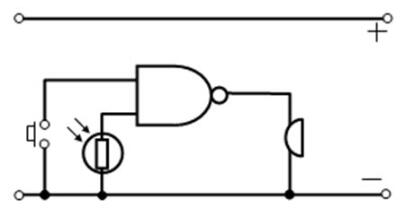

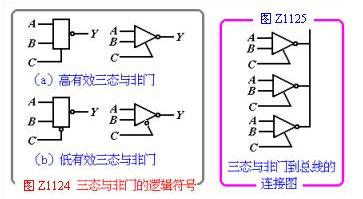

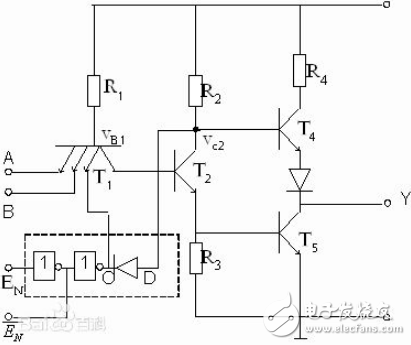

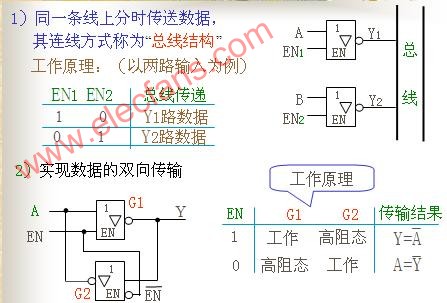

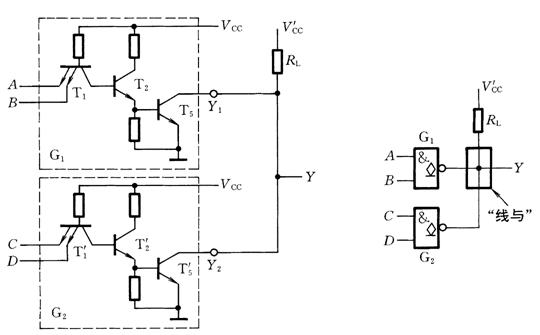

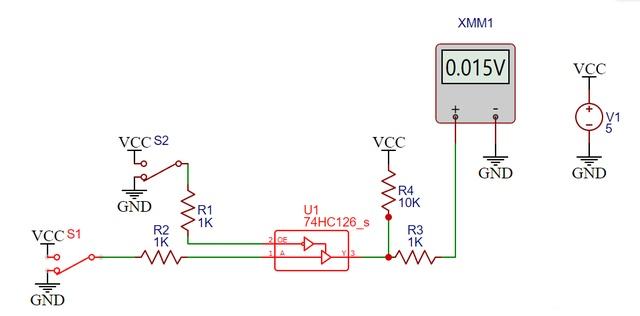

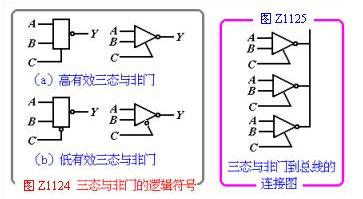

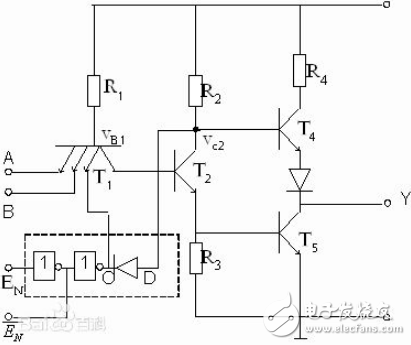

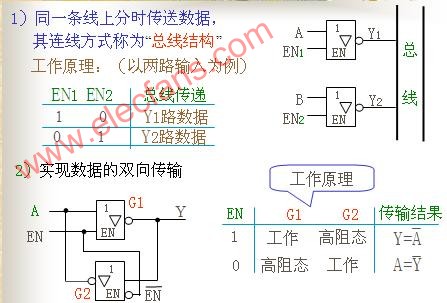

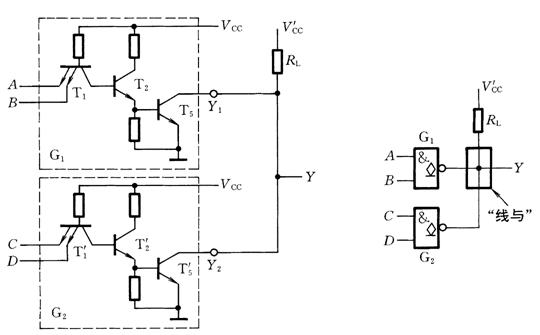

三态门和OC门一、OC门实际使用中,有时需要两个或两个以上与非门的输出端连接在同一条导线上,将这些与非门上的数据(状态)用同一条导线输送出去。因此,需要一种新的与非门电路来实现线与逻辑,这种门电路

2008-05-26 13:01:37

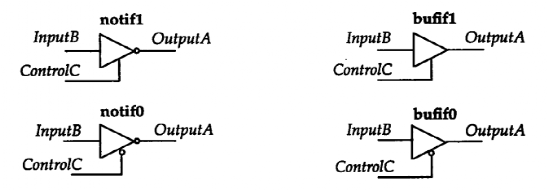

门级建模,是使用基本的逻辑单元,例如与门,与非门等,进行更低级抽象层次上的设计。与行为级建模相比,门级建模更注重硬件的实现方法,即通过连接一些基本门电路去实现多种逻辑功能。虽然行为级建模最后也会被

2023-03-30 11:35:24 2111

2111

这是相对于两个不同的元器件而命名的,OC门是相对于三极管而言,OD门是相对于MOS管。

2023-03-14 16:04:12 4967

4967

超可配置的多功能门;三态-74LVC1G99

2023-02-20 19:45:09 0

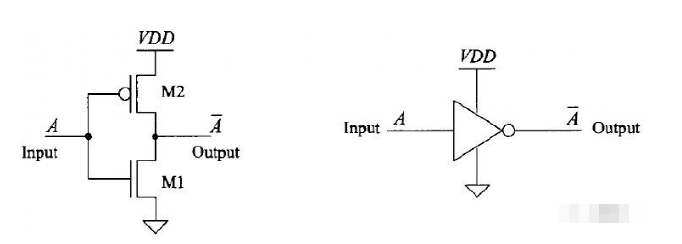

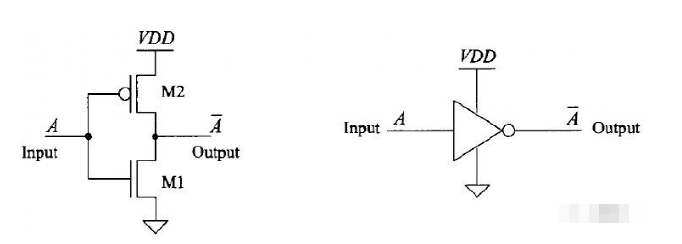

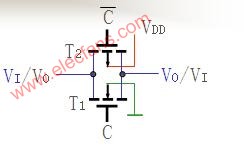

0 反相器是最基本CMOS器件。

2023-01-30 16:22:34 3312

3312

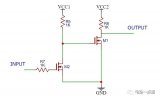

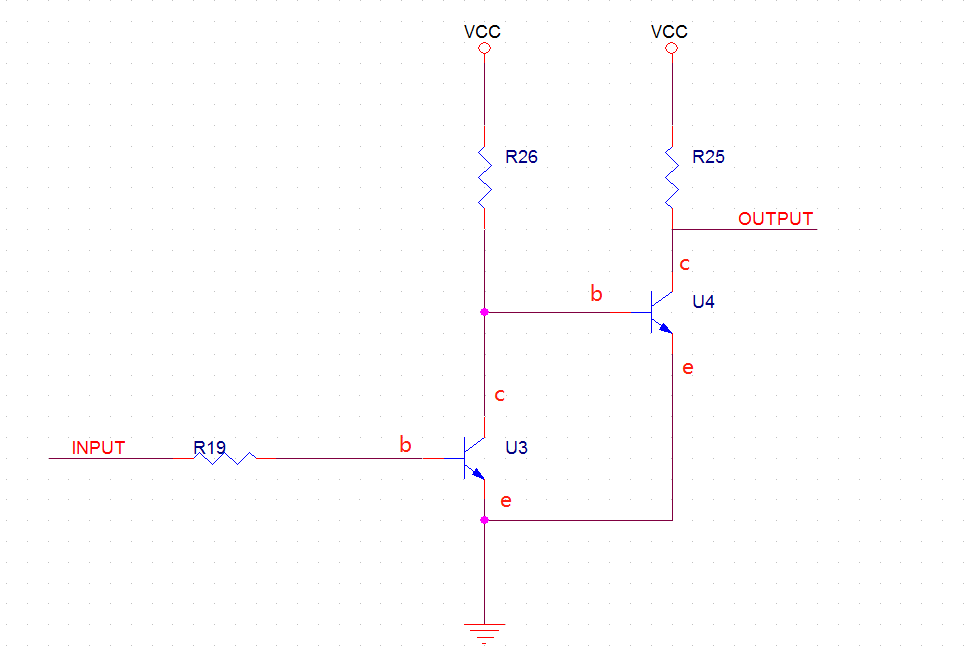

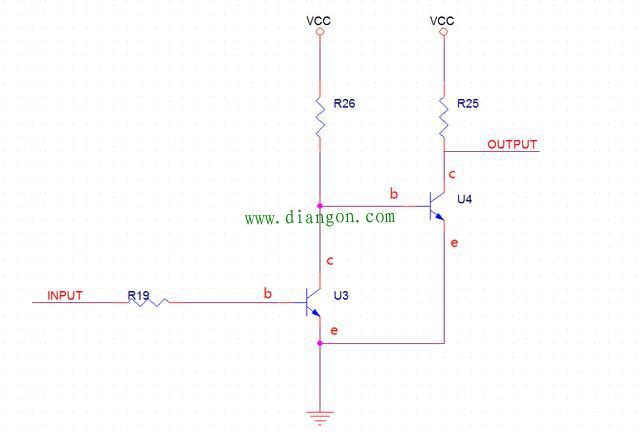

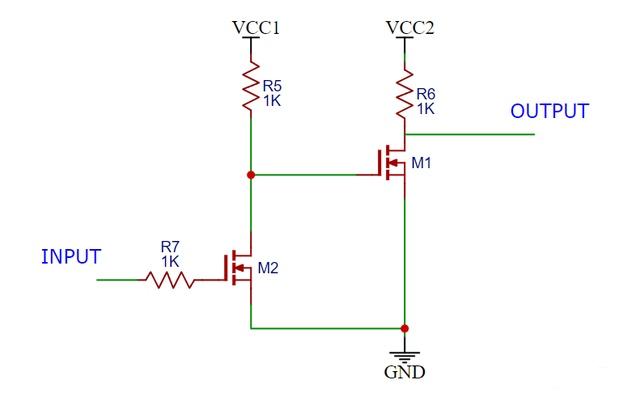

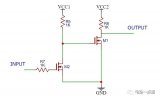

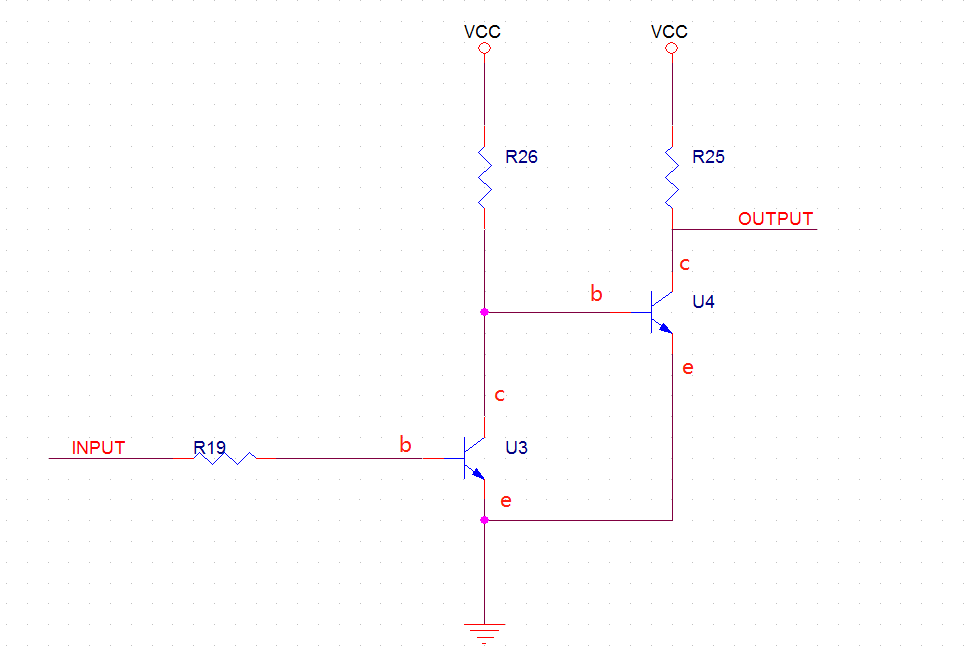

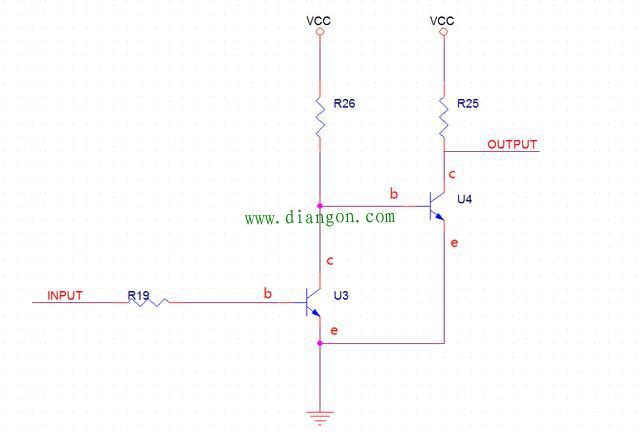

是相对于三极管而言,OD门是相对于MOS管。 我们先来分析下OC门电路的工作原理: 当INPUT输入高电平,Ube0.7V,三极管U3导通,U4的b点电位为0,U4截止,OUTPUT高电平 当INPUT

2022-12-25 10:23:41 1960

1960

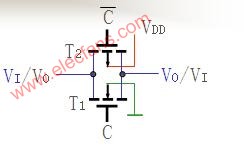

由上图看出,在单相三态门中,当EN=1时,对原电路无影响,电路的输出符合原来电路的所有逻辑关系,即A可以输出到B。当EN= 0时,电路内部的所有输出与外部将处于一种关断状态。

2022-10-20 11:01:02 904

904 OC门,又称集电极开路(漏极开路)与非门门电路,Open Collector(Open Drain)。

2022-08-12 14:36:46 9905

9905 什么是集电极开路(OC)?

我们先来说说集电极开路输出的结构。集电极开路输出的结构如图1所示,右边的那个三极管集电极什么都不接,所以叫做集电极开路(左边的三极管为反相之用,使输入为"0"时,输出也为

2022-02-11 15:22:02 8

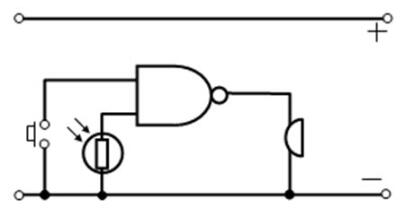

8 门磁开关原理及相关应用文章目录门磁开关原理及相关应用一、门磁开关二、干簧管的工作原理三、门磁报警器一、门磁开关 门磁是用来探测门、窗、抽屉等是否被非法打开或移动。它由无线发射器和磁块两部分

2021-10-22 16:50:59 7

7 文章目录门磁开关原理及相关应用一、门磁开关二、干簧管的工作原理三、门磁报警器PS:相关文档可以去下载:https://download.csdn.net/download

2021-10-22 15:06:05 19

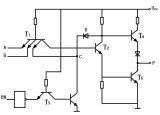

19 c型管4导通,输入端b的电平状况可以通过3、4管到达输出端d。 当控制端a为“0”时,3、4管都停止,输入端b的电平状况无法到达输出端d,输出端d呈现高电阻的状态。 这个器件的三态门带有一定驱动能力,也可称之为带控制端的传输门。 文章整

2021-08-12 11:39:49 10760

10760 电子发烧友网为你提供数字电路常见术语:高阻态,三态门资料下载的电子资料下载,更有其他相关的电路图、源代码、课件教程、中文资料、英文资料、参考设计、用户指南、解决方案等资料,希望可以帮助到广大的电子工程师们。

2021-03-27 08:45:27 13

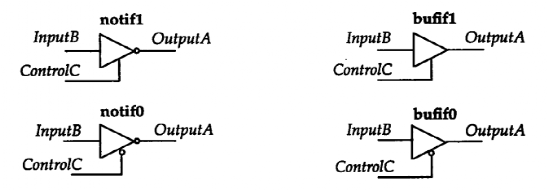

13 入门: and, nand,or, nor, x o r, x n o r 2) 多输出门: buf, not 3) 三态门: bufif0, bufif1, notif0,notif1 4) 上拉

2021-03-05 15:23:12 5320

5320

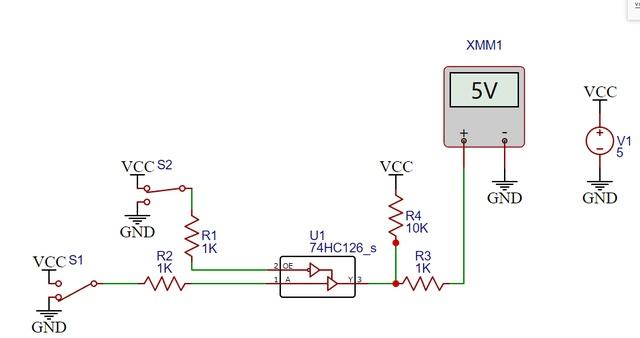

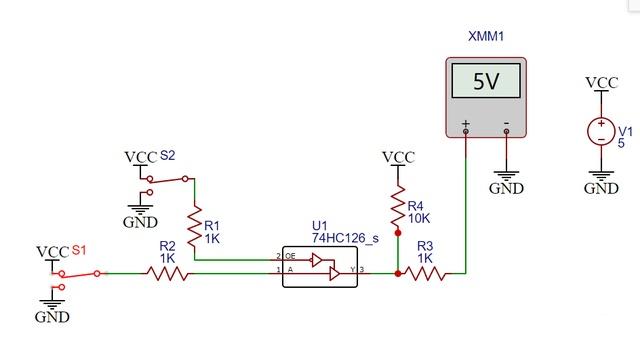

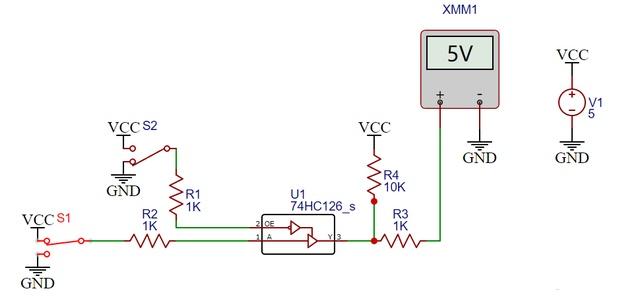

本文档的主要内容详细介绍的是三态门应用的Multisim仿真实例电路图免费下载。

2020-09-23 17:32:00 38

38 Multisim仿真软件进行三态总线电路工作过程波形仿真分析,用环形计数器做实验中的信号源产生所需的各个控制信号、用脉冲信号源产生各数据输入信号,用逻辑分析仪多踪同步显示各个三态门的控制信号、数据输入信号及总线输出信号波形,可直观形象地描述三态门总线传输电路的工作特性。

2020-04-18 12:50:00 6304

6304 三态电路可提供三种不同的输出值:逻辑“0”,逻辑“1”和高阻态。高阻态主要用来将逻辑门同系统的其他部分加以隔离。例如双向I/O电路和共用总线结构中广泛应用三态特性。

2019-11-29 07:09:00 3339

3339 三态电路可提供三种不同的输出值:逻辑“0”,逻辑“1”和高阻态。高阻态主要用来将逻辑门同系统的其他部分加以隔离。例如双向I/O电路和共用总线结构中广泛应用三态特性。

2019-11-21 07:05:00 7465

7465 在数字电路中,所谓“门”就是只能实现基本逻辑关系的电路。最基本的逻辑关系是与、或、非,最基本的逻辑门是与门、或门和非门。逻辑门可以用电阻、电容、二极管、三极管等分立原件构成,成为分立元件门。也可以将门电路的所有器件及连接导线制作在同一块半导体基片上,构成集成逻辑门电路。

2019-11-05 11:28:23 19400

19400

本文档的主要内容详细介绍的是三态门原理HDL语言DSP和ARM总线的仿真及Modelsim使用教程资料主要内容包括了:1 ModelSimSE的使用流程,2 一个Verilog计数器仿真详细流程附

2019-07-09 16:49:27 9

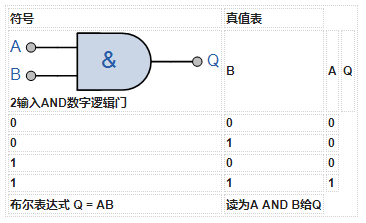

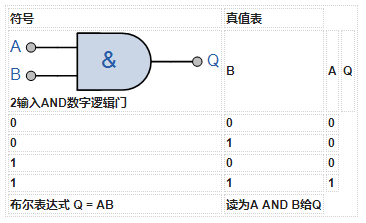

9 和缓冲器是单输入器件,也可以具有三态高阻抗输出,可用于控制数据流到公共数据总线上。下面总结了八个最“标准”的数字逻辑门及其相应的真值表。

2019-06-26 11:49:41 7987

7987

三态门亦称“三态输出门”、“三态门输出电路”。是一种重要的总线接口电路。具有高电平、低电平和高阻抗三种输出状态的门电路。

2019-03-10 09:29:25 15025

15025 三态门主要是用于总线的连接,因为总线只允许同时只有一个使用者。通常在数据总线上接有多个器件,每个器件通过OE/CE之类的信号选通。如器件没有选通的话它就处于高阻态,相当于没有接在总线上,不影响其它器件的工作。

2019-03-08 16:49:37 21630

21630 三态指其输出既可以是一般二值逻辑电路,即正常的高电平(逻辑1)或低电平(逻辑0),又可以保持特有的高阻抗状态,那么三态门输出的三种状态是什么呢?

2019-02-21 16:45:59 66152

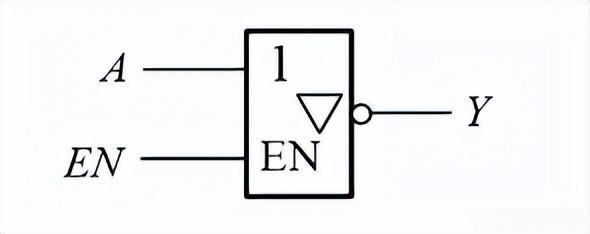

66152 三态缓冲器(Three-state buffer),又称为三态门、三态驱动器,其三态输出受到使能输出端的控制,当使能输出有效时,器件实现正常逻辑状态输出(逻辑0、逻辑1),当使能输入无效时,输出处于高阻状态,即等效于与所连的电路断开。

2018-10-24 16:09:36 32926

32926 三态门,是指逻辑门的输出除有高、低电平两种状态外,还有第三种状态——高阻状态的门电路 高阻态相当于隔断状态。

2018-07-26 10:53:43 29132

29132

TTL、CMOS电平和OC门知识大全

2018-07-15 10:33:00 7222

7222 MOS管构成的缓冲器Buffer和漏极开路们OD门是数字电路非常重要的概念,怎么构成的;

反相器,线与逻辑怎么玩,又怎么用呢?

根据原理图,真值表,应用典型电路全面了解基本的逻辑门,与门,或门,与非门。

半导体SS, TT, FF是怎么回事?

2018-04-29 17:54:00 46613

46613

本文主要介绍了传输门和三态门什么区别,三态门就是指输出有三种状态(0,1,高阻)的门。传输门就是指可以控制通路通断的门,导通时,一端的信号可以传到另一端,不导通时,一端信号不能传到另一端。两者不是

2018-04-08 15:33:49 51792

51792

本文开始介绍了三态门的定义与三态门的应用,其次对三态门的三态及特点进行了介绍,最后阐述了三态输出门电路与三态门电路的图形符号与真值表。

2018-03-01 14:47:41 113066

113066

三态指其输出既可以是一般二值逻辑电路,即正常的高电平(逻辑1)或低电平(逻辑0),又可以保持特有的高阻抗状态。本文开始介绍了三态门的定义,其次介绍了三态门的逻辑符号,最后介绍了三款三态门逻辑电路。

2018-03-01 14:03:10 69342

69342

三态数据缓冲器是数据输入/输出的通道,数据传输的方向取决于控制逻辑对三态门的控制。本文介绍三态缓冲器的逻辑符号。

2018-01-11 10:42:36 13281

13281

低电平,随它后面接的东西定。三态门,是指逻辑门的输出除有高、低电平两种状态外,还有第三种状态——高阻状态的门电路。高阻态相当于隔断状态(电阻很大,相当于开路)。 三态门都有一个EN控制使能端,来控制门电路的通断。 可以具备这三种状态的器件就叫做三态(门,总线,......)。

2017-12-25 11:27:11 20313

20313

集成电路。 TTL集成逻辑门电路的输入级采用多发射极三级管、输出级采用达林顿结构,这不仅提高了门电路的开关速度,也使电路有较强的驱动负载的能力。在TTL系列中,除了有实现各种基本逻辑功能的门电路以外,还有集电极开路门和三态门。 MOS集成电

2017-12-12 10:33:04 9

9 即集电极开路门电路,OD门,即漏极开路门电路,必须外界上拉电阻和电源才能将开关电平作为高低电平用。否则它一般只作为开关大电压和大电流负载,所以又叫做驱动门电路。输出端可以实现线与连接;oc门必须外接负载电阻和电源才能正常工作。

2017-11-09 17:41:25 38092

38092 逻辑门是逻辑电路的基本组成部分,可以由晶体管来构成,逻辑门大致可以分为基本门、万用门和延伸门等三种,其中基本门又可以分为与门、或门和非门三种。逻辑门可以使信号的高低电平转化为响应的逻辑信号,从而实现逻辑运算

2017-05-22 14:16:38 53353

53353

介绍了什么是集电极开路,漏极开路,推挽上拉,电阻弱上拉,三态门。

2017-02-28 22:08:40 1

1 三态门在数字电路上可以说是应用的非常广泛,特别是一些总线上的应用,因而,随着数字电路的发展,就避免不了用硬件描述语言在FPGA上来设计实现三态门。

2017-02-08 11:37:06 7000

7000 集电极开路_漏极开路_推挽_上拉电阻_弱上拉_三态门_准双向口,感兴趣的小伙伴们可以瞧一瞧。

2016-11-16 18:32:35 14

14 为了让读者确实理解TTL与非门与OC门的区别,熟练地掌握OC门的应用,通过对TTL与非门的分析,和对其弊端的指出,说明研制OC门的理由,总结了OC门上拉电阻的作用和计算方法,对OC门上

2013-09-18 14:08:15 89

89 基于探索仿真三态门总线传输电路的目的,采用Multisim10仿真软件对总线连接的三态门分时轮流工作时的波形进行了仿真实验测试,给出了仿真实验方案,即用Multisim仿真软件构成环形计

2013-06-08 17:58:44 48

48 实验三 集电极开路门电路及三态门电路的研究 一、实验目的 1、熟悉集电极开路OC门及三态TS门的逻辑功能和使用方法 2、掌握三态门构成总线的特点及方法 3、掌握集电极负载电阻RL对

2012-07-16 23:03:30 36

36 介绍了用Multisim仿真软件分析三态门工作过程的方法,目的是探索三态门工作波形的仿真实验技术,即用Multisim仿真软件中的字组产生器产生三态门的控制信号及输入信号,用Multisim中示

2011-05-06 15:59:38 76

76 实验目的1. 掌握与非门、或非门、与或非门及异或门的逻辑功能。2. 了解三态门的逻辑功能以及禁止状态的判别方法。了解三态门的应用。3. 掌握组合逻辑电路的设计和实

2010-08-18 14:50:44 109

109 三态门:计算机的逻辑部件

常用的集成门电路器件分为两大类:CMOS和TTL。 CMOS是由单极型场效应三极管组成集成电路, TTL是晶体管-晶体管逻辑电路

2010-04-15 14:55:00 1685

1685 或门,或门是什么意思

或逻辑及或门:

或逻辑指的是:在决定某事件的诸条件中,只要有一个或一个以上的条件具备,该事件就会发生

2010-03-08 11:39:13 13754

13754 OD门(漏极开路的门电路)

如同TTL OC门,CMOS OD门,可用来“线与”。

2010-02-28 19:15:52 16654

16654

三态门的组成及工作原理

2010-02-28 19:13:26 23595

23595

OC门输出并联的接法及逻辑图

2009-07-15 19:02:57 6069

6069

集电极开路门和三态输出门的应用

一、 实训目的1.熟悉集电极开路门(OC门)和三态输出门(TSL门)的逻辑功能;2.熟悉用OC门构成线与功能;3.熟悉用TSL门

2009-04-07 23:23:53 59

59 三态与非门(TSL)

利用OC门虽然可以实现线与的功能,但外接电阻Rp的选择要受到一定的限制而不能取得太小,因此影响了工作速度。

2009-04-07 00:15:37 7965

7965

集电极开路门

在工程实践中将两个门的输出端并联以实现与逻辑的功能称为线与。 考察下图所示的情况。当将图中所示的两个逻辑门的输出连接在一起,并且

2009-04-07 00:15:19 19903

19903

TTL或非门、集电极开路门和三态门电路

1.TTL或非门

下图为TTL或非门的逻辑电路及其代表符号。

2009-04-07 00:11:59 13667

13667

3.3.3 其它功能的TTL门电路一、集电极开路与非门(OC门)1.OC门的工作原理2.OC门的应用二、与或非门三、三态输出门(TSL门)1.三态输出门

2009-03-30 16:15:14 2145

2145

3.3.3 其它功能的TTL门电路一、集电极开路与非门(OC门)1.OC门的工作原理2.OC门的应用二、与或非门三、三态输出门(TSL门)1.三态输出门

2009-03-30 16:14:25 2022

2022

什么是三态门?

三态门,是指逻辑门的输出除有高、低电平两种状态外,还有第三种状态——高阻状态的门电路 高阻态相当于隔断状态。

2008-05-26 12:48:24 41856

41856

电子发烧友App

电子发烧友App

评论