D触发器,是时序逻辑电路中必备的一个基本单元,学好 D 触发器,是学好时序逻辑电路的前提条件,其重要性不亚于加法器,二者共同构成数字电路组合、时序逻辑的基础。

2023-10-09 17:26:57 234

234

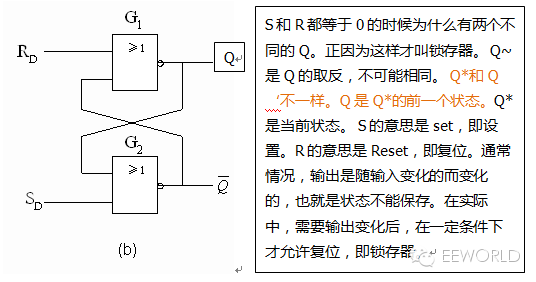

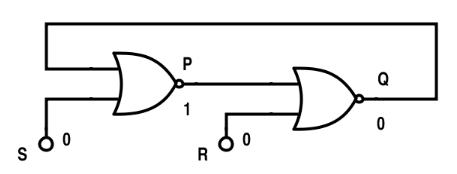

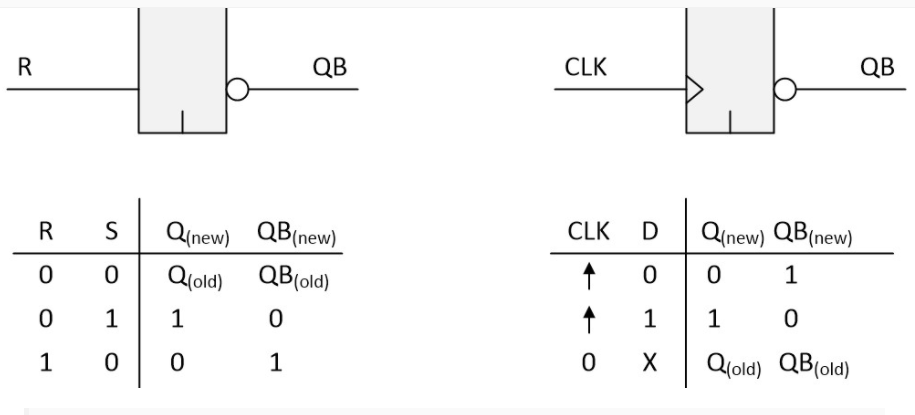

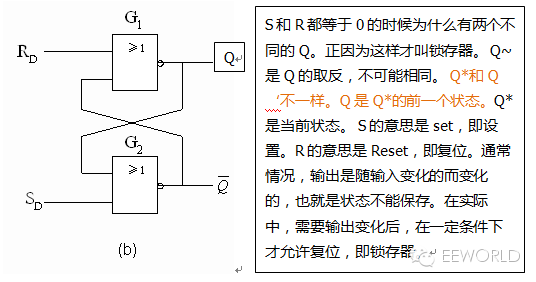

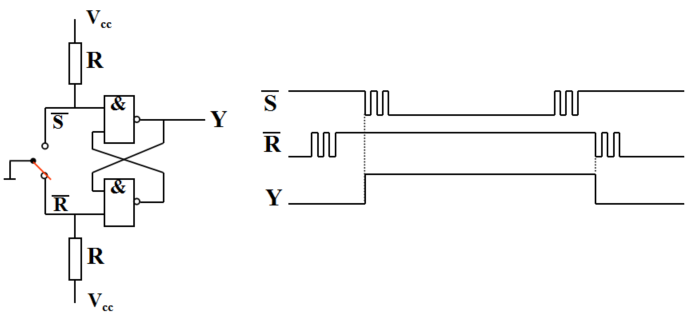

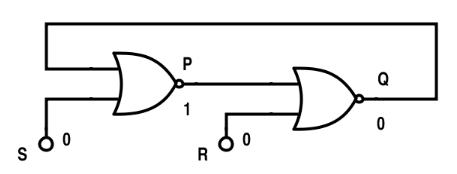

在数字电路中,RS触发器(也称为RS锁存器)是一种基本的双稳态触发器,它可以通过特定的输入信号来实现置位(Set)和复位(Reset)操作。

2023-09-28 16:31:07 1317

1317 rs触发器为什么不能都为1 RS触发器属于数字电路中的一种重要的锁存器。它由两个输入端和两个输出端组成。理论上,输入信号可以为任意值,包括1或0。但是,在实际应用中,不能让RS触发器的两个输入信号

2023-09-17 14:47:12 341

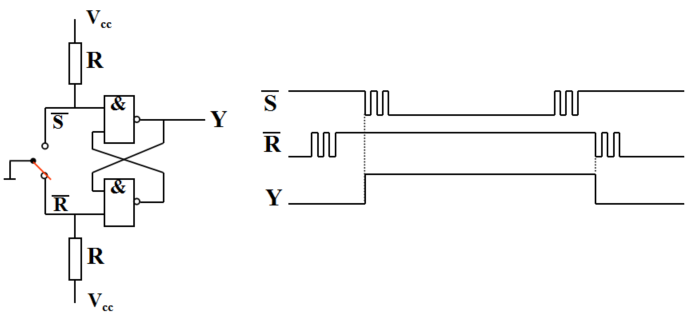

341 由于RS触发器实现方式的不同,对输入信号抖动(即短时间内多次变化)的响应也不同。原始的电路设计可能导致RS触发器对输入信号的抖动比较敏感。

2023-09-07 15:47:45 683

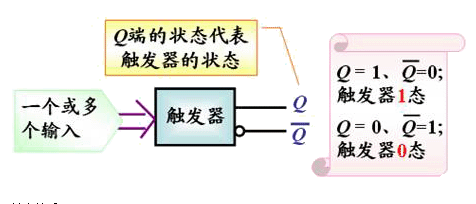

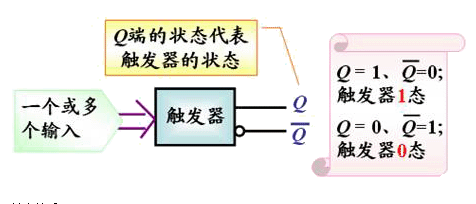

683 触发器(Flip-Flop)是数字电路中的一种时序逻辑元件,用于存储二进制位的状态。它是数字电路设计中的基本构建块之一,常用于存储数据、实现状态机、控制信号的生成等。触发器可以看作是一种特殊

2023-08-31 10:50:19 1436

1436

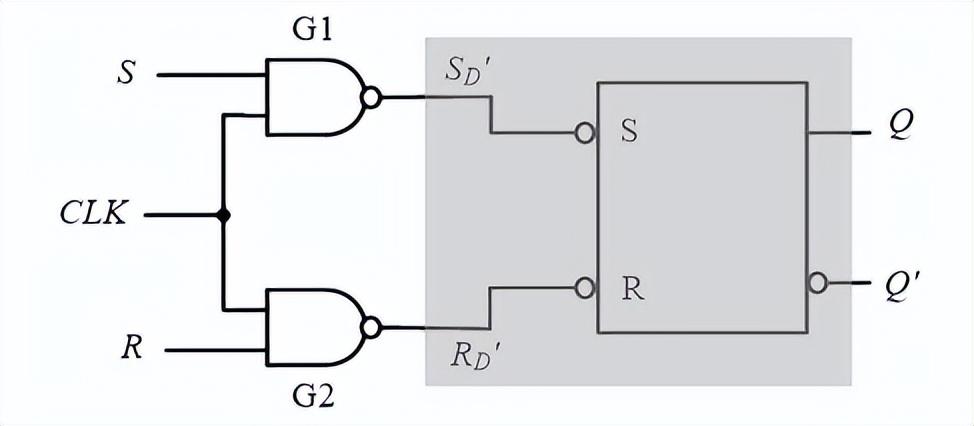

在传统的异步 RS 触发器中,当输入的 R 和 S 同时为 1 时,会引发互锁问题,输出结果是不确定的。为了避免这个问题,常常使用带有使能控制的同步触发器,如带有时钟信号的 D 触发器或 JK 触发器。这些触发器在时钟边沿上才会响应输入信号,解决了异步 RS 触发器的互锁问题。

2023-08-28 15:44:35 641

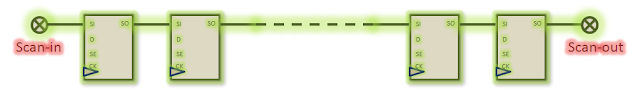

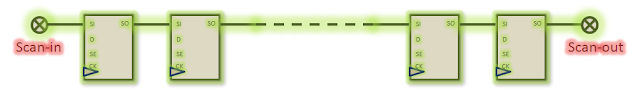

641 什么是扫描链: 扫描链是基于扫描的设计中的元素,用于移进和移出测试数据。扫描链由连接在链中的多个触发器构成,其中一个触发器的输出连接到另一个触发器。第一触发器的输入连接到芯片的输入引脚(称为扫描入

2023-08-25 17:01:16 180

180

触发器的输出状态由什么决定 触发器是一种数字电路元件,用于存储和转换电信号。它通常由几个门电路构成,并能够在符合特定条件时改变输出状态。触发器的输出状态是由输入信号和内部反馈电路共同决定的。在本篇

2023-08-24 15:50:23 276

276 什么是触发器?触发器的作用是什么?触发器的触发方式 触发器是一种在数据库中执行自动化操作的工具。它是一种特殊的存储过程,可以监视数据库表的变化,并在满足特定条件时自动触发一系列操作。触发器通常

2023-08-24 15:50:15 852

852 请简述锁存器与触发器的概念,并分析二者的区别。

2023-08-15 09:24:10 646

646

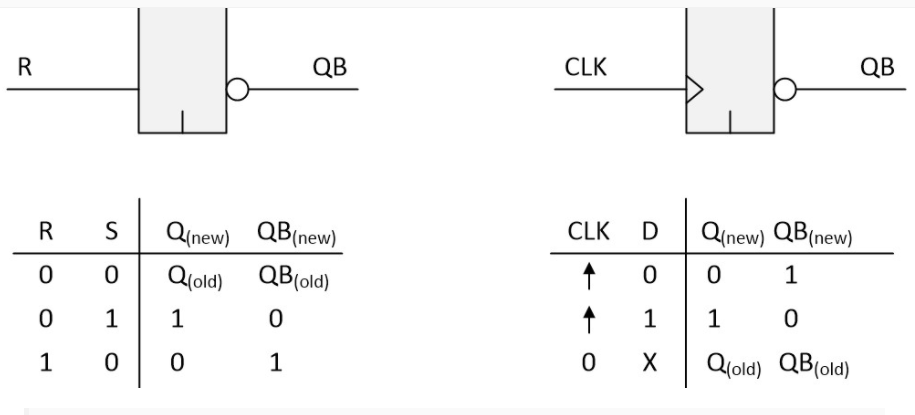

锁存器和触发器有时组合在一起,因为它们都可以在其输出上存储一位(1或0)。与锁存器相比,触发器是需要时钟信号(Clk)的同步电路。D 触发器仅在时钟从

2023-06-29 11:50:18 5258

5258

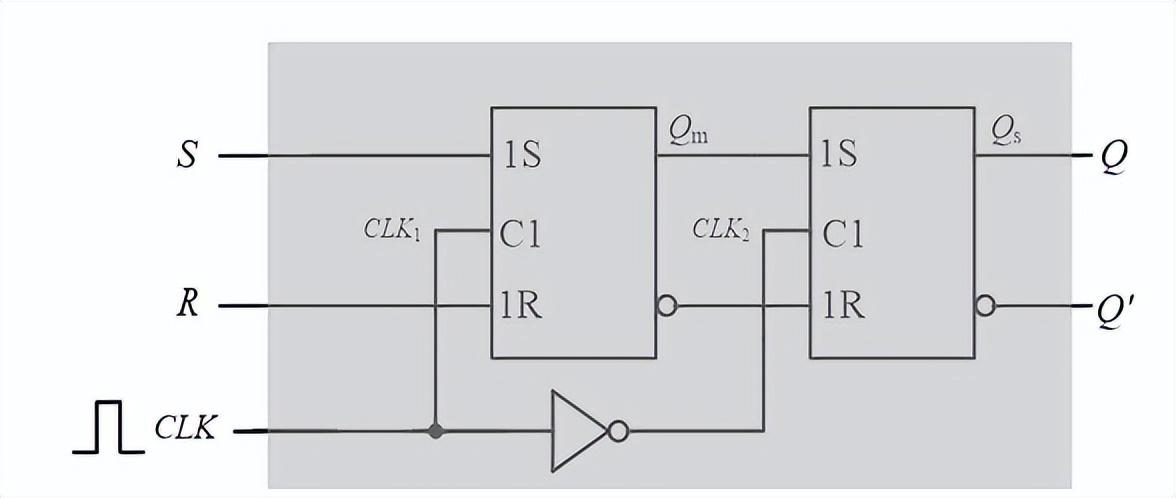

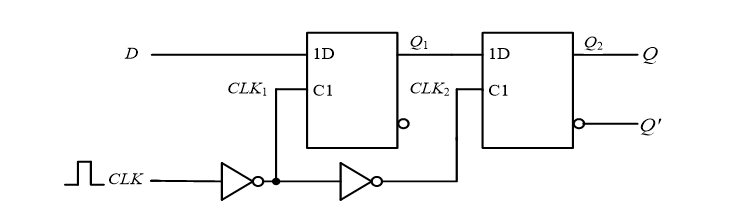

简单的说触发器实现边沿出发是通过两级锁存器实现的,比如上升沿触发其实是,前一级是低电平锁存,后一级是高电平锁存。

2023-06-28 11:18:32 438

438

锁存器是构成各种时序电路的基本元件,它的特点是具有0和1两种稳定的状态,一旦状态被确定,就能自行保持,即长期存储1位的二进制码,直到有外部信号作用时才有可能改变。锁存器是一种对电平敏感的存储单元电路,它们可以在特定输入电平作用下改变状态。

2023-03-23 16:03:32 658

658

锁存器(latch)---对脉冲电平敏感,在时钟脉冲的电平作用下改变状态,当Gate输入为高电平时,输入D透明传输到输出Q;当Gate从高变低或者保持低电平时,输出Q被锁存保持不变。锁存器是电平触发的存储器。

2023-03-23 14:48:54 1357

1357

触发器应用举例

2023-03-15 16:40:14 574

574

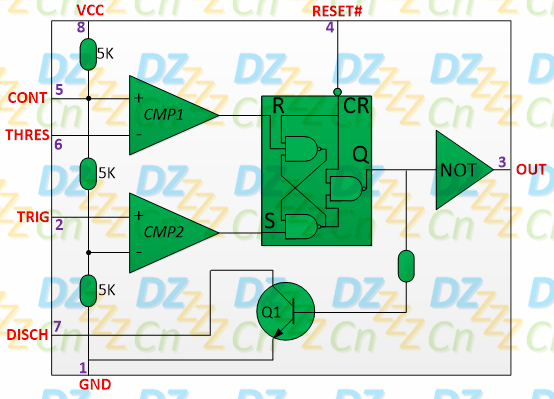

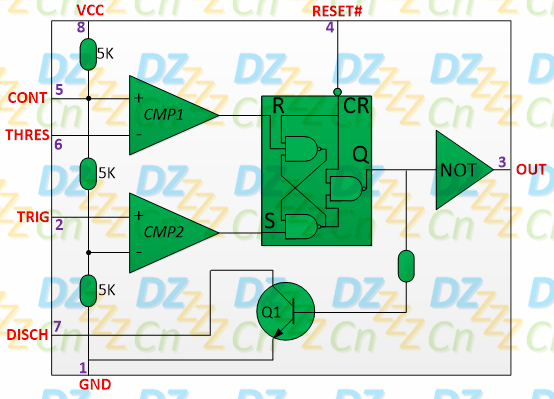

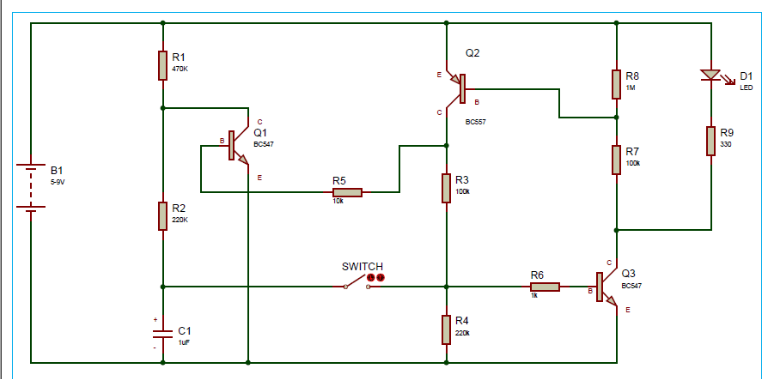

555定时器(Timer)因内部有3个5K欧姆分压电阻而得名,是一种多用途的模数混合集成电路,它能方便地组成施密特触发器、单稳态触发器与多谐振荡器,而且成本低,性能可靠,在各种领域获得了广泛的应用。

2023-03-08 15:36:00 5183

5183

八进制透明锁存器(三态);八进制 D 触发器(三态)-74F373_374

2023-03-03 20:05:16 0

0 连通的;当使能端为低电平时,输出口的数据保持之前的数据不变,无论输入口的数据怎么变化,输出都保持不变,就是把原来的状态锁存下来了(所以才叫锁存器)。锁存器与触发器的区别在于:**锁存器是电平触发,而触发器是边沿触发。**锁

2023-02-09 21:05:05 597

597 锁存器(latch):是电平触发的存储单元,数据存储的动作(状态转换)取决于输入时钟(或者使能)信号的电平值,尽当锁存器处于使能状态时,输出才会随着数据输入发生变化。

2023-01-31 14:57:40 1186

1186 你有没有遇到过这样奇怪的事:你一直以为自己知道某件事,但当你试着向别人解释它时,你才发现自己的论述中存在漏洞和逻辑上的差异?这就是我最近所遇到的情况,当时有人问我锁存器和触发器之间的区别,以及为什么它们都与寄存器有关。

2023-01-30 15:21:15 2073

2073 主要内容: ·双稳态器件 ·锁存器常见结构 ·锁存器的应用 ·触发器 ·触发器的建立时间和保持时间 1、双稳态器件 ** 双稳态器件**是指稳定状态有两种,一种是0,一种是1的器件;双稳态器件

2023-01-28 09:28:00 2426

2426

1:锁存器、触发器、寄存器的关联与区别 首先应该明确锁存器和触发器是由与非门之类的东西构成。尤其是锁存器,虽说数字电路定义含有锁存器或触发器的电路叫时序电路,但锁存器有很多组合逻辑电路的特性。 锁存

2022-12-19 12:25:01 3721

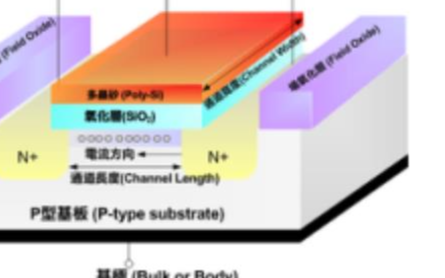

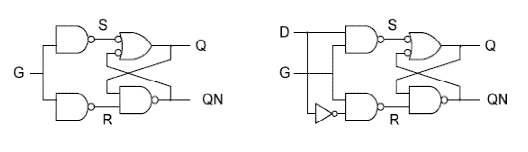

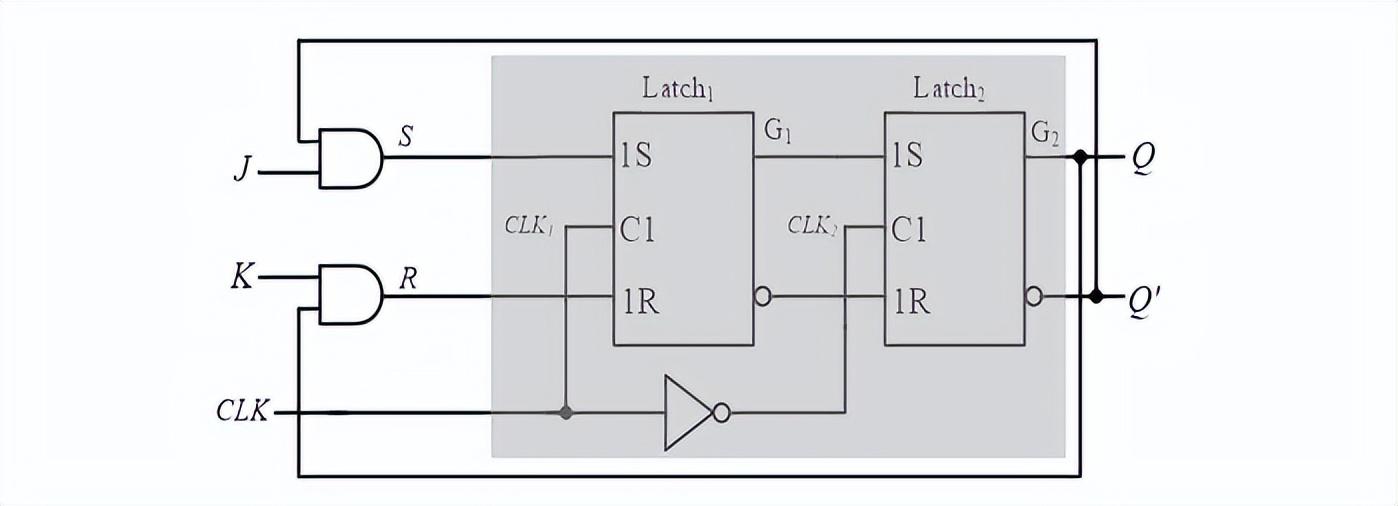

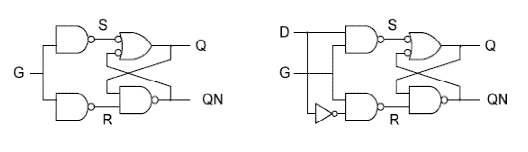

3721 来源:罗姆半导体社区 触发器的电路图由逻辑门组合而成,其结构均由R-S锁存器派生而来(广义的触发器包括锁存器)。触发器可以处理输入、输出信号和时钟频率之间的相互影响。 在R-S锁存器的前面加一个由

2022-11-29 17:35:40 1584

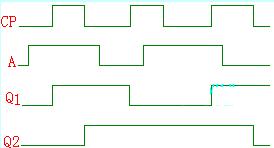

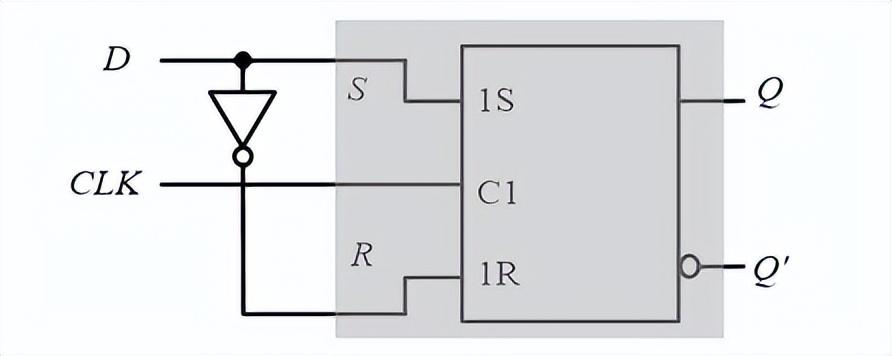

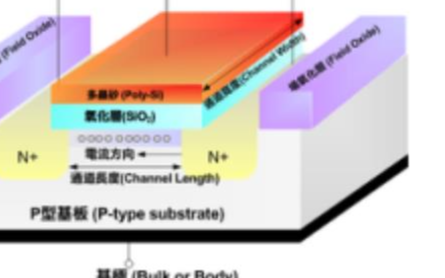

1584 D 触发器是一个电路,存储 1bit 数据,并定期地根据触发器的输入(d)更新这 1 bit 数据,更新通常发生在时钟上升沿(clk)。存储的数据会通过输出管脚(q)输出。

2022-11-10 10:01:39 383

383 rs触发器电路图与rs触发器内部电路图 rs触发器电路图 主从RS触发器电路图: 主从触发器由两级触发器构成,其中一级接收输入信号,其状态直接由输入信号决定,称为主触发器,还有一级的输入与主触发器

2022-10-19 19:16:03 16964

16964

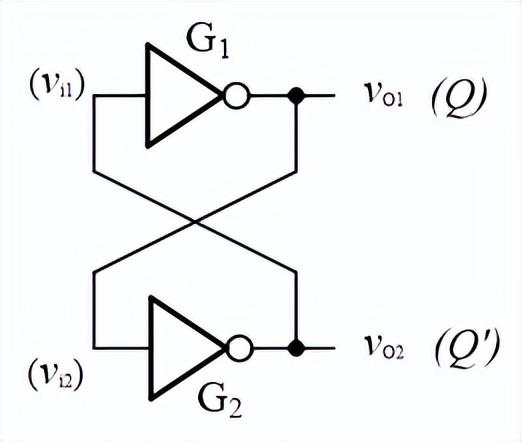

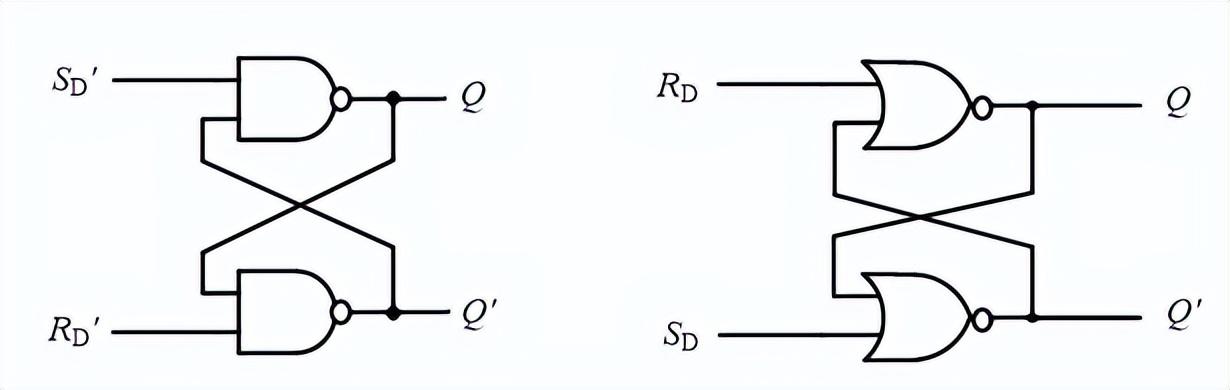

什么是RS触发器 其中R、S分别是英文复位 Reset 和置位 Set 的缩写,作为最简单的一种触发器,是构成各种复杂触发器的基础。RS触发器的逻辑电路图如下图所示。 RS触发器可以用与非门实现或者

2022-10-19 17:49:59 5720

5720

锁存器是具有两个稳定状态的时序逻辑电路,即它是双稳态多谐振荡器。锁存器有一个反馈路径来保留信息。因此,锁存器可以是存储设备。只要设备处于开机状态,锁存器就可以存储一位信息。当使能启用时,锁存器会在输入更改时立即更改存储的信息,即它们是电平触发设备。当使能信号打开时,它会持续对输入进行采样。

2022-09-12 16:13:00 6069

6069

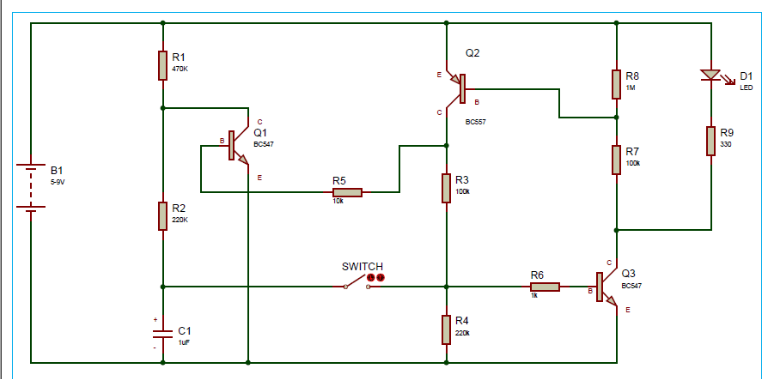

电路中,电路只能被锁存到一种状态,并且可以改变需要移除电源的状态。通常移位寄存器和触发器用于锁存电路,就像我们在Clap-on-Clap-off 电路中使用的一样。

2022-08-25 16:32:47 2779

2779

每个 Slice 有 8 个 FF 。四个可以配置为 D 型触发器或电平敏感锁存器,另外四个只能配置为 D 型触发器,但是需要记得是:当原来的四个 FF 配置为锁存器时,不能使用这四个 FF 。

2022-07-22 10:05:01 2518

2518 每个 Slice 有 8 个 FF 。四个可以配置为 D 型触发器或电平敏感锁存器,另外四个只能配置为 D 型触发器,但是需要记得是:当原来的四个 FF 配置为锁存器时,不能使用这四个 FF 。

2022-03-15 11:59:34 7158

7158 时钟脉冲的电平作用下改变状态锁存器是电平触发的存储单元,数据存储的动作取决于输入时钟(或者使能)信号的电平值,仅当锁存器处于使能状态时,输出才会随着数据输入发生变化。锁存器不同于触发器,它不在锁存数据

2011-10-09 16:19:46

这是一个系列文章,从最简单的门电路介绍,从基础的锁存器、触发器、编码器、译码器等一系列数字逻辑电路开始,最终构造一个简易版的CPU实物

2021-11-06 09:20:58 16

16 首先应该明确锁存器和触发器也是由与非门之类的东西构成。尤其是锁存器,虽说数字电路定义含有锁存器或触发器的电路叫时序电路,但锁存器有很多组合电路的特性。 组合电路就是一个真值表,一个函数,一组输入对应

2021-08-12 10:26:12 3567

3567 脉冲触发器由两个相同的电平触发的SR触发器组成,其中左SR触发器成为主触发器,右手侧称为从触发器。

2021-02-11 10:56:00 6965

6965

你有没有遇到过这样奇怪的事:你一直以为自己知道某件事,但当你试着向别人解释它时,你才发现自己的论述中存在漏洞和逻辑上的差异?这就是我最近所遇到的情况,当时有人问我锁存器和触发器之间的区别,以及

2021-01-05 16:03:53 4896

4896

,锁存器有两个输入,一个是有效信号EN,一个是输入数据信号DATA_IN,有一个输出Q,它的功能就是在EN有效的时候把DATA_IN的值传给Q,也就是锁存的过程。 2)触发器 触发器(Flip-Flop,简写为FF)也叫双稳态门,又称双稳态触发器,是一种可以在两种

2020-11-29 11:02:11 20662

20662 文章都对锁存器有个误解,我们后面会详细说明。 这篇文章,我们包含如下内容: ①锁存器、触发器和寄存器的原理和区别,为什么锁存器不好? ② 什么样的代码会产生锁存器? ③ 为什么锁存器依然存在于FPGA中? 锁存器、触发器和寄存器的原理和区别,为什么锁存器

2020-11-16 11:42:00 7206

7206

电子触发器常常用于高强度气体放电灯(HID)的启动,型号繁多。由于高强度气体放电灯启动时需要一个高电压来使气体电离进入等离子态,因而需要一个高压发生器做为启动器。这就是触发器早期的机械型触发器已经

2019-12-12 09:55:06 10534

10534 JK触发器是数字电路触发器中的一种基本电路单元。JK触发器具有置0、置1、保持和翻转功能,在各类集成触发器中,JK触发器的功能最为齐全。在实际应用中,它不仅有很强的通用性,而且能灵活地转换其他类型的触发器。由JK触发器可以构成D触发器和T触发器。

2019-11-08 14:48:44 79654

79654

锁存器(有时也称为S/R锁存器)是最小的存储器块。它们可以使用两个NOR逻辑门(S和R为高电平有效)或两个NAND门(输入为低电平有效)构建,并用于构建更复杂的锁存器和触发器。

2019-07-30 11:23:28 5658

5658

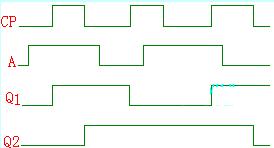

CP=1时,门。。打开,门。。被封锁,从触发器保持原来状态不变,D信号进入主触发器。但是要特别注意,这时主触发器只跟随而不锁存,即。。跟随D变化,D怎么变。。也随之怎么变。

2019-07-15 08:57:32 42337

42337

触发器是一种用来保障参照完整性的特殊的存储过程,它维护不同表中数据间关系的有关规则。当对指定的表进行某种特定操作(如:Insert,Delete或Update)时,触发器产生作用。触发器可以调用存储过程。

2019-07-12 10:05:42 22642

22642

D型触发器是一个改进的置位复位触发器,增加了一个反相器,由此可见以防止S和R输入处于相同的逻辑电平,此状态将强制两个输出都处于逻辑“1”,超越反馈锁存动作,无论哪个输入先进入逻辑电平“1”都将失去控制,而另一个仍处于逻辑“0”的输入控制锁存器的结果状态。

2019-06-26 15:36:28 14537

14537

本文档的主要内容详细介绍的是数字电路教程之触发器课件的详细资料说明主要内容包括了:一 SR锁存器,二 电平触发的触发器,三 脉冲触发的触发器,四 边沿触发的触发器,五 触发器的逻辑功能及其描述方法

2018-12-28 08:00:00 17

17 本文首先介绍了锁存器Latch结构和锁存器latch的优缺点,其次介绍了触发器Flip-flop的结构与优缺点,最后介绍了锁存器Latch和触发器Flip-flop两者之间的区别。

2018-04-18 14:10:10 128942

128942

本文开始阐述了单稳态触发器工作特点和单稳态触发器的分类,其次阐述了单稳态触发器工作原理,最后介绍了常用的CD4098单稳态触发器。

2018-03-28 15:41:35 37615

37615

本文开始介绍了触发器的定义和触发器的特点,其次阐述了触发器的分类和触发器的作用,最后介绍了触发器的工作原理。

2018-03-27 17:35:52 19880

19880 本文开始介绍了什么是单稳态触发器以及单稳态触发器的电路组成,其次阐述了单稳态触发器特点、门电路构成的单稳态触发器、D触发器构成的单稳态触发器,最后详细的阐述了时基电路构成的单稳态触发器。

2018-03-27 09:24:23 68948

68948

触发器是Oracle提供一种SQL语句执行机制。它可以用来实现更为复杂的约束,用来保证数据的完整性。本章将讲解触发器定义、语句触发器、行触发器、instead of触发器、系统和用户触发器。 触发器

2018-03-26 13:51:31 2

2 锁存器是电平触发的存储单元,数据存储的动作取决于输入时钟(或者使能)信号的电平值,仅当锁存器处于使能状态时,输出才会随着数据输入发生变化。

2018-03-26 10:57:46 15588

15588 锁存器就是把单片机的输出的数据先存起来,可以让单片机继续做其它事。它的LE为高的时候,数据就可以通过它。当为低时,它的输出端就会被锁定RS触发器是构成其它各种功能触发器的基本组成部分。又称为基本RS触发器。

2018-01-31 14:48:13 28618

28618

边沿触发器,指的是接收时钟脉冲CP 的某一约定跳变(正跳变或负跳变)来到时的输入数据。在CP=l 及CP=0 期间以及CP非约定跳变到来时,触发器不接收数据的触发器。具有下列特点的触发器称为边沿触发方式触发器,简称边沿触发器。

2018-01-31 09:02:33 68254

68254

JK触发器是数字电路触发器中的一种基本电路单元。JK触发器具有置0、置1、保持和翻转功能,在各类集成触发器中,JK触发器的功能最为齐全。在实际应用中,它不仅有很强的通用性,而且能灵活地转换其他类型的触发器。由JK触发器可以构成D触发器和T触发器。

2017-12-25 17:30:03 172587

172587

锁存器(latch)---对脉冲电平敏感,在时钟脉冲的电平作用下改变状态 锁存器是电平触发的存储单元,数据存储的动作取决于输入时钟(或者使能)信号的电平值,仅当锁存器处于使能状态时,输出才会随着数据输入发生变化。

2017-11-02 09:24:41 92855

92855

所谓锁存器,就是输出端的状态不会随输入端的状态变化而变化,仅在有锁存信号时输入的状态被保存到输出,直到下一个锁存信号到来时才改变。典型的锁存器逻辑电路是 D 触发器电路。 PS:锁存信号(即对LE赋高电平时Data端的输入信号)。锁存,就是把信号暂存以维持某种电平状态。

2017-10-30 14:35:53 58733

58733

触发器的功能:

① 完成比约束更复杂的数据约束:触发器可以实现比约束更为复杂的数据约束

② 检查所做的SQL是否允许:触发器可以检查SQL所做的操作是否被允许。例如:在产品库存表里,如果

2017-08-19 12:05:00 41369

41369 一种单锁存器CMOS三值D型边沿触发器设计

2017-01-17 19:54:24 22

22 触发器的相互转换 基本触发器之间是可以互相转换的,JK触发器和D触发器是两种最常用的触发器,别的触发器可以通过这两种触发器转化得来,它们

2010-09-18 08:56:19 3600

3600

本次重点内容:1、触发器的概念和分类。2、同步触发器、主从触发器、边沿触发器的含义。

4.1.1 触发器概述一、触发

2010-08-19 08:57:47 18499

18499 1、掌握锁存器、触发器的电路结构和工作原理;

2、熟练掌握SR触发器、JK触发器、D触发器及T 触发器的逻辑功能;

3、正确理解锁存器、触发器的动态特性

2010-08-18 16:39:35 233

233 5.1 基本RS触发器5.2 时钟控制的触发器5.3 集成触发器5.4 触发器的逻辑符号及时序图

2010-08-10 11:53:23 116

116 触发器的分类, 触发器的电路

双稳态器件有两类:一类是触发器,一类是锁存器。锁存器是触发器的原始形式。基本

2010-03-09 09:59:59 1491

1491 地址锁存器,地址锁存器是什么意思

地址锁存器就是一个暂存器,它根据控制信号的状态,将总线上地址代码暂存起来。8086/8088数

2010-03-09 09:49:49 4547

4547 锁存器,锁存器是什么意思

锁存器定义一位钟控D触发器只能传送或存储一位二进制数据,而在实际工作中往往是一次传送或存

2010-03-09 09:44:12 11794

11794 施密特触发器,施密特触发器是什么意思

施密特触发器也有两个稳定状态,但与一般触发器不同的是,施密特触发器采用电位触发

2010-03-08 14:14:56 1763

1763 什么是RS触发器,RS触发器的工作原理是什么?

主从RS触发器

2010-03-08 14:00:11 29331

29331 D触发器,D触发器是什么意思

边沿D 触发器: 电平触发的主从触发器工作时,必须在正跳沿前加入输入信号。如果在CP 高

2010-03-08 13:53:13 4130

4130 JK触发器原理是什么?

JK触发器是一种功能较完善,应用很广泛的双稳态触发器。图9-5(a)所示是一种典型结构的JK触发器——主从型JK触

2010-03-08 13:41:11 23241

23241 JK触发器,JK触发器是什么意思

1.主从JK触发器主从结构触发器也可以彻底解决直接控制,防止空翻。这里以性能优良、广泛使用的主从JK触发器为

2010-03-08 13:36:29 5842

5842 触发器

一、 实验目的

1. 学会测试触发器逻辑功能的方法。 2. 进一步熟悉RS触发器

2009-03-28 10:02:34 8498

8498

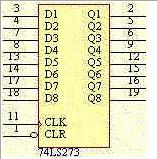

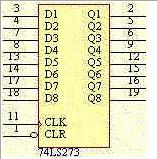

地址锁存器--74LS273

74LS273是带清除端的八D触发器,只有清除端为高电平时才具有锁存功能,锁存控制端为11脚CLK,在上升沿锁存。单片机的ALE端输出的锁存控制信号必须经反

2009-03-14 15:37:57 4529

4529

一、实验目的1、掌握基本RS、JK、D和T触发器的逻辑功能2、掌握集成触发器的逻辑功能及使用方法3、熟悉触发器之间相互转换的方法二、实验原理触发器具有两个稳

2008-12-19 00:40:23 48

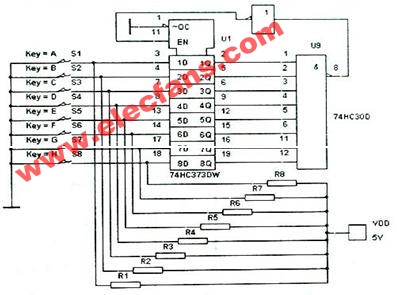

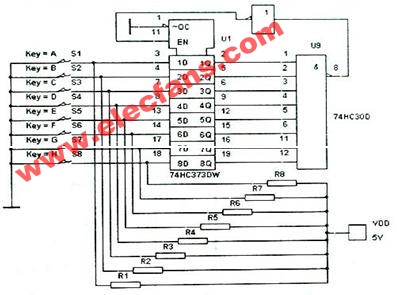

48 8(八)路触发锁存电路

图所示为8路触发锁存电路。图中,74HC373

2008-12-01 20:45:39 2839

2839

D触发器

同步式D触发器逻辑电路图

D触发器功能

2008-10-20 09:57:54 1846

1846

【本章主要讲授内容】 1.触发器的性质与分类; 2.触发器的功能; 3.触发器的结构和触发方式; 4.触发器的时间参数。【本章重点、难点内容】

2008-10-20 09:53:54 59

59 74LS71 与输入R—S主从触发器(带预置和清除端)

74279、74LS279、74HC279 四/R—/S锁存器双嵌位输入,图腾柱输出。

2008-01-22 12:45:32 26171

26171 D触发器真值表分析:

1. D 触发器真值表

Dn

2007-09-11 23:15:20 17600

17600 CD4013 双D触发器 *CD4027 双JK触发器 *CD4042 四锁存D型触发器 *CD4043

2006-04-17 21:18:32 3219

3219 双稳态器件有两类:一类是触发器,一类是锁存器。锁存器是

2006-04-16 17:31:53 888

888

电子发烧友App

电子发烧友App

评论