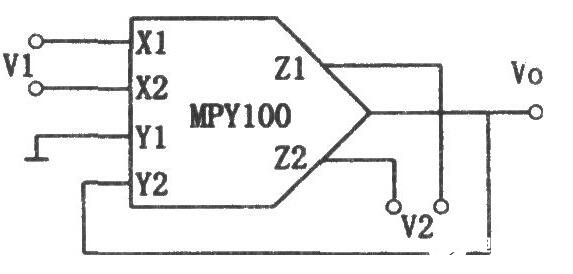

除法运算电路图

电子发烧友App

电子发烧友App

硬声App

硬声App

完善资料让更多小伙伴认识你,还能领取20积分哦,立即完善>

电子发烧友网>电子技术应用>电路原理图>放大电路图>运算放大器电路>除法运算电路图

相关推荐

5168

5168 15859

15859

5141

5141 3961

3961 0

0 5

5 5

5 1172

1172

11412

11412 14405

14405

评论