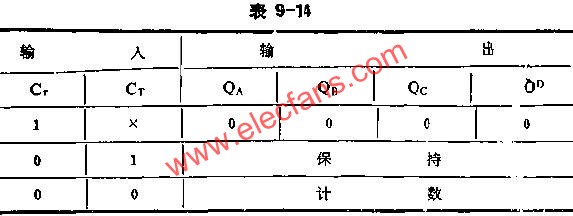

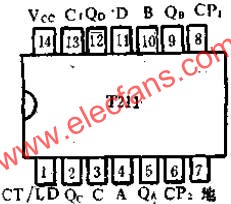

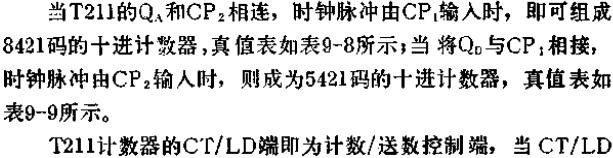

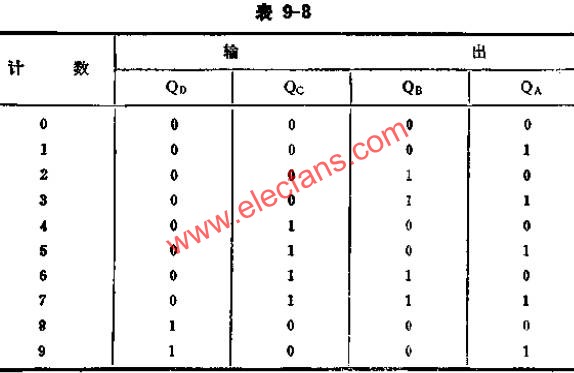

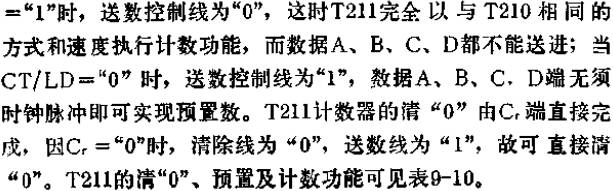

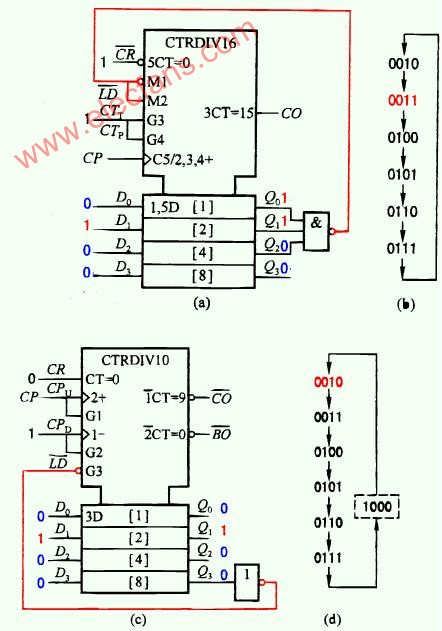

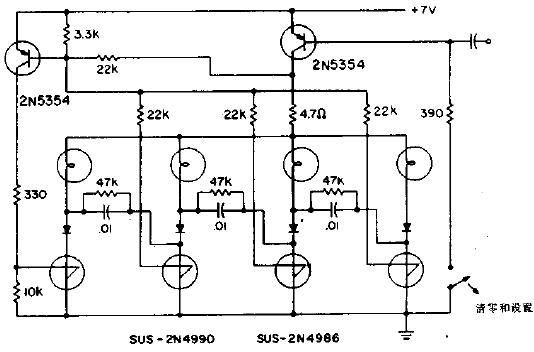

T211 2-5-10进制可预置计数器的应用电路图

- 计数器(91962)

相关推荐

基于FPGA的十进制计数器

本方案是一个基于 FPGA 的十进制计数器。共阳极 7 段显示器上的 0 到 9 十进制计数器,硬件在 Xilinx Spartan 6 FPGA 板上实现。

2022-12-20 14:52:25 2

2

2

2十进制计数器的工作原理

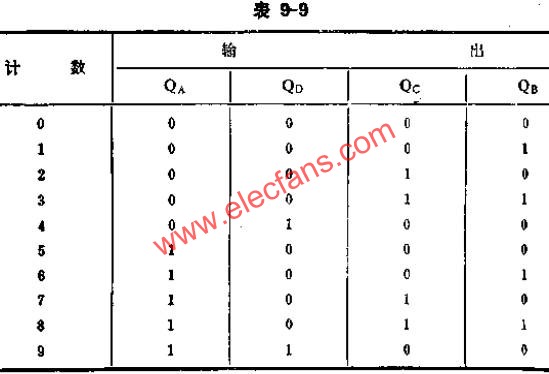

二进制编码的十进制是一个串行数字计数器,可计数十位数字,它会为每个新的时钟输入重置。由于它可以通过10种独特的输出组合,因此也被称为“十进制(BCD)计数器”。十进制计数器可以计数0000、0001、0010、1000、1001、1010、1011、1110、1111、0000和0001等。

2022-10-31 16:25:37 11019

11019

11019

11019

74ls161十进制计数器电路图

74LS161为4位二进制同步加法计数器。其中 是异步清零端, 是预置数控制端,D3 D2 D1 D0是预置数输入端,CTt和CTp是计数使能端,CO是进位输出端(CO=Q3 Q0

2021-07-09 16:12:21 73502

73502

73502

73502

使用Multisim仿真实例实现二进制计数器的实验电路图免费下载

本文档的主要内容详细介绍的是使用Multisim仿真实例实现二进制计数器的实验电路图免费下载。

2020-09-04 16:55:07 85

85

85

8574ls190应用电路图大全(五款74ls190不同进制计数器电路)

本文主要介绍了五款74ls190应用电路图。包括了60和100进制计数器(递增)电路,56进制递减计数器与100进制递减计数器电路和2位十进制可加减计数器电路。

2018-05-28 16:18:11 54071

54071

54071

54071

74ls192计数器应用电路图大全(五款电子骰子/计时/定时电路)

本文主要介绍了五款74ls192计数器应用电路图。其中包括了74ls192电子骰子电路、74ls192计时电路、74ls192定时电路、74ls19230进制计数器电路及两位十进制计数器。

2018-05-28 10:20:01 116393

116393

116393

116393

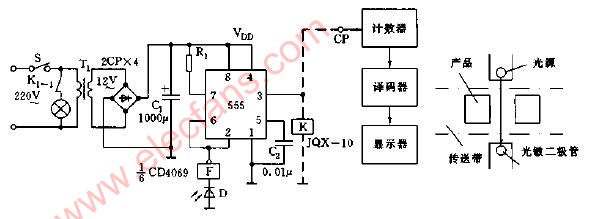

cd4026应用电路图大全(555时基电路/按键计数器/脉冲计数器)

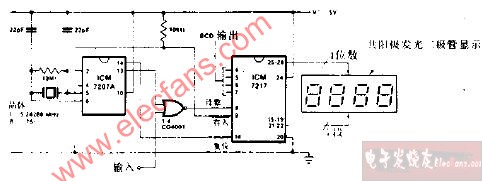

本文主要介绍了cd4026应用电路图大全(555时基电路/按键计数器/脉冲计数器)。由CD4026、555时基电路等组成的数字显示门铃电路,是由十进制计数/7段译码器CD4026、555时基电路等

2018-05-10 16:44:50 11589

11589

11589

11589

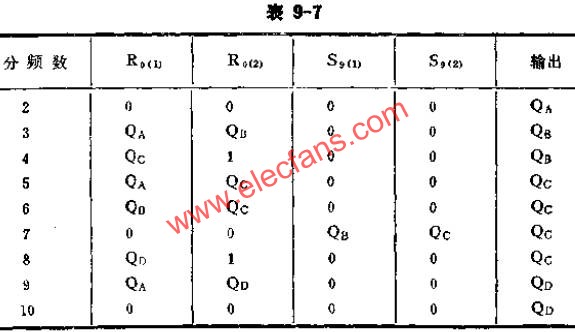

74ls161分频电路图大全(脉冲分频电路\同步加法计数器)

本文主要介绍了74ls161分频电路图大全(脉冲分频电路\同步加法计数器)。计数器又称为分频器。N进制计数器的进位输出脉冲就是计数器输入脉冲的N分频。N进制计数器可直接作为N分频器。用同步加法计数器

2018-05-08 14:41:38 95799

95799

95799

95799

74ls163应用电路图大全(N进制计数器\分频电路\时钟脉冲)

本文主要介绍了74ls163应用电路图大全(N进制计数器\分频电路\时钟脉冲)。74LS163是(模16)四位二进制同步计数器。该计数器能同步并行预置数据,同步清零,具有清零、置数、计数和保持四种

2018-05-08 14:27:23 51924

51924

51924

51924

同步计数器74ls162设计24进制计数器

本文首先介绍了计数器种类与应用,其次介绍了74LS160并行置零法设计24进制计数器电路图,最后介绍了74ls162设计24进制计数器原理电路图。

2018-05-08 11:46:43 54648

54648

54648

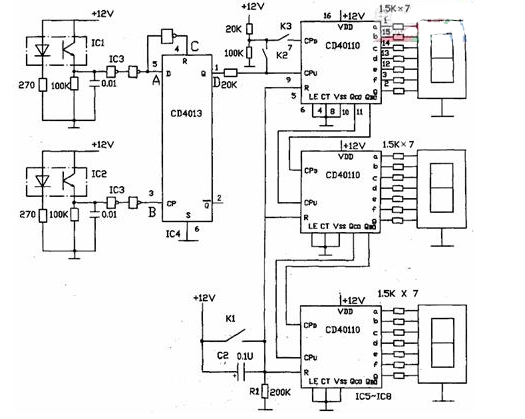

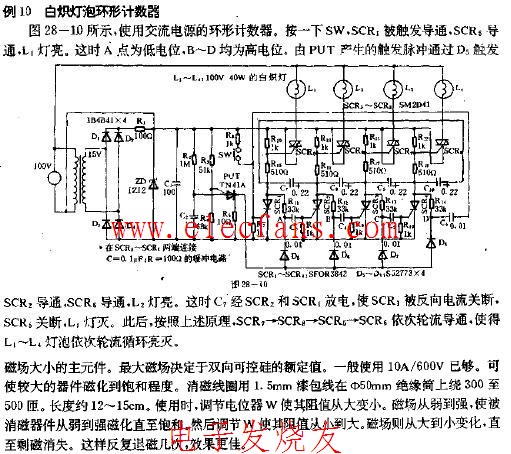

54648cd40110计数器电路图大全(七款cd40110计数器电路设计原理图详解)

本文主要介绍了cd40110计数器电路图大全(七款cd40110计数器电路设计原理图详解)。利用交流电源50Hz的输出频率通过分频,可以取得各种不同频率的时基脉冲。该电路选用lmin的时间长度作为

2018-03-04 11:09:50 31876

31876

31876

31876

cd4017计数器电路图(三款cd4017计数器电路)

本文开始对CD4017功能与CD4017逻辑结构图进行了介绍,其次分别介绍了用CD4017和选择开关组成多进制计数器、CD4017组成的1/n计数器电路与用CD4017组成1~17进制计数器电路图。

2018-01-31 13:58:06 22819

22819

22819

22819

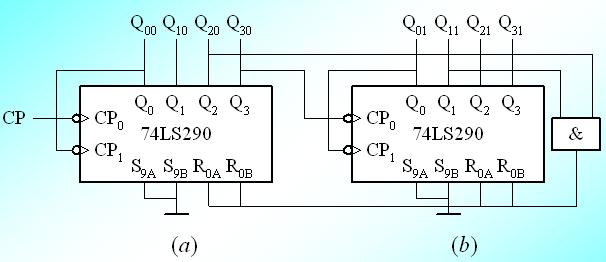

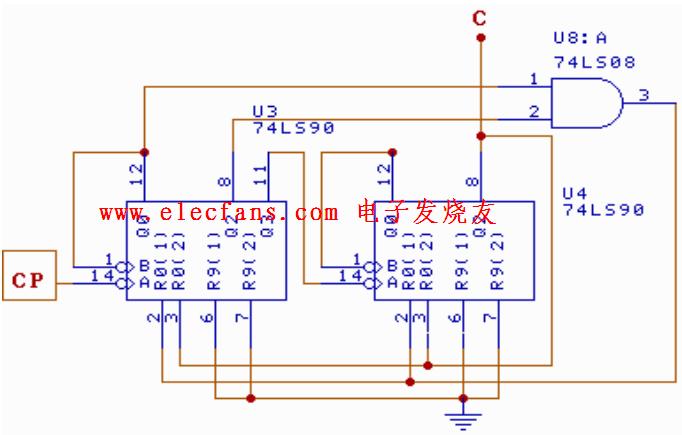

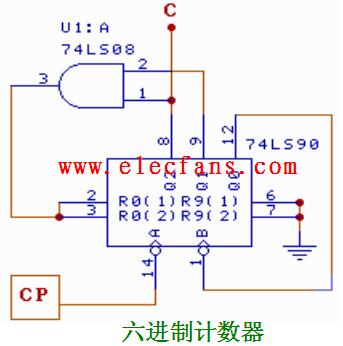

74ls290计数器电路大全(六种进制计数器电路)

74ls290是一个二,五,十进制计数器,本文为大家介绍由74ls290构成的各种进制计数器的电路。

2018-01-26 09:26:11 106188

106188

106188

106188

74ls160十进制计数器

本文主要介绍了74ls160十进制计数器电路的设计与实现。74LS160是二~十进制同步可预置计数器,1脚Cr为清零端,低电平有效.2脚CP为时钟脉冲输人端,上升沿触发.3~6V脚D1一D4为数据

2018-01-18 15:14:45 182091

182091

182091

182091

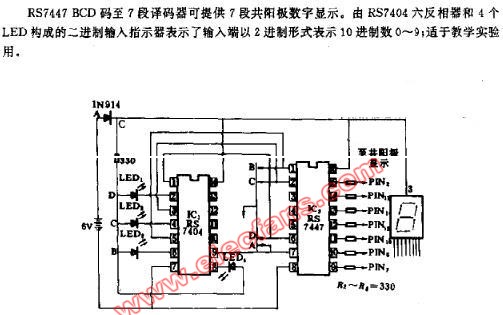

74LS161集成计数器电路(2、3、4、6、8、10、60进制计数器)

本文主要介绍了74LS161集成计数器电路(2、3、4、6、8、10、60进制计数器)。74LS161是4位二进制同步计数器,该计数器能同步并行预置数据,具有清零置数,计数和保持功能,具有进位输出端

2018-01-18 10:56:39 324594

324594

324594

324594

74ls161制作24进制计数器设计

74ls161为二进制同步计数器,具有同步预置数、异步清零以及保持等功能。两片74ls161可设计一个24进制计数器。

2018-01-16 15:30:46 110315

110315

110315

110315

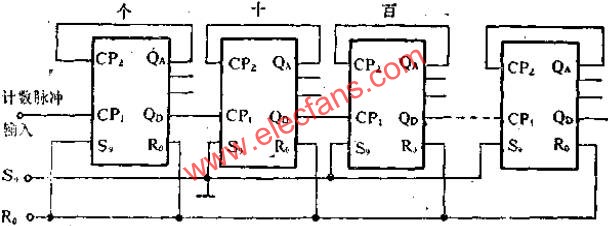

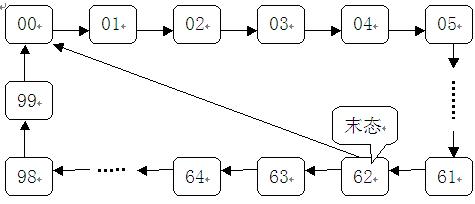

74ls90设计60进制计数器

60进制计数器,由于24进制、60进制计数器均由集成计数器级联构成,且都包含有基本的十进制计数器,从设计简便考虑,芯片选择同步十进制计数器

2017-12-22 13:55:48 148134

148134

148134

148134

基于74LS160的N进制计数器仿真设计

计的电路进行仿真实验。仿真结果表明设计的计数器能实现所要求的N进制技术功能。最终得出采用反馈复零法可以实现进制计数器的结论。

2017-12-21 17:08:37 60783

60783

60783

60783

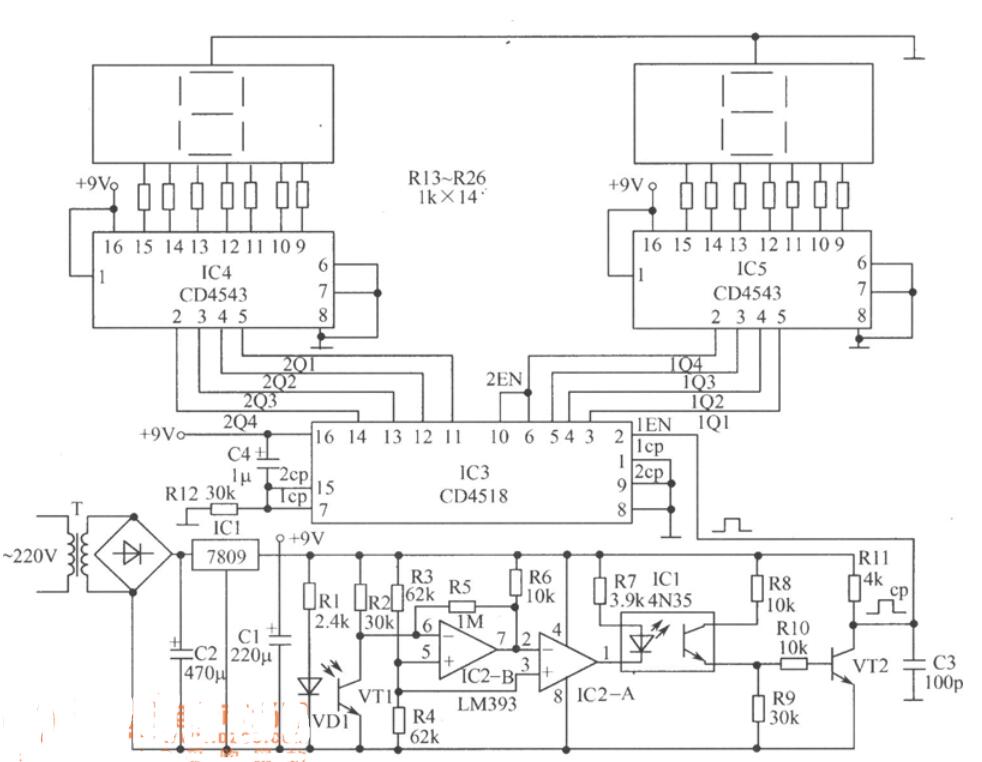

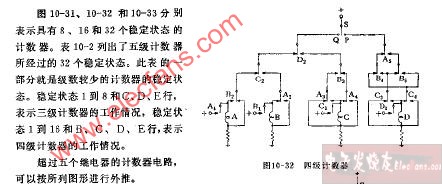

24进制计数器的设计

集成计数器常见的是多位二进制计数器及十进制计数器,当需要实现其它进制计数器时,通常利用现有的集成计数器进行适当的连接而构成。对于当设计要求没有限定计数器的状态编码时电路设计的灵活性问题已有文献进行

2017-11-09 16:36:16 81

81

81

81基于Proteus的任意进制计数器设计与仿真

提出一种基于Proteus 软件的任意进制计数器的设计。以74LS163 集成计数器为基础,用置数法设计了两种48 进制计数器,采用Proteus 软件对计数器进行仿真。结果表明,Proteus 软件具有实现48 进制计数器的功能。仿真图像清晰,能快速准确地验证设计结果。

2016-07-29 18:53:03 24

24

24

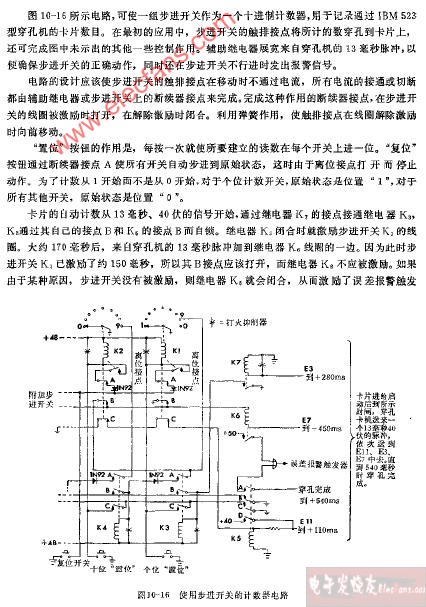

24C181 2-10进制可预置可逆计数器的应用线路图

C181是双时钟2-10进制可预置可逆计数器.所谓双时钟是指计数器的加法计数时钟和减法计数时钟各有它自身的输入

2010-10-19 15:16:06 814

814

814

814

C180 2-10进制同步加法计数器的应用线路图

C180(CMOS)2-10进制同步加法计数器由同步的四级D型触发器组成.它的管脚外引线排列和功用如图所示,C180 2-10进制

2010-10-19 14:56:14 1889

1889

1889

1889

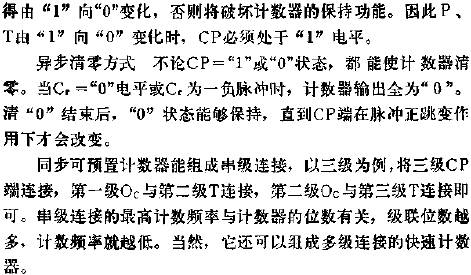

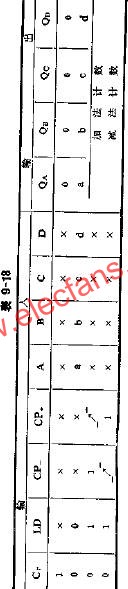

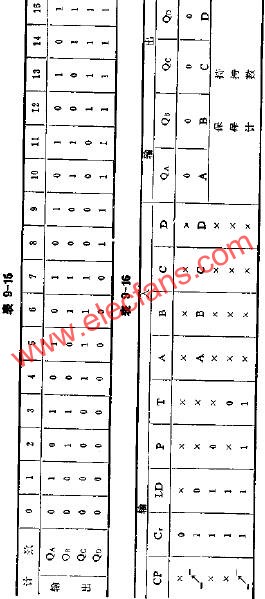

T217 2-10进制同步可预置可逆计数器的应用电路图

T217是2-10进制同步可预置可逆计数器,能同时作加法计数和减法计数.它的主要电参数为:电源电流ICC小于100MA,计数

2010-10-19 14:41:30 811

811

811

811

T216 2-10进制同步可预置计数器的应用线路图

T216是2-10进制同步可预置计数器,它的电源电流ICC小于94MA,计数工作频率约为10MHZ,CP到输出的平均延迟时间小于45NS,

2010-10-19 14:33:22 775

775

775

775

T215 2-16进制同步可预置可逆计数器的应用电路图

T215是2-16进制同步可预置可逆计数器.它能同时作加法计数和减法计数.它的主要电参数为:电源电流ICC小于100M

2010-10-19 14:09:21 1197

1197

1197

1197

T214 2-16进制同步可预置计数器的应用电路图

T214 2-16进制同步可预置计数器,它主主要电参数是:电源电流ICC小于94MA,计数工作频率FM>10MHZ,CP到输出的平均延迟

2010-10-19 13:51:41 1388

1388

1388

1388

T213 2-N-16可变进制计数器的应用电路图

T213计数器内部由四级J-K触发器串接成四位异步计数器,它的管脚外引线排列及功用如图所示,将T213计数器的

2010-10-19 13:40:10 1557

1557

1557

1557

T212 2-8-16进制可以预置计数器的应用电路图

T212计数器和T211计数器相比,仅在内部触发器连接上略有不同,而管肢的外引线排列及功用完全和T211一致.当CP

2010-10-19 13:30:06 1222

1222

1222

1222

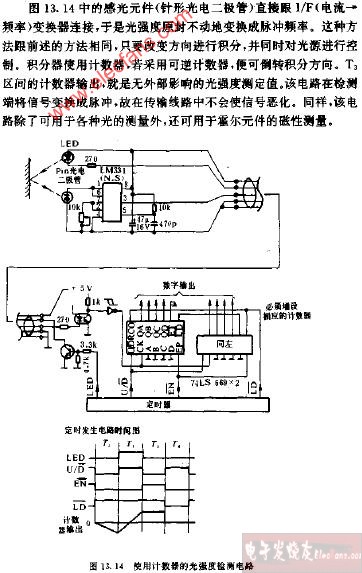

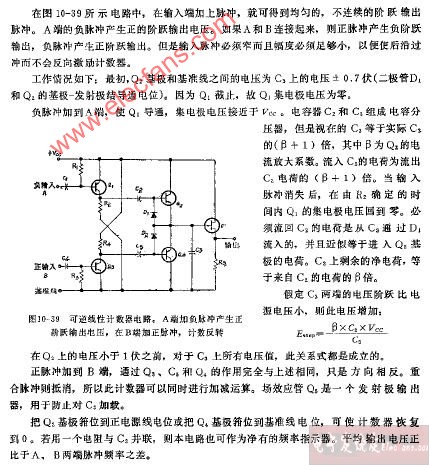

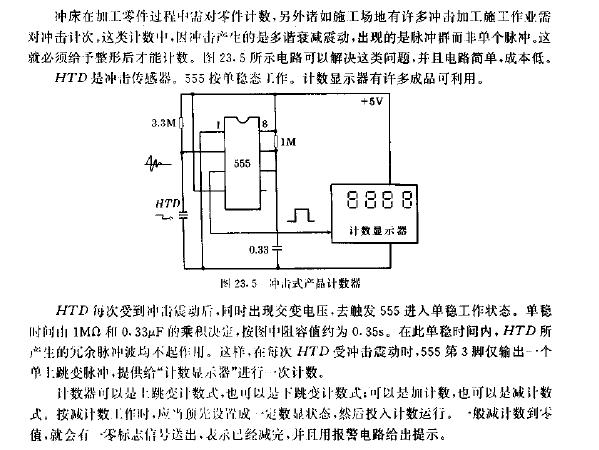

T210作N进制计数和分频器的应用电路图

T210除了作为2-5-10进制计数器外,还可以接成9以内的N进制计数器,方法是在R0端上串接二个与非门电路,各级触发器

2010-10-19 12:55:17 1344

1344

1344

1344

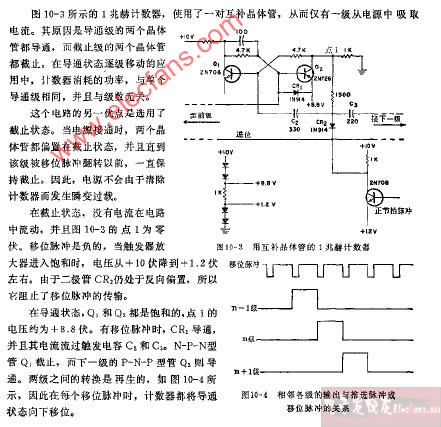

T210 2-5-10进制计数和减法计数的应用电路图

T210计数器(TTL)是异步计数器,它的内部有四个触发器,第一个触发器有独立的时钟输入CP1和输出QA,其余三个

2010-10-19 12:39:04 1723

1723

1723

1723

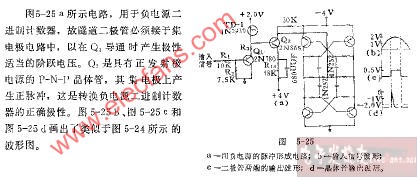

十进制计数器,十进制计数器原理是什么?

十进制计数器,十进制计数器原理是什么?

二进制计数器具有电路结构简单、运算方便等特点,但是日常生活中我们所接触的大部分都是十进制数,特

2010-03-08 13:19:54 23684

23684

23684

23684什么是二进制计数器,二进制计数器原理是什么?

什么是二进制计数器,二进制计数器原理是什么?

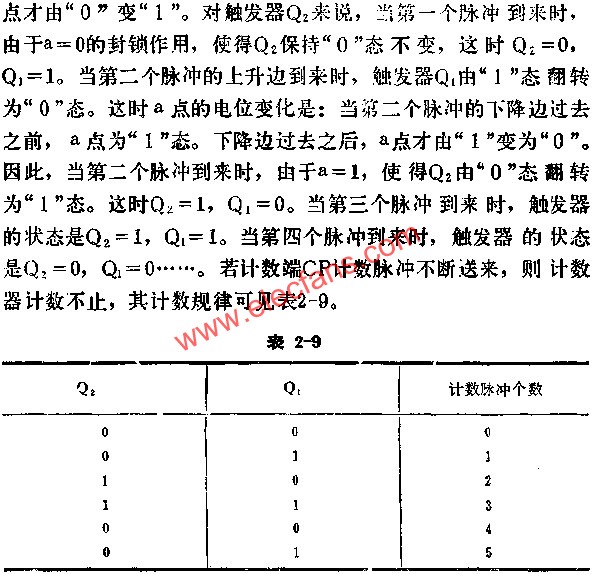

计数器是数字系统中用得较多的基本逻辑器件。它不仅能记录输入时钟脉冲的个数,还可以实现

2010-03-08 13:16:34 29984

29984

29984

2998424进制计数器电路

24进制计数器电路

在百进制基础上,采用反馈归零法即可组成二十四进制计数器。计数范围为0~23,24为过渡状态,当高位计数至2、低位计数至4

2009-09-16 15:50:29 19522

19522

19522

19522

100进制计数器

100进制计数器一、 实验目的:1、 熟悉MAX+PLUS环境的基本操作。2、 掌握VHDL和原理图的设计输入方式。3、 设计100进制计数器。二、&

2009-06-28 00:07:21 7414

7414

7414

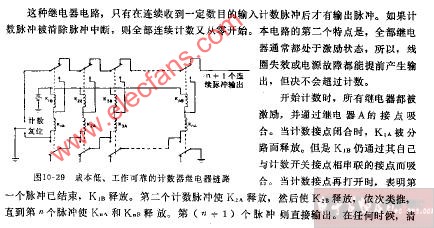

7414可逆、可预置计数器CD4029构成的任意N分频减法计数电路

图3是可逆、可预置计数器CD4029构成的任意N分频减法计数电路,U/D接“L”电平进行减法计数,B/D接“L”电平按BCD输出码进行计数,低位的Co进位到高位的CT输

2009-06-22 07:44:38 4593

4593

4593

4593

电子发烧友App

电子发烧友App

评论