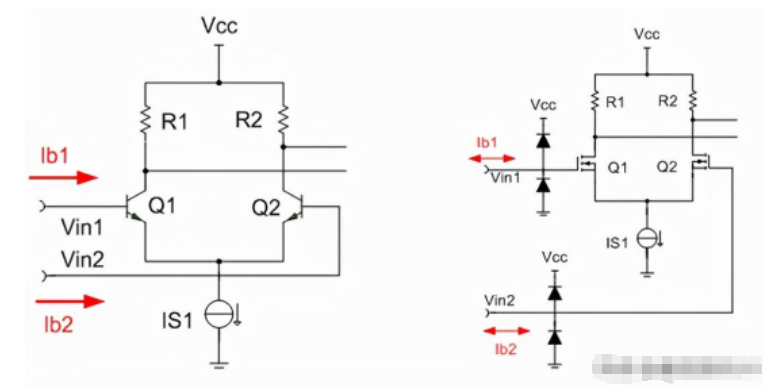

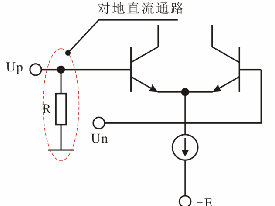

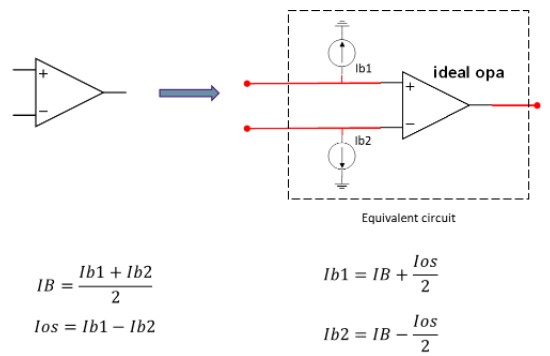

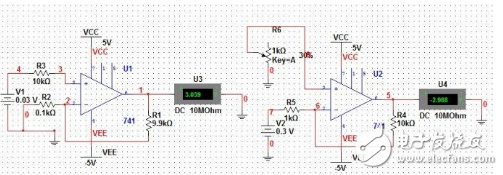

运放输入失调电流为

Ios=(Ib+)-(Ib-)

这种测试方法有几个缺点,一个是使用了很大的电阻R1和R2,一般会是M欧级,这两个电阻引入了很大的电压噪声。受到电阻R1和R2的阻值的限制,难以测得FET输入运放的偏置电流。

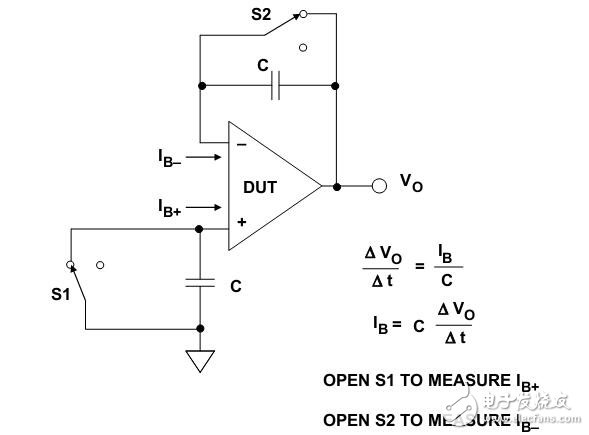

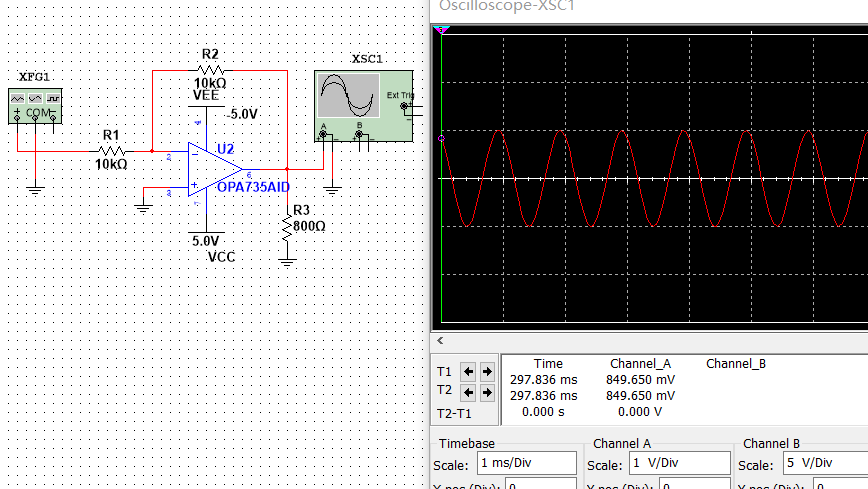

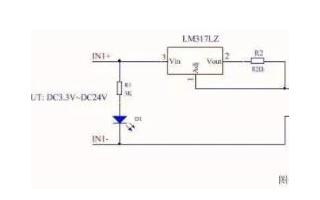

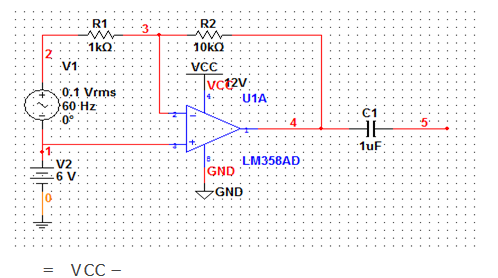

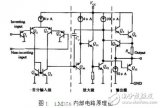

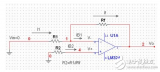

第二种方法测试方法,是让运放的输入偏置电流流入电容,具体测试如下图。从图中的公式很容易理解测试的原理,这个测试的关键,是选取漏电流极小的电容。

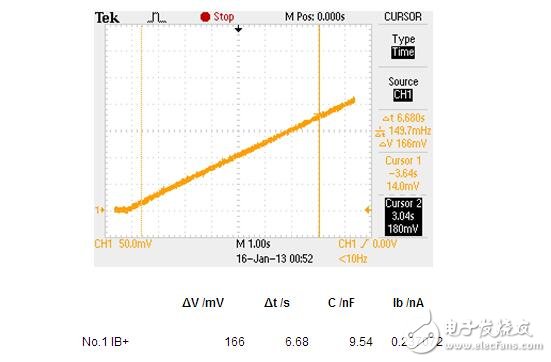

(1)打开S1,IB+流入电容C,用示波器观察Vo的变化,结果如下图,按上图的方法就可以计算出IB+。

(2)关闭S1打开S2,IB-流入电容C,用示波器观察Vo的变化,结果如下图,可以计算出IB-。

(3)再根据定义就可以计算出运放的输入偏置电流和失调电流。

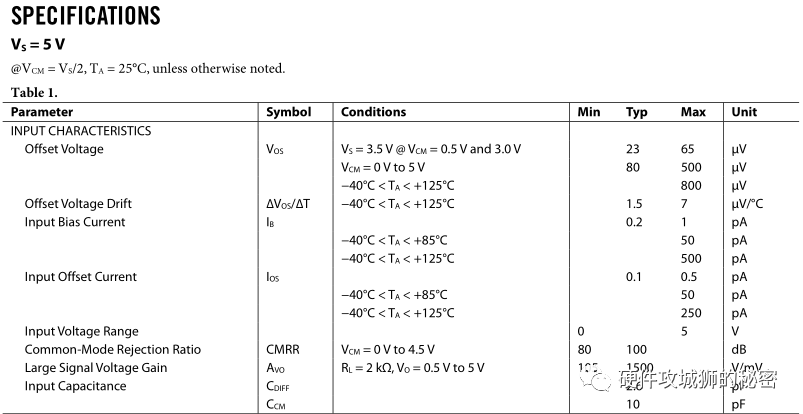

这种测试方法可以测得fA级的失调电流。测试时需要选用低漏电流的电容,推荐使用极低漏电流的特氟龙电容,聚丙烯(PP)电容或聚苯乙烯电容。

再分享一个经验,就是贴片电容在焊接过程中,由于引脚可能残留焊锡膏等杂质,会使FET运放的漏电流大大的增加。曾经测试一个偏置电流为小于10pA级的运放,由于没有对引脚 进行清洗,结果测得结果出现了很大的误差,或者叫差错,达了nA的水平了。

电子发烧友App

电子发烧友App

评论