一、一位数值比较器

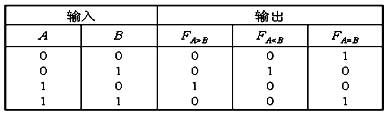

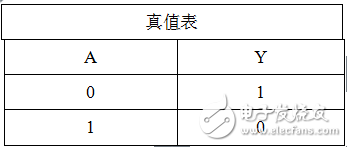

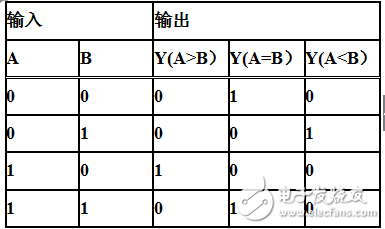

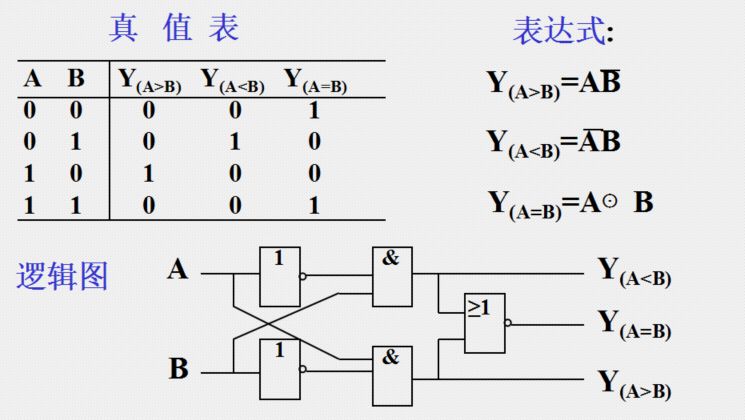

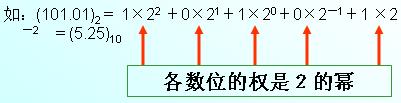

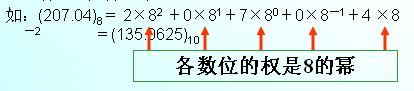

1位数值比较器是多位比较器的基础。当A和B都是1位数时,它们只能取0或1两种值,由此可写出1位数值比较器的真值表:

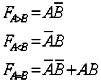

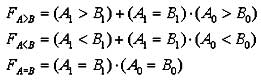

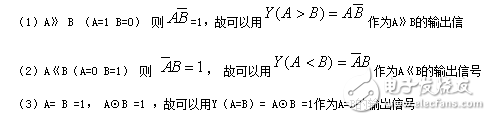

由真值表得到如下逻辑表达式:

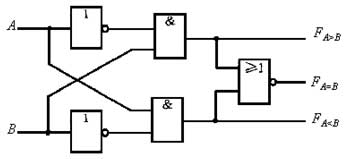

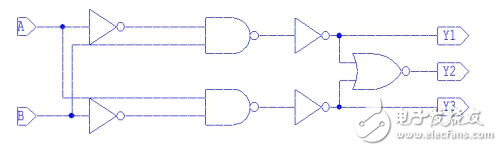

由以上逻辑表达式可画出如下图所示的逻辑电路。实际应用中,可根据具体情况选用逻辑门。

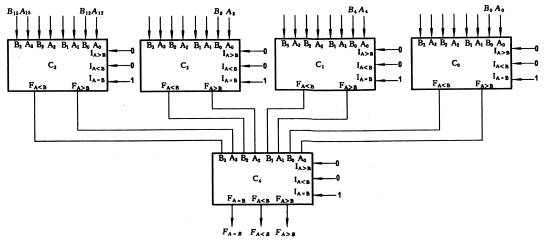

二、两位数值比较器

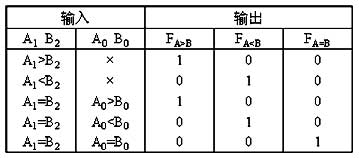

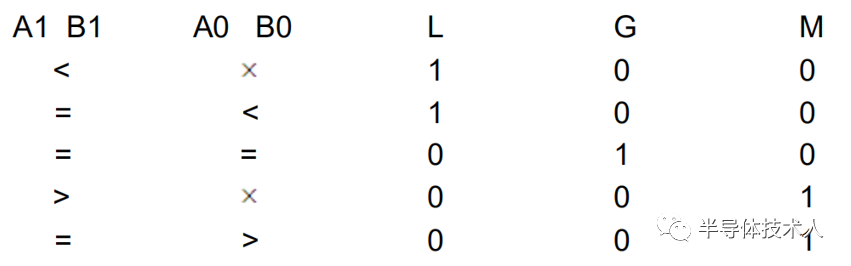

现在分析比较两位数字A1A0和B1B0的情况。

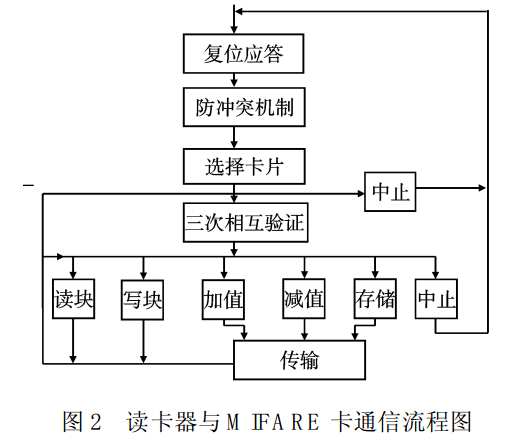

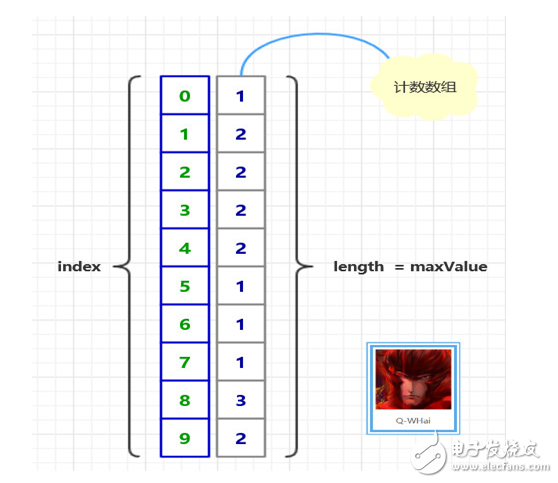

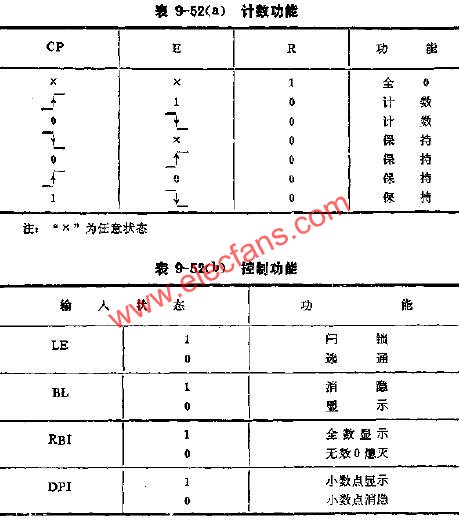

为了减少符号的种类,不再使用字母L,而以(Ai>Bi)、(Ai<Bi)、(Ai=Bi)直接表示逻辑函数。可以由真值表对两位比较器作如下简要概述。

当高位相等时,两数的比较结果由低位比较的结果决定。

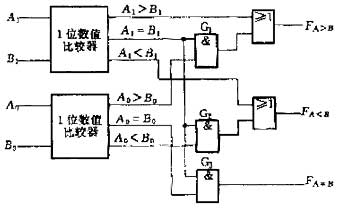

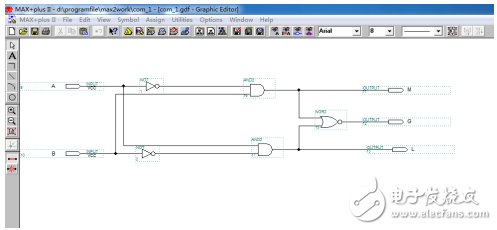

根据表达式画出逻辑图:

电路利用了1位数值比较器的输出作为中间结果。它所依据的原理是,如果两位数A1A0和B1B0的高位不相等,则高位比较结果就是两数比较结果,与低位无关。这时,由于中间函数(A1=B1)=0,使与门G1、G2、G3均封锁,而或门都打开,低位比较结果不能影响或门,高位比较结果则从或门直接输出。如果高位相等,即(A1=B1)=1,使与门G1、G2、G3均打开,同时由(A1>B1)=0和(A1<B1)=0作用,或门也打开,低位的比较结果直接送达输出端,即低位的比较结果决定两数谁大、谁小或者相等。

三、一位数据比较器电路的设计

1.设计目的

(1) 了解EDA技术的发展及应用

(2) 掌握VHDL语言的基础知识,熟悉在数字电路系统设计中VHDL程序设计

(3) 学习MAX+PLUSⅡ软件的应用方法

(4) 应用EDA技术的设计方法完成4位右移移位寄存器的设计(采用原理图和文本法两种方法实现),并在MAX+PLUSⅡ上仿真

2 、关于MAX+PlusⅡ的使用与仿真

2.1、 MAX+plus2软件简介

MAX+plusII是Altera公司提供的一个集成化开发系统,该系统界面友好,学习容易,使用简单,功能齐全,是一款流行的EDA开发平台。

MAX+PLUSII把这些设计转自动换成最终所需的格式。其设计速度非常快。对于一般几千门的电路设计,使用MAX+PLUSII,从设计输入到器件编程完毕,用户拿到设计好的逻辑电路,大约只需几小时。设计处理一般在数分钟内完成。特别是在原理图输入等方面,Maxplus2被公认为是最易使用,人机界面最友善的PLD开发软件,特别适合初学者使用。

EDA (Electronic Design Automation)

EDA技术就是依靠功能强大的电子计算机,在EDA 工具软件平台上,对以硬件描述语言HDL为系统逻辑描述手段完成的设计文件,自动地完成逻辑编译、化简、分割、综合、优化、仿真,直至下载到可编程逻辑器件CPLD/FPGA或专用集成电路ASIC芯片中,实现既定的电子电路设计功能。

2.2、MAX+plus2 使用方法简要说明

MAX+plus2硬件平台的微机最好配置512MB内存、4,3GMB硬盘,可以在Windows XP等操作系统支持下工作。在进行了MAX+plus2的系统安装和系统启动后,对于所要设计和仿真的系统需要进行如下基本步骤:

(1)VHDL语言工程文件的建立和编辑;

文件的建立:新建文件(file/new/text editor file)、输入文本(text editor)、保存文件(file/save);文件的修改:打开需修改文件(file/open/*.vhd)、修改(text editor)、保存 (file/save);

(2)电路图的建立和编辑

建立文件打开图形编辑器,选择file/save as建立.gdf文件、输入所需元件及电路模块、编辑端口名称、对各电路块及输入/输出端口进行连线、在设计过程中,可以随时对已进行工作进行保存;

(3)VHDL语言程序的编译

编译的目的:生成可以进行仿真、定时分析及下载到可编程器件的相关文件。

编译的步骤:打开需编译源程序(file/open)、编译(MAX+ plus II/compiler)、为当前文件建立项目(file/project/set project to current file);

(4)VHDL语言程序的仿真

VHDL程序的仿真过程大致可以分为三个步骤:生成波形文件、仿真、定时分析。

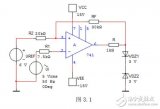

3、基本门电路

CMOS组成的门

本次课程设计需要一些简单的电路,我们开始先介绍简单的电路。本实验中只用到TTL和CMOS组成的与门、非门两种门电路

工作原理:

当V(IN)=0V NMOS管截止,PMOS管导通,V(OUT)=VDD=5V

当V(IN)=5V PMOS截止,NMOS管导通,V(OUT)=0V

4、数值比较器

4.1 1、数值比较器

1位数值比较器:比较输入的两个1位二进制数A、B的大小。我们输入信号是两个要进行比较的1位二进制数,现在用A、B表示,输出信号是比较结果

三种情况如下

它的真值表如下

由上述表达式及其真值表我们可知的1位数比较器设计比较成功。

1位数比较器逻辑图如下

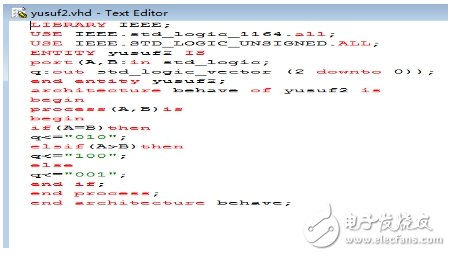

5、数值比较器的VHDL程序及仿真结果

5.1 、关于1位数值比较器的VHDL程序及仿真

VHDL程序如下

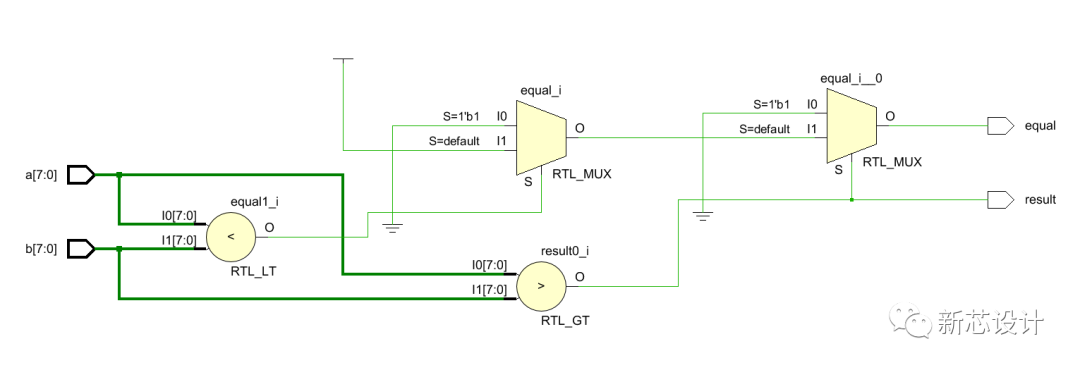

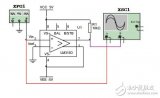

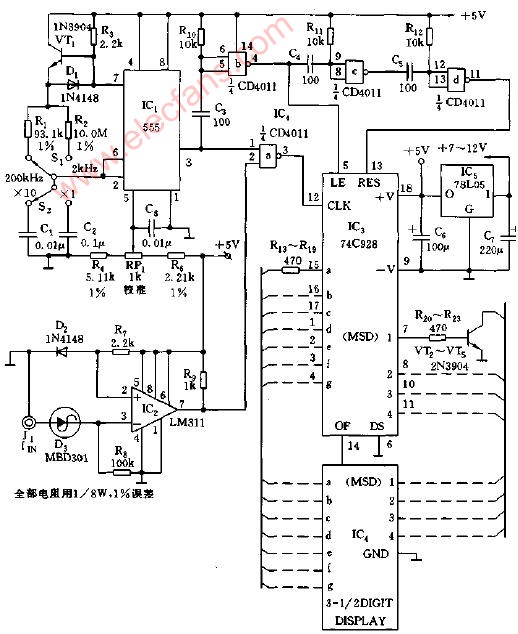

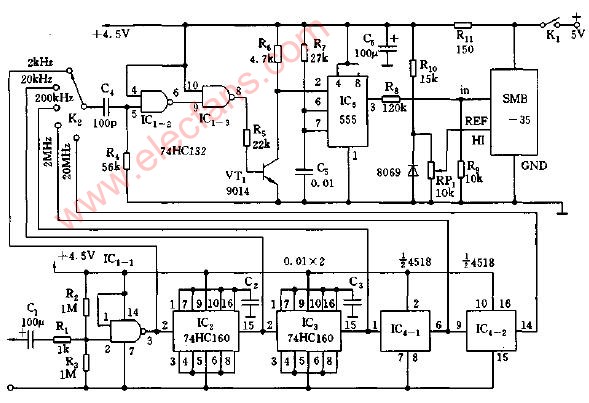

一位数值比较器的逻辑电路图

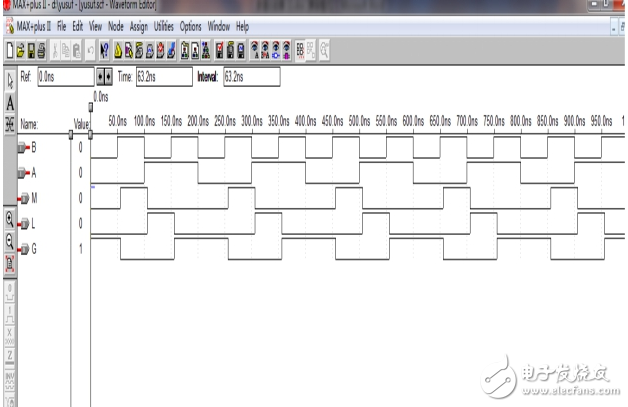

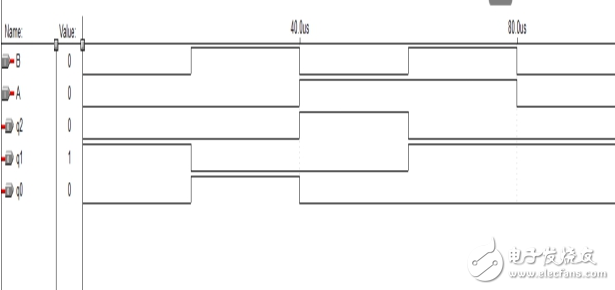

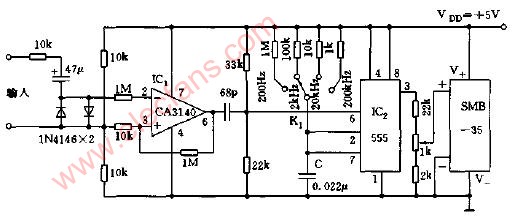

仿真波形如下:

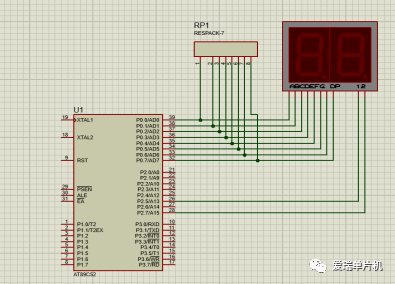

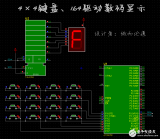

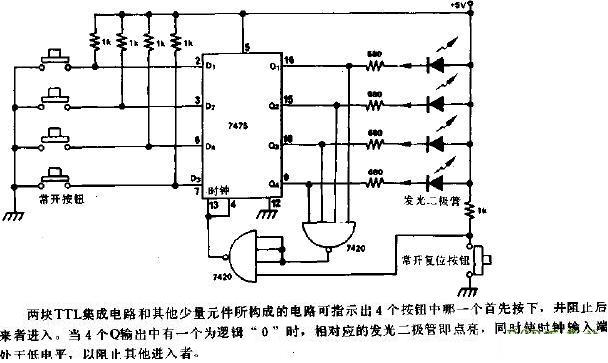

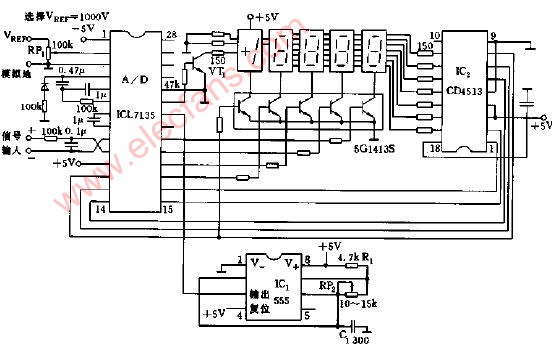

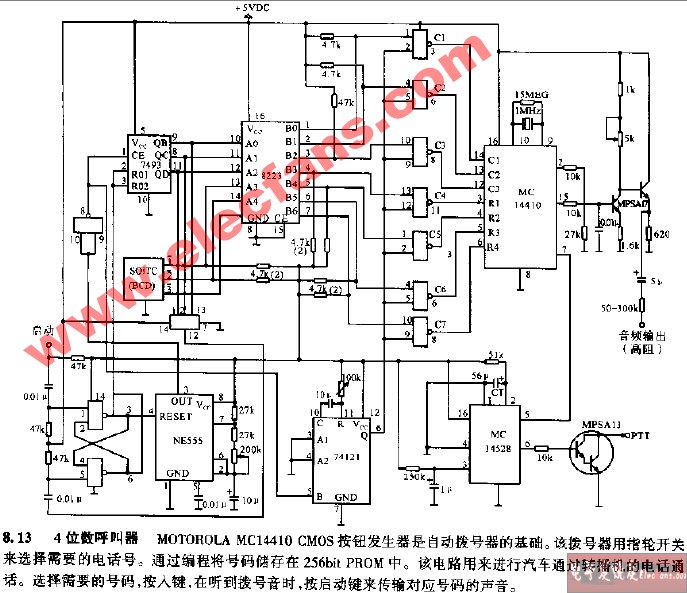

实事接线图

电子发烧友App

电子发烧友App

评论