时钟发生器由哪些部分组成?锁相环pll的特点是什么?如何用硬件配置pll 时钟发生器是指通过特定的电路设计产生适合各种电子设备使用的时钟信号的器件。时钟发生器由多个部分组成,其中最核心的是锁相环

2023-10-13 17:39:50 99

99 9ZXL1951D PCIe 时钟发生器评估板用户指南

2023-07-07 19:19:11 0

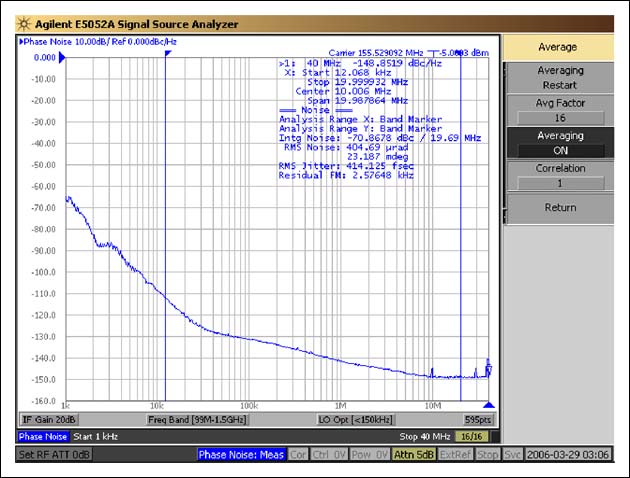

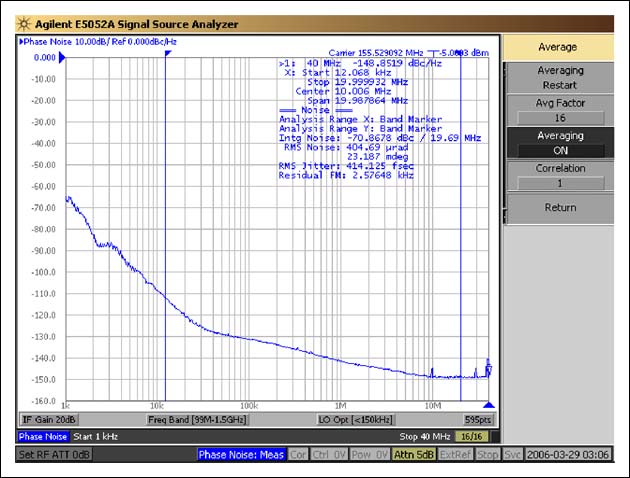

0 本文讨论电源噪声干扰对基于PLL的时钟发生器的影响,并介绍几种用于评估由此产生的确定性抖动(DJ)的测量技术。派生关系显示了如何使用频域杂散测量来评估时序抖动行为。实验室台架测试结果用于比较测量技术,并演示如何可靠地评估参考时钟发生器的电源噪声抑制(PSNR)性能。

2023-04-11 11:06:39 478

478

9ZXL1951D PCIe 时钟发生器评估板用户指南

2023-03-21 19:21:13 0

0 CY25200是一种具有扩频功能的可编程时钟发生器。扩频在小范围内调制输出时钟频率,扩展能量并降低能量峰值。这是一种在各种应用中降低EMI的强大技术。它使用外部参考时钟或晶体作为输入。它还使用PLL生成扩展频谱输出时钟,该时钟可以与输入频率不同。最多有六个输出时钟可用,其中两个可以是REFCLK。

2023-02-14 16:19:04 0

0 与典型的“本地”时钟解决方案相比,使用集成的多输出时钟发生器具有许多优势。本文讨论集中式时钟发生器(如MAX9489和MAX9471)在降低系统成本、良好信号完整性和消除干扰方面的优势。它包括电路板设计,说明如何使用中央时钟源克服一些基本设计挑战。

2023-02-09 11:57:14 706

706

电子发烧友网为你提供Maxim(Maxim)MAX9471ETP+T相关产品参数、数据手册,更有MAX9471ETP+T的引脚图、接线图、封装手册、中文资料、英文资料,MAX9471ETP+T真值表,MAX9471ETP+T管脚等资料,希望可以帮助到广大的电子工程师们。

2023-02-07 18:34:57

电子发烧友网为你提供Maxim(Maxim)MAX9471ETP+相关产品参数、数据手册,更有MAX9471ETP+的引脚图、接线图、封装手册、中文资料、英文资料,MAX9471ETP+真值表,MAX9471ETP+管脚等资料,希望可以帮助到广大的电子工程师们。

2023-02-07 18:34:37

极景微发布超小封装PCIe5.0时钟发生器日前,极景微(UltraSilicon)宣布,推出两款支持PCIe5.0接口标准的1输出及2输出时钟发生器,分别为US6D101和US6D102。该芯片具有

2023-02-02 15:25:54 684

684

具有集成双路 VCO 的 5/10 路输出时钟发生器/抖动消除器 Function Clock generator Number of outputs 5 Output

2022-12-02 13:47:31

具有集成双路 VCO 的 4 路输出时钟发生器/抖动消除器 Function Clock generator Number of outputs 2 Output

2022-12-02 13:47:24

具有音频时钟的 3G/高清/标清视频时钟发生器 Function Clock generator Number of outputs 4 Output frequency

2022-12-02 13:47:21

超低抖动时钟发生器如何优化串行链路系统性能

2022-11-04 09:50:15 0

0 AC1571时钟发生器一款基于PLL的、适用于5G基站应用的时钟发生器。采用数字锁相环技术,以实现最佳的高频低相噪性能,具有低功耗和高PSRR能力。采用ADPLL技术,管脚兼容843N571,可以

2022-08-11 16:26:33

这是带有板上芯片(COB)的1Hz时钟发生器电路。通常,为数字时钟和计数器电路应用产生1Hz时钟的电路将IC与晶体和微调电容器等结合使用。

2022-06-07 10:43:50 1598

1598

。Cypress时钟发生器兼容大量增值性能,如VCXO,扩频和输出相位校准,及其兼容流行接口标准的参考时钟/3.0,如PCIe1.0/2.0/3.0、10GbE、SATA1.0/2.0和USB1.0

2022-04-22 09:02:09 679

679 时钟发生器AD9516-0技术手册

2022-01-25 15:59:42 4

4 集成2.5 GHz压控振荡器数据表的AD9517-1 12输出时钟发生器

2021-06-17 15:57:38 6

6 集成2.0 GHz压控振荡器数据表的AD9518-3 6输出时钟发生器

2021-06-17 15:38:27 3

3 集成2.2 GHz压控振荡器数据表的AD9517-2 12输出时钟发生器

2021-06-17 12:31:30 3

3 AD9517-0 12输出时钟发生器,集成2.8 GHz压控振荡器数据表

2021-06-16 12:14:49 4

4 AD9516-3:14输出时钟发生器,集成2.0 GHz压控振荡器数据表

2021-05-25 12:00:10 2

2 AD9516-0:14-集成2.8 GHz压控振荡器数据表的输出时钟发生器

2021-05-24 15:33:39 8

8 (ADC/DAC))和本振(LO)要求采用低抖动参考时钟以提高性能。其他基带组件也要求各种频率的时钟源。表1.时钟发生器——典型性能表2.时钟分配产品——典型性能图1.面向采用MIMO架构的典型LTE

2018-10-18 11:29:03

AD9576:双锁相环异步时钟发生器数据表

2021-05-16 12:57:55 0

0 AD9531:3通道时钟发生器,24输出数据表

2021-05-15 15:24:07 11

11 AD9575:网络时钟发生器,双输出数据表

2021-05-09 11:06:44 1

1 AD9573:PCI-Express时钟发生器IC,PLL内核,分频器,双输出数据表

2021-05-08 20:05:05 5

5 AD9520-4:12集成1.6 GHz压控振荡器数据表的LVPECL/24 CMOS输出时钟发生器

2021-05-07 09:37:39 9

9 AD9517-4:12输出时钟发生器,集成1.6 GHz压控振荡器数据表

2021-04-30 15:51:42 10

10 集成2.2 GHz VCO数据表的AD9522-2:12 LVDS/24 CMOS输出时钟发生器

2021-04-29 20:28:12 11

11 AD9522-4:12集成1.6 GHz压控振荡器数据表的LVDS/24 CMOS输出时钟发生器

2021-04-29 19:06:06 1

1 AD9516-2:14-集成2.2 GHz压控振荡器数据表的输出时钟发生器

2021-04-28 19:52:58 0

0 AD9522-5:12 LVDS/24 CMOS输出时钟发生器数据表

2021-04-28 10:53:01 0

0 AD9522-3:12集成2 GHz压控振荡器数据表的LVDS/24 CMOS输出时钟发生器

2021-04-28 10:38:36 7

7 AD9551:多业务时钟发生器数据表

2021-04-28 10:30:52 0

0 AD9516-5:14-输出时钟发生器数据表

2021-04-27 21:41:19 5

5 AD9520-5:12 LVPECL/24 CMOS输出时钟发生器数据表

2021-04-27 21:31:55 2

2 AD9530:4 CML输出、低抖动时钟发生器,集成5.4 GHz压控振荡器数据表

2021-04-24 12:02:38 0

0 AD9520-2:12集成2.2 GHz压控振荡器数据表的LVPECL/24 CMOS输出时钟发生器

2021-04-18 16:07:52 6

6 AD9516-1:14-集成2.5 GHz压控振荡器数据表的输出时钟发生器

2021-04-18 12:00:33 2

2 AD9520-1:12集成2.5 GHz压控振荡器数据表的LVPECL/24 CMOS输出时钟发生器

2021-04-18 11:48:20 8

8 AD9516-4:14-集成1.6 GHz压控振荡器数据表的输出时钟发生器

2021-04-17 20:23:00 9

9 AD9522-0:12集成2.8 GHz压控振荡器数据表的LVDS/24 CMOS输出时钟发生器

2021-04-17 20:08:52 0

0 AD9522-1:12 LVDS/24 CMOS输出时钟发生器,集成2.4 GHz压控振荡器数据表

2021-04-16 20:21:52 1

1 AD9520-3:12集成2 GHz压控振荡器数据表的LVPECL/24 CMOS输出时钟发生器

2021-04-16 18:38:03 3

3 AD9571:以太网时钟发生器,10个时钟输出

2021-04-16 10:21:56 3

3 ADF4360-9:集成压控振荡器数据表的时钟发生器PLL

2021-04-14 14:10:44 0

0 AD9517-0:12输出时钟发生器,集成2.8 GHz压控振荡器数据表

2021-04-13 12:10:21 0

0 AD9517-1:12输出时钟发生器,集成2.5 GHz压控振荡器数据表

2021-04-13 12:02:55 1

1 AD9517-2:12输出时钟发生器,集成2.2 GHz压控振荡器数据表

2021-04-13 11:57:48 0

0 AD9518-3:6输出时钟发生器,集成2.0 GHz压控振荡器数据表

2021-04-13 11:13:25 2

2 AD9540:655 MHz低抖动时钟发生器数据表

2021-03-22 19:57:57 0

0 AD9518-1:6输出时钟发生器,集成2.5 GHz压控振荡器数据表

2021-03-22 19:55:03 0

0 AD9525: 8路LVPECL输出低抖动时钟发生器

2021-03-21 15:00:20 0

0 AD9523-1:低抖动时钟发生器,14路LVPECL/LVDS/HSTL输出或29路LVCMOS输出 数据手册

2021-03-21 14:28:08 1

1 AD9520-0:12路LVPECL/24路CMOS输出时钟发生器,集成2.8 GHz VCO

2021-03-19 09:02:27 0

0 系统设计师通常侧重于为应用选择最合适的数据转换器,在向数据转换器提供输入的时钟发生器件的选择上往往少有考虑。然而,如果不慎重考虑时钟发生器的相位噪声和抖动性能,数据转换器动态范围和线性度性能可能受到严重的影响。

2020-11-22 11:34:38 2489

2489

SSDCI1108AF是减少电磁干扰(EMI)的时钟发生器。利用内调制器对振荡频率进行周期性的微调,可以使不必要的电磁干扰(EMI)峰值衰减。SSDCI1108AF接收来自基本晶体或外部基准的输入时钟,并锁定到该输入时钟,以传递1x调制时钟输出。

2020-04-17 08:00:00 10

10 新型AEC-Q100认证的时钟发生器、缓冲器、PCIe时钟和缓冲器满足广泛的车辆自动化应用需求。

2019-09-24 14:25:08 828

828 AD9523:14路LVPECL/LVDS/HSTL输出 或29路LVCMOS输出 低抖动时钟发生器

2019-07-04 06:18:00 3365

3365 据麦姆斯咨询报道,Microchip推出了业界尺寸最小的MEMS时钟发生器DSC613。这款新器件可在电路板上最多替换掉三个晶振和振荡器,从而减少高达80%的时钟元件布板空间。

2018-11-15 16:38:26 3736

3736 Microchip基于MEMS的时钟发生器

2018-07-08 01:23:00 3691

3691 Microchip基于MEMS的时钟发生器

2018-06-07 13:46:00 4241

4241

系统设计师通常侧重于为应用选择最合适的数据转换器,在向数据转换器提供输入的时钟发生器件的选择上往往少有考虑。然而,如果不慎重考虑时钟发生器、相位噪声和抖动性能,数据转换器、动态范围和线性度性能可能受到严重的影响。

2017-11-17 02:00:58 671

671

10GHz扩频时钟发生器的设计_胡帅帅

2017-01-07 21:28:58 1

1 一种占空比可调的两相非重叠时钟发生器_张学敏

2017-01-05 15:06:09 5

5 双环路时钟发生器可清除抖动并提供多个高频输出

2016-01-04 17:41:13 17

17 Pericom推出一项全新的HiFlex时钟发生器产品系列,该系列产品可提供多频率输出,同时具有超低噪声(抖动)、高集成度及高灵活性的特点,完美地适用于网络、云计算和其他需要多频率及输出的高性能平台。

2013-01-29 09:14:04 1000

1000 Silicon Laboratories (芯科实验室有限公司)日前宣布扩展其PCI Express(PCIe)时钟发生器和时钟缓冲器产品组合。

2012-02-02 09:31:56 1356

1356 MAX3636是一个高度灵活,高精度锁相环(PLL)时钟发生器为下一代网络设备的要求低抖动时钟发生器和强大的高速数据传输的分布进行了优化。

2011-10-11 11:15:22 1267

1267

德州仪器(TI)日前宣布推出一款具有业界最佳抖动性能的高度集成的时钟发生器。LMK03806可以帮助设计人员运用一个低成本晶体合成所需的时钟频率

2011-10-10 09:19:30 1072

1072 在有效抑制EMC 干扰的扩频时钟发生器(SSCG)中内置FRAM 的新产品MB88R157A 被纳入富士通的产品阵容。针对10MHz ~ 50MHz 的输入频率,该产品的输出时钟频率可以在1MHz ~ 134MHz 范围内任意设

2011-08-31 17:26:32 40

40 在电力系统、CDMA2000、DVB、DMB等系统中,高精度的GPS时钟发生器(GPS同步时钟)对维持系统正常运转有至关重要的意义。

那如何利用GPS OEM来进行二次开发,产生高精度时钟发生

2010-09-17 22:02:44 1233

1233 如何利用GPS OEM来进行二次开发,产生高精度时钟发生器是一个研究的热点问题。在电力系统、CDMA2000、DVB、DMB等系统中,高精度的GPS

2010-07-24 15:45:26 748

748 MAX3679A高性能四路输出时钟发生器(Maxim)

Maxim推出用于以太网设备的高性能、四路输出时钟发生器MAX3679A。器件采用低噪声

2010-04-14 16:51:49 722

722 MAX3625B 抖动仅为0.36ps的PLL时钟发生器

概述

MAX3625B是一款低抖动、精密时钟发生器,优化用于网络设备。器件内置晶体振荡器和锁相环(PLL)

2010-03-01 08:56:18 1282

1282

MAX3625B是一款低抖动、精密时钟发生器,优化用于网络设备。器件内置晶体振荡器和锁相环(PLL)时钟倍频器,以产生高频时钟输出,用于以太网、10G光纤通道及其它网络设备。Ma

2010-03-01 08:54:52 126

126 Maxim推出高性能、三路输出时钟发生器MAX3625B

Maxim近日推出高性能、三路输出时钟发生器MAX3625B,适用于以太网和光纤通道网络设备。器件采用低噪声VCO和PLL架构,能够

2009-12-14 17:25:04 1001

1001 针对直接数字频率合成(DDS)和集成锁相环(PLL)技术的特性,提出了一种新的DDS 激励PLL 系统频率合成时钟发生器方案。且DDS 避免正弦查找表,即避免使用ROM,采用滤波的方法

2009-12-14 10:22:00 36

36 MAX3624 低抖动、精密时钟发生器,提供四路输出

概述

MAX3624是一款低抖动精密

2009-09-18 08:56:41 632

632

评估低抖动PLL时钟发生器的电源噪声抑制性能

本文介绍了电源噪声对基于PLL的时钟发生器的干扰,并讨论了几种用于评估确定性抖动(DJ)的技术方案。推导出的关系式提

2009-09-18 08:46:32 1424

1424

MAX3625A 低抖动、精密时钟发生器,提供三路输出

2009-08-13 13:01:27 805

805

摘要:与典型的“本地”时钟方案相比,集成的多输出时钟发生器有许多优势。本文探讨了集中时钟发生器(如MAX9489和MAX9471)的优点,如:降低系统成本、良好的信号完整性、抑制干

2009-05-03 11:07:05 616

616

摘要:与典型的“本地”时钟方案相比,集成的多输出时钟发生器有许多优势。本文探讨了集中时钟发生器(如MAX9489和MAX9471)的优点,如:降低系统成本、良好的信号完整性、抑制干

2009-04-22 10:11:53 392

392

摘要:MAX9450/MAX9451/MAX9452是集成了VCXO,具有相同PLL内核和三种不同输出(LVPECL, HSTL,LVDS)的高精度时钟发生器。MAX945x时钟发生器具有四个主要的特点:集成VCXO,工作频率范围宽,PLL

2009-04-22 09:42:01 913

913

振荡器时钟发生器电路图

2009-04-13 08:54:22 699

699

精密时钟发生器电路图

2009-03-25 09:35:22 960

960

Si5338 业界首个任意频率、任意输出的时钟发生器

高性能模拟与混合信号领导厂商Silicon Laboratories日前发表全新的时钟发生器和缓冲器系列,可为业

2008-11-10 09:39:44 1654

1654 MAX9471, MAX9472 多输出时钟发生器,提供双PLL和OTP

MAX9471/MAX9472器件输出一组消费类产品中最

2008-10-04 20:47:43 642

642

The MAX9471/MAX9472 multipurpose clock generatorsare ideal for consumer and communication

2008-10-04 20:45:42 12

12 MAX9489时钟发生器提供多时钟输出,十分适合网络路由器。MAX9489提供15路缓冲时钟输出,每一路都可以独立地调节到10个频率中的任意一个:133MHz、125MHz、100MHz、83MHz、80MHz、66MHz、62

2008-06-23 11:16:46 8

8

电子发烧友App

电子发烧友App

评论