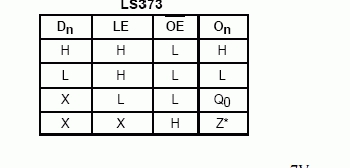

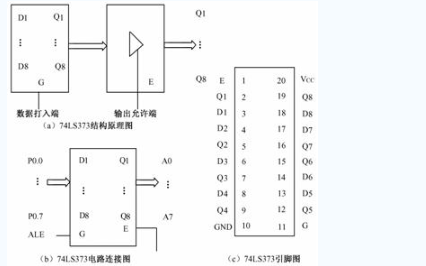

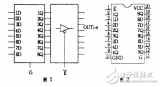

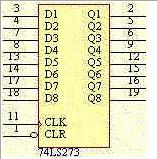

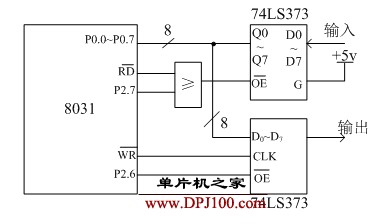

74LS373是透明的带有三态门的八D锁存器,其原理结构如图l所示,当三态门的使能信号线CE为低电平时,三态门处于导通状态,允许Q端输出}CE为高电平时,输出三态门断开,输出端对外电路呈高阻状态。G端控制锁存器的状态.当G为高电平时,锁存器输出(1Q~8Q)状态和输入端(1D~8D)状态相同;G端从高电平返回低电平(下降沿)时,输入端(1D~8D)的数据锁入1Q~8Q中。

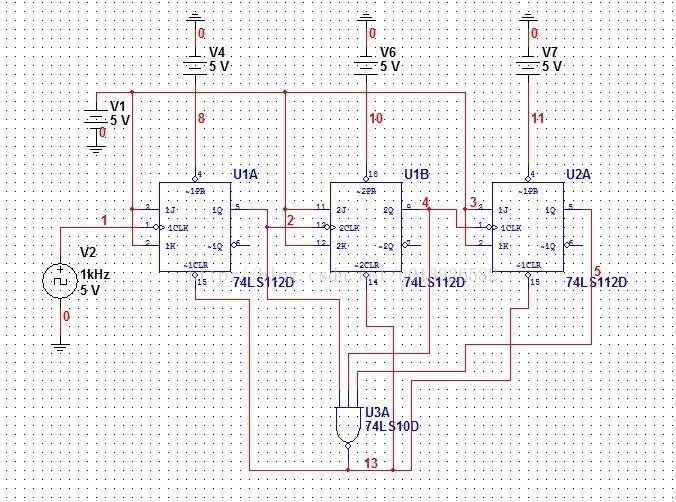

8D锁存器74LS373的允许端G的控制信号不是周期固定的脉冲信号,而是将取自锁存器输出端的信号处理后得到的,保证电路结构最简洁、处理时间最快捷,同时减少了脉冲源存在可能带来的干扰,使电路性能更可靠

小编推荐:74ls373引脚图及功能_工作原理_逻辑电路真值表_参数及应用电路

74ls373电路结构与工作原理

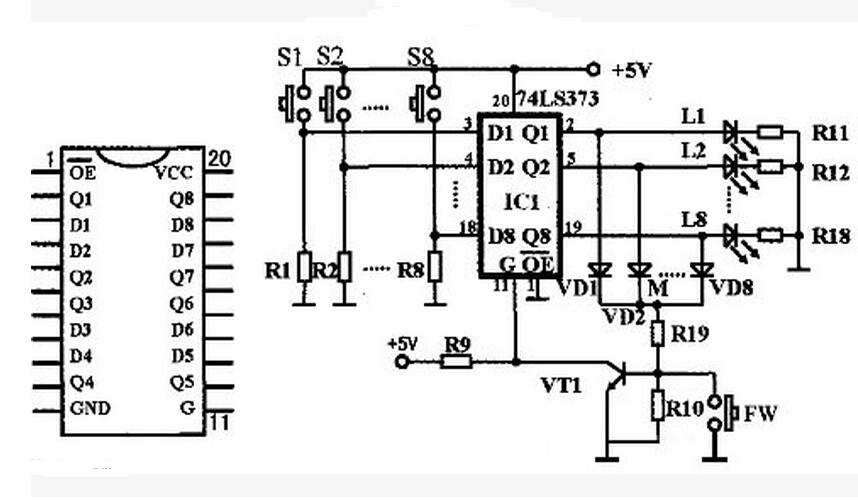

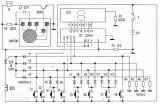

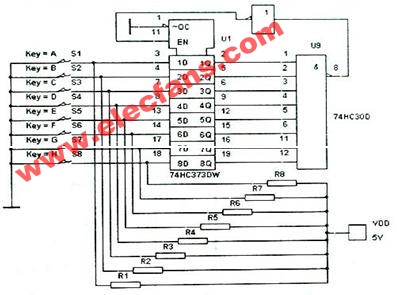

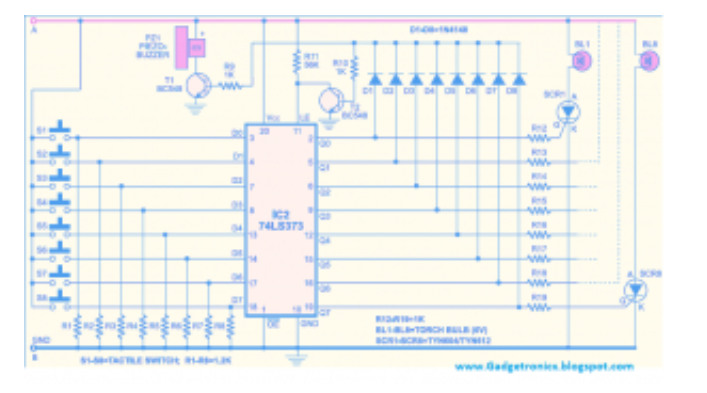

利用74LS373设计的抢答器电路它由一片8D锁存器74LS373。8只组别按键开关S1-S8,8组别抢答有效的状态显示发光二极管L1-L8,一个复位按键FW等组成。

该8路竞赛抢答器,每组受控于一个抢答按键开关,高电平表示抢答有效。

设置主持人控制键FW用于控制整个系统清0和抢答有效开始控制的启动。每按下一次复位键FW时,使8D锁存器的控制端G为高电平,若组别按键开关S1~S8中任何一个都没按下,即对应8D锁存器的输入端D均为低电平,则此时8个输出端均为低电平,对应的发光二极管均不点亮,表示抢答者正在准备抢答状态。按下复位键FW时,8D锁存器的控制端G为高电平,若组别按键开关S1-S8中存在一个或几个处于按下状态,即与之对应的8D锁存器的输入端D为高电平,此时与之对应的8D锁存器的输出端立即为高电平,对应的发光二极管被点亮,表示抢答者违规了。只有每按下一次复位键FW,并在复位键FW抬起后,抢答才是有效的。

系统具有第一抢答信号鉴别和锁存功能。在主持人将系统复位并使抢答 有效开始后,第一抢答者按下抢答按钮。对应的输入引脚接高电位1,8D锁存器的对应输出端立即为高电平1。二极管VD1-VD8组成了或门电路。使三极管VT1基极得到高电位而饱和导通使锁存器的G为低电平,将8D锁存器的输入信号锁存在了输出端,输入端的信号变化将不在影响输出端。对应点亮的发光二极管指示出第一抢答者的组别。

在显示有效的组别的同时,也可同时采用蜂鸣器警示。

抢答器设计器件选择与电路制作

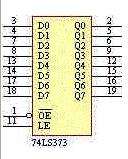

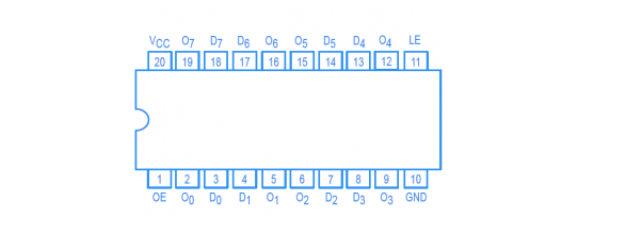

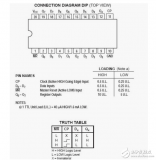

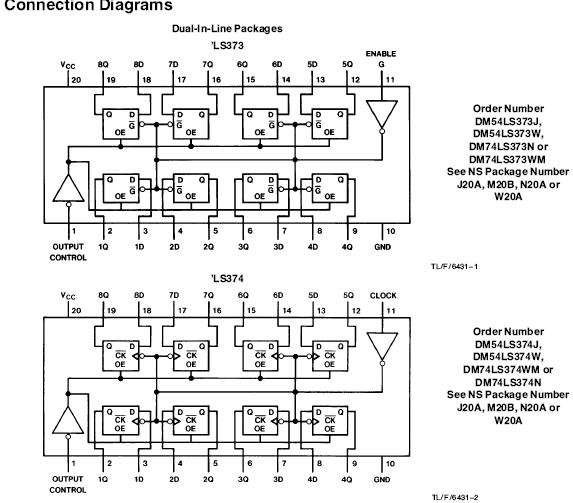

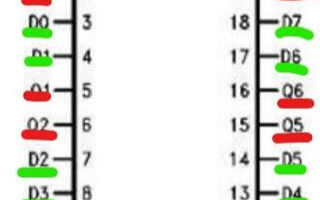

8D锁存器选择74LS373,其引脚排列图如图2示。若选择其它型号的,要注意控制端电平的要求,及其它的使能端。8只组别按键开关S1-S8、复位按键FW可选择AN8系列车床控制用按钮。8组别抢答有效的状态显示用发光二极管L1~L8选用φ10的高亮LED;三极管VT1选择S9014,电阻R1-R8选择025W/5.1kΩ,R11~R18选择~25W/430Ω,R9和R10选择0.25W/5.1kΩ,R19选择0.25W,5,10Ω,二极管VDl~VD8选择IN4148。

图 2

电路采用单5V电源供电,制作时可使用7805稳压集成电路获得。

制作时,抢答按键、指示LED可通过接线端子从线路板上引出,方便于使用。

组装焊接无误,即能保证可靠工作。

电子发烧友App

电子发烧友App

评论