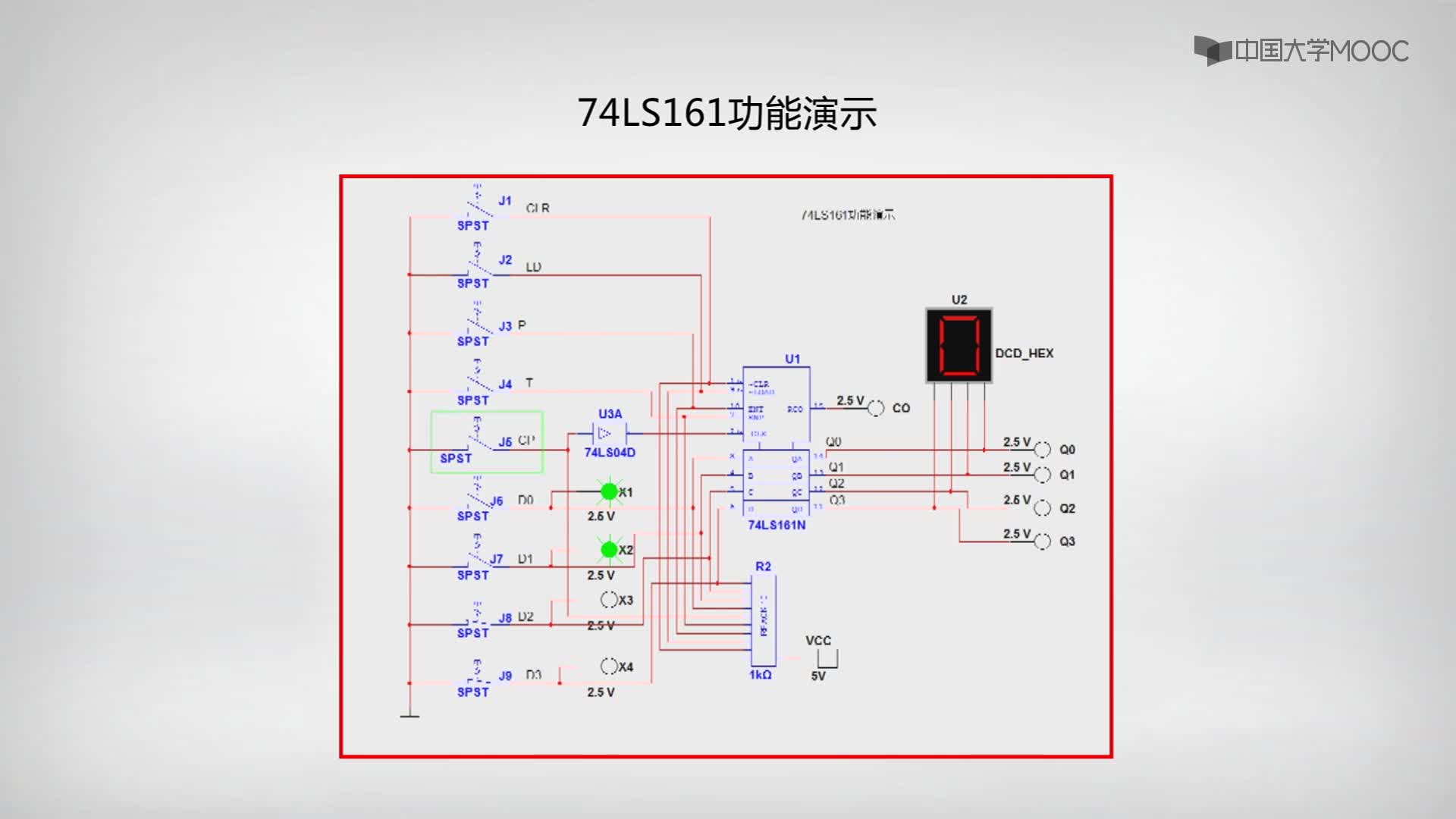

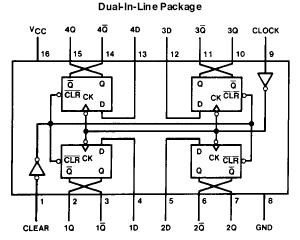

2.2、字组产生器输出字组的设计

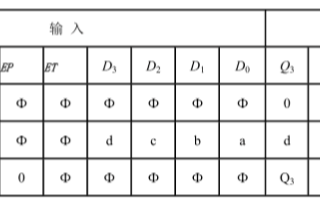

所设计的各字数据为0,2,3,2,3,2,3,2,3,2,3,2,3,2,3,2,3,2,3,2,3,2,如图2所示。

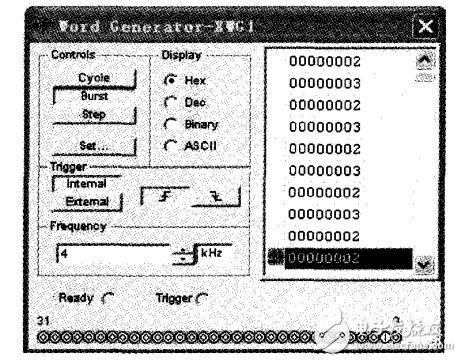

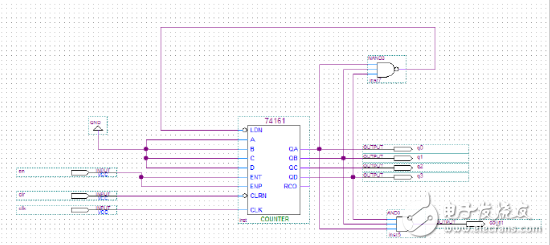

在字组产生器的数据栏内以十六进制(Hex)依次输入各字组数据,并对最后一个字数据进行末地址设置(SetFinalPosition),完成所有字组信号的设置,如图3所示。

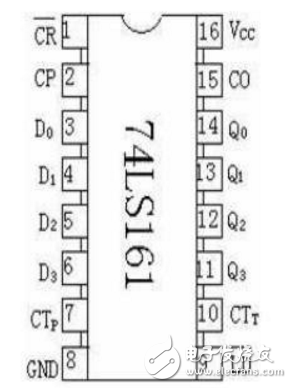

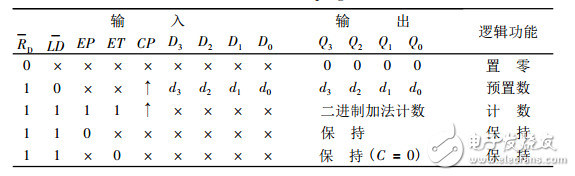

图3 集成计数器74LS161仿真实验字组信号的设置

2.3、仿真运行分析

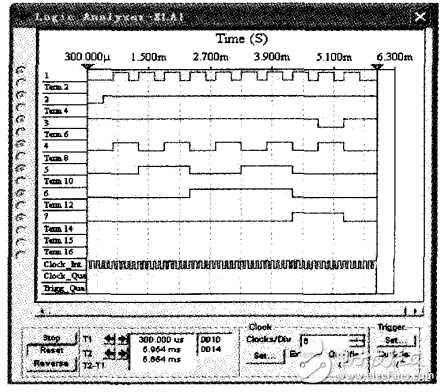

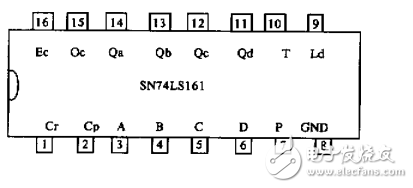

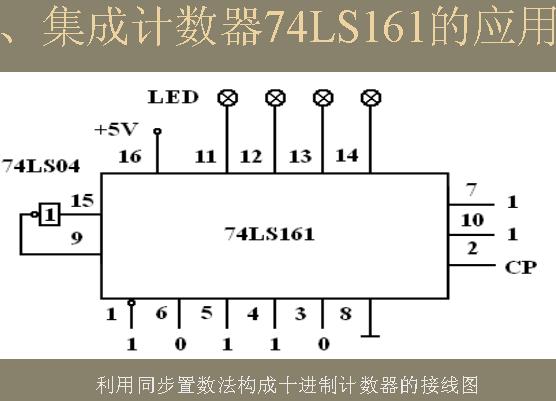

逻辑仪分析显示波形如图4所示。

图4 集成计数器74LS161仿真实验波形

图4中,“1”为时钟脉冲/CLK的波形;“2”为异步置0信号/CLR的波形;“3”为预置数控制信号/LOAD的波形;“4”~“7”为状态输出信号QA~QD的波形。

由图4可知,/CLR一0时将计数器置于0000初始状态;/CLR=1时,从0000~1001状态,预置数控制信号/LOAD=1,计数器在时钟脉冲/CLK作用下按计数方式工作;在1001状态预置数控制信号/LOAD一0,计数器在时钟脉冲/CLK作用下按预置数方式工作,使QAQBQcQD—ABCD一0000。

3、结语

由于受实验仪器的限制无法对计数器工作波形进行硬件实验验证,主要是,现有的信号发生器不能产生多路同步信号,现有的示波器多为双踪示波器无法同时观测多路波形,用Multisim软件仿真解决了这一问题,所述方法具有实际应用意义。

电子发烧友App

电子发烧友App

评论