硬件电路设计

单片机最小系统

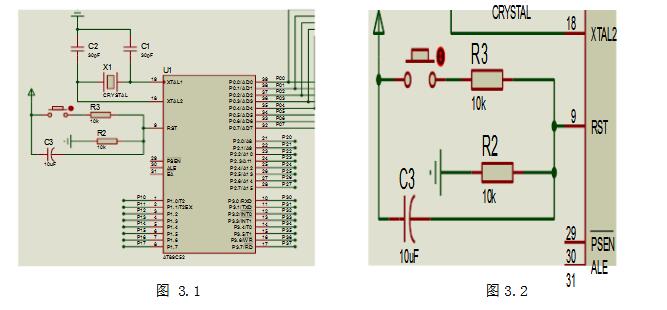

本系统以AT89C52单片机为核心,本系统选用12MHZ的晶振,使得单片机有合理的运行速度。起振电容30pF对振荡器的频率高低、振荡器的稳定性和起振的快速性影响较合适,复位电路为按键高电平复位。AT89C52单片机最小系统电路设计如图3.1所示:

复位电路

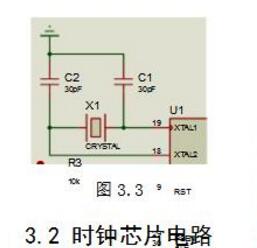

单片机复位的条件是当单片机振荡器工作时,RST引脚上出现持续两个机器周期的高电平,从而实现复位操作,使单片机回复到初始状态。上电时,考虑到振荡器有一定的起振时间,RST引脚上高电平必须持续10ms以上才能保证有效复位。 STC89C52的复位是由外部的复位电路来实现的。电路图如图3.2。

晶振电路

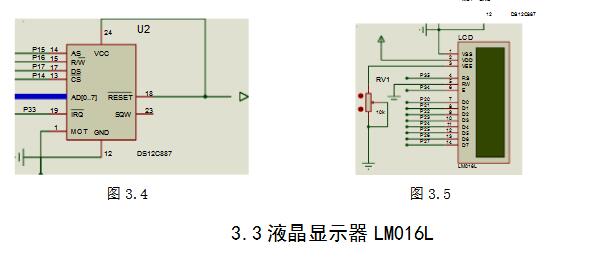

晶振的作用是为系统提供基本的时钟信号。晶振电路中接在晶振旁的两个电容,叫负载电容。一般单片机的晶振工作于并联谐振状态,也可以理解为谐振电容的一部分。电容值无严格要求,但电容取值对振荡频率输出的稳定性、大小、振荡电路起振速度有少许影响,C2、C3可在30pF时振荡器有较高的频率稳定性电路图如图3.3。

本系统采用DS12C887时钟芯片定时及计时功能,DS12C887时钟芯片共需要13条信号线。GND、 VCC:直流电源,其中VCC接+5V输入,GND接地,当VCC输入为+5V时,用户可以访问DS12C887内RAM中的数据,并可对其进行读、写操作;当VCC的输入小于+4.25V时,禁止用户对内部RAM进行读、写操作,此时用户不能正确获取芯片内的时间信息;当VCC的输入小于+3V时,DS12C887会自动将电源发换到内部自带的锂电池上,以保证内部的电路能够正常工作 MOT:模式选择脚。SQW:方波输出脚,当供电电压VCC大于4.25V时,SQW脚可进行方波输出。AD0~AD7:复用地址数据总线,该总线采用分时复用技术,在总线周期的前半部分,出现在AD0~AD7上的是地址信息,可用以选通DS12C887内的RAM,总线周期的后半部分出现在AD0~AD7上的数据信息 AS:地址选通输入脚。DS/RD:数据选择或读输入脚,该引脚有两种工作模式,当MOT接VCC时,选用Motorola工作模式,在这种工作模式中,每个总线周期的后一部分的DS为高电平。

在读操作中,DS的上升沿使DS12C887将内部数据送往总线AD0~AD7上,以供外部读取在写操作中,DS的下降沿将使总线 AD0~AD7上的数据锁存在DS12C887中。当MOT接GND时,选用Intel工作模式,在该模式中,该引脚是读允许输入脚 R/W:读/写输入端,该管脚也有2种工作模式,当MOT接VCC时,R/W工作在Motorola模式CS:片选输入,低电平有效 IRQ:中断请求输入,低电平有效,该脚有效对DS12C887内的时钟、日历和RAM中的内容没有任何影响,仅内部的控制寄存器有影响,在典型的应用中,RESET可以接VCC,这样可以保证DS12C887在掉电时,其内部控制寄存器不受影响。

DS12C887电路如图3.4所示:

液晶显示器LM016L的VSS脚接地,VDD脚接电源,VEE脚接一可变电阻接地,RS脚接单片机P3.5脚,E脚接单片机P3.4脚,D0至D7脚接单片机的P2.0至P2.7脚。液晶显示器LM016L电路图如图3.5。

软件体统设计

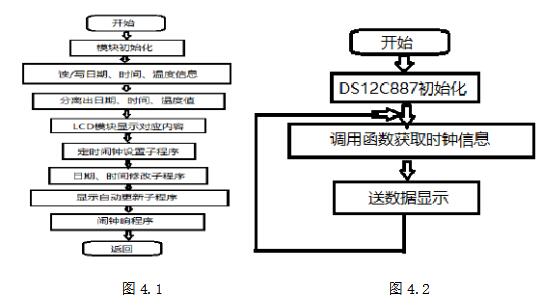

主程序流程图如图4.1

DS12C887程序流程图如图4.2。

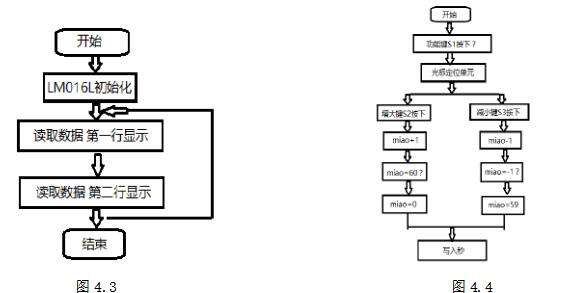

LM016L程序流程图如图4.3

电子发烧友App

电子发烧友App

评论