ad630应用电路:锁相放大电路

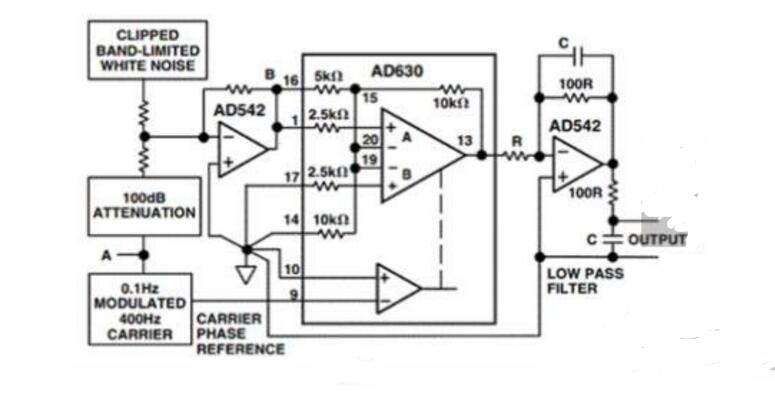

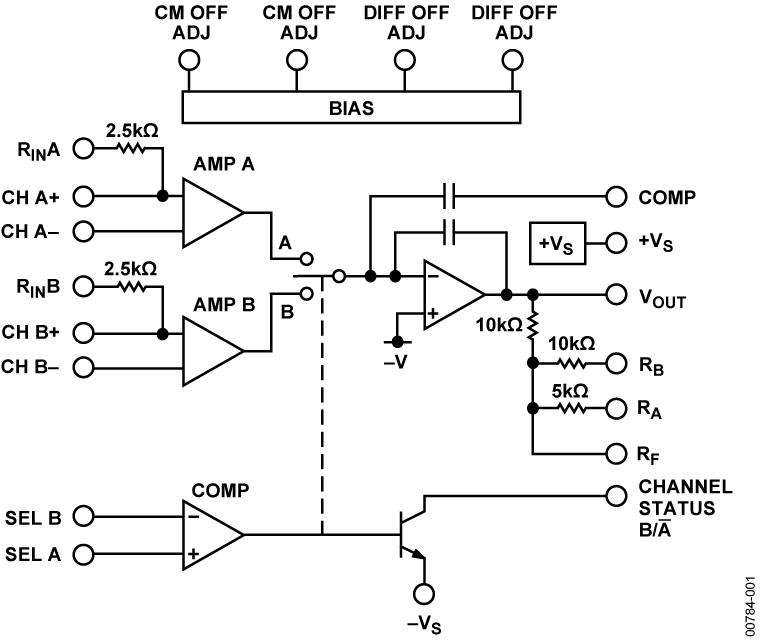

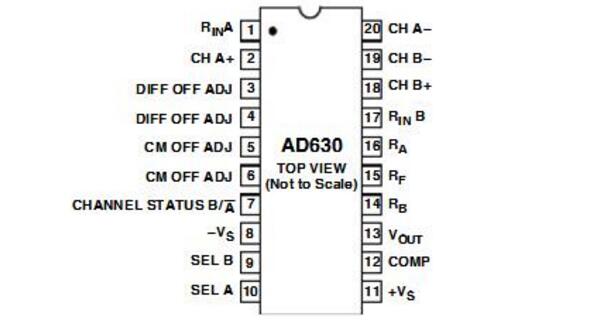

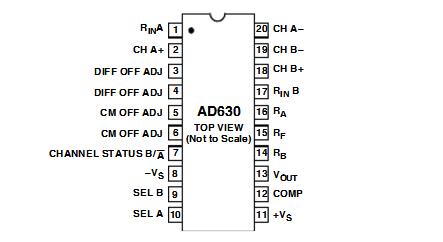

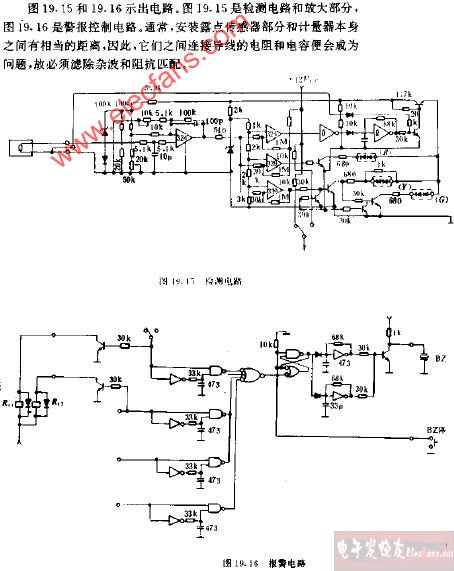

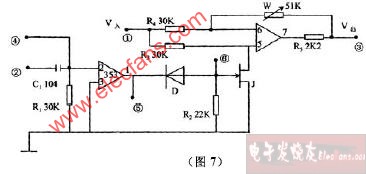

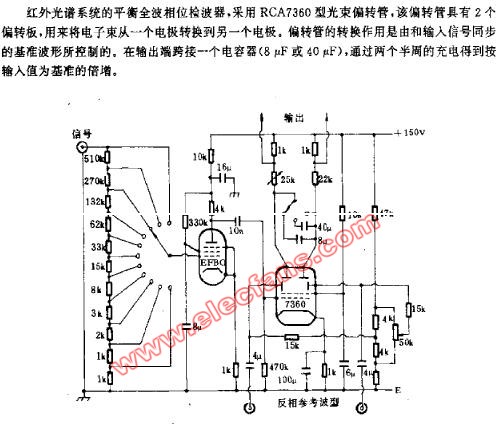

AD630的锁相放大电路示意图如下图所示。

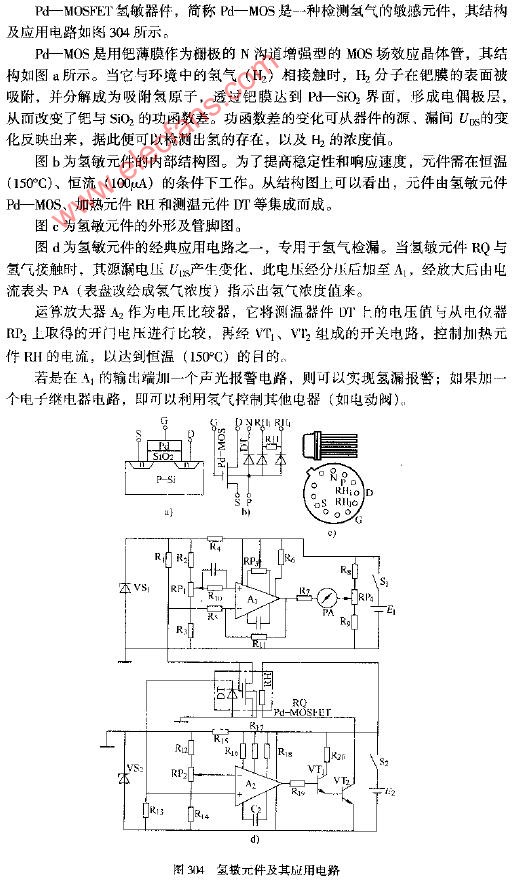

A点的波形为被检测信号与载波调制后的双边已调制波形,B点为双边已调制波形和噪声叠加后的波形,AD630的第9脚接载波信号,方波、正弦波都可行,相当与一个参考相位。AD630的输出接一个积分电路及一个低通滤波器,以达到的信号的完美恢复。

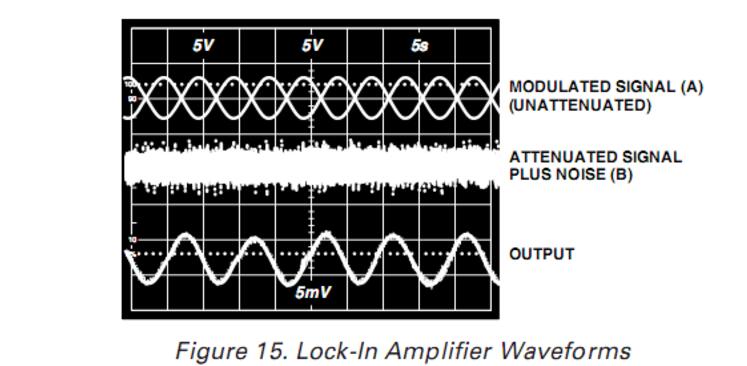

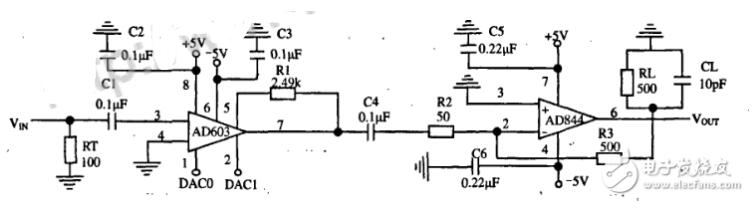

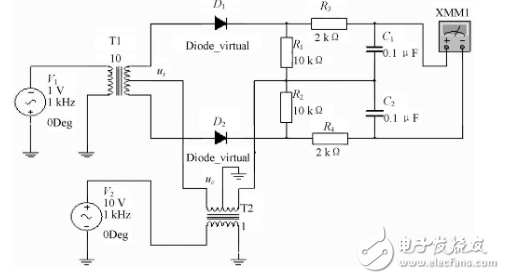

测试信号400Hz的载波调制0.1Hz的正弦波产生,正弦调制波形用于清楚的说明,信号通过类似于图9b的电路产生,显示在如图15上部的轨迹。他被衰减10万次,规范化求和放大器的输出B。噪音信号通过求和放大器加入到调制信号中,这个信号是简单的带限裁剪的白噪声。图15的中间轨迹显示了衰减的信号和噪音的叠加。混合信号使用相位信息同步解调(相位信息来自于调制器),结果为使用2极点的简单滤波器进行低通滤波,滤波器对输出端提供100增益,恢复后的信号在图15的下部。

上述这个混合的信号和干扰噪音类似于要求进行检测的锁定放大的信号。AD630精确的输入性能提供了大于100dB的信号范围,并且其动态响应允许其用于载波频率比实例中的大于两个或以上的数量级。一个更复杂的低通输出滤波器,将有助于抵抗更宽的带宽干扰。

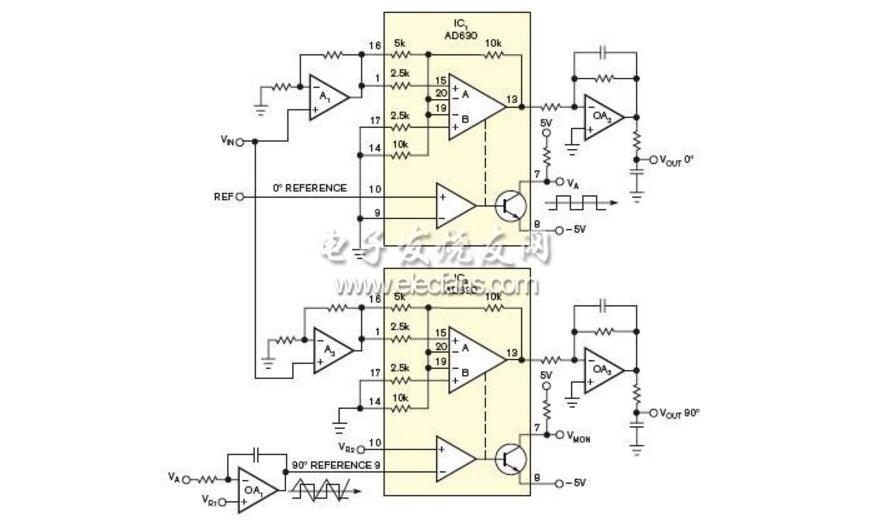

ad630应用电路:相敏检波电路

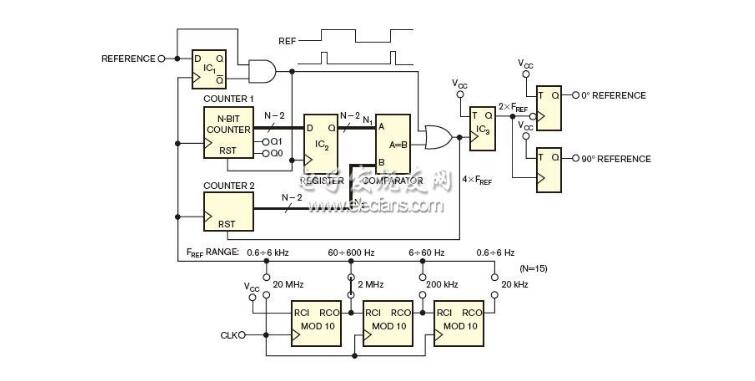

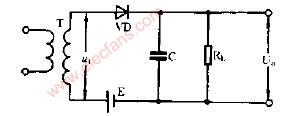

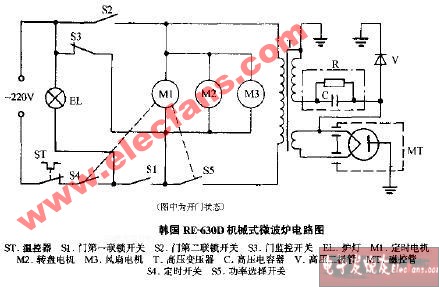

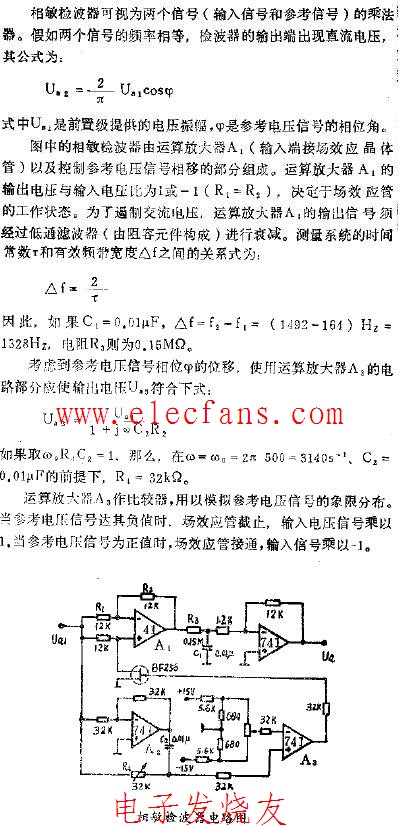

图2描绘了一条全数字电路,你可在小型CPLD中实施该电路,来产生图1中的0和90?基准信号。1号计数器以数字时钟脉冲的数量N的形式来测量基准信号时间,其中的基准时间可能不同于50%。在基准信号的每个正前沿,该计数器在N1=1处收到一条预设命令。D型双稳态多谐振荡器IC1产生这类脉冲。

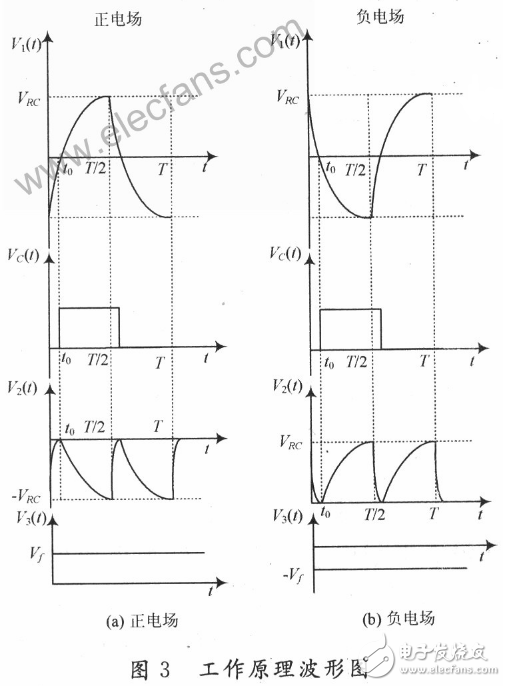

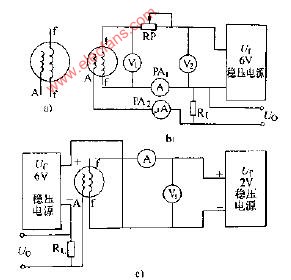

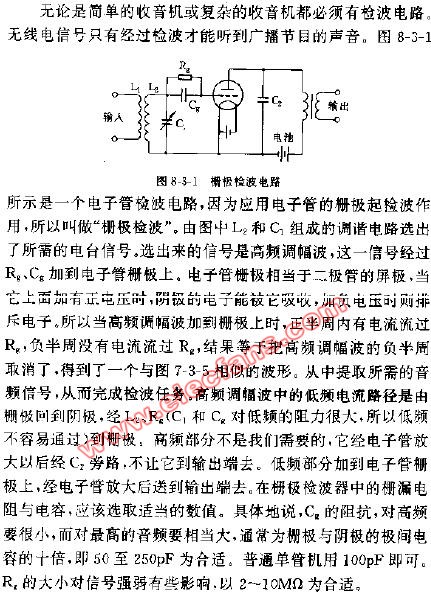

图1,OA1把双极VA信号积分,并创建三角波。VR1和VR2获得关于VA的90。相移基准电压。

图2,你可在小型CPLD中实现这条全数字电路。

当基准时间超过N/4整数值的大约四倍时,就会缺少最后的EQ信号。为了克服这个问题,RST脉冲和EQ脉冲的“或”组合会在每个基准时间周期内产生四条几乎等距的命令。N/4整数除法是逻辑右移N1的两位,在最后的脉冲位置上产生最大误差3。T型双稳态多谐振荡器IC3产生一个信号,频率为基准信号的两倍。这样,准确度等于3/N1。

为使准确度至少能与AD630相比,1号计数器的N1输出将为最高值。但是,如果你希望N1达到较高值,那么对于给定的数字时钟频率,位数的增加会使最大基准频率下降。

电子发烧友App

电子发烧友App

评论