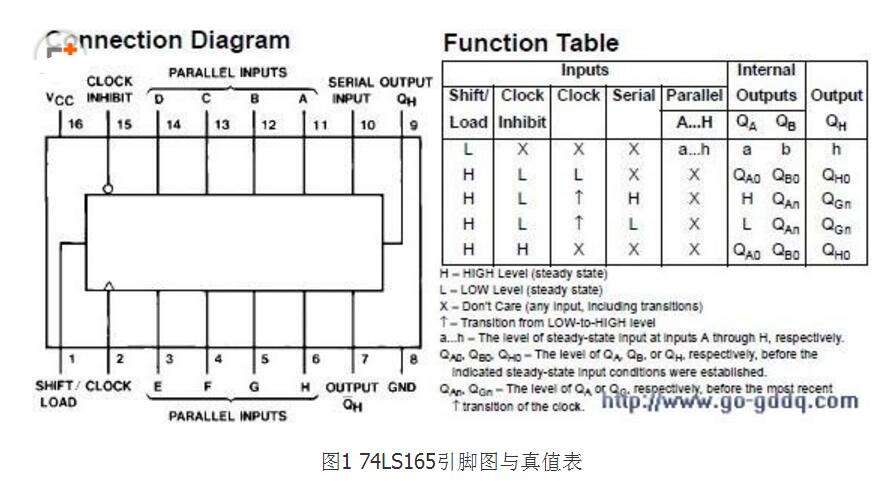

74LS165功能简介

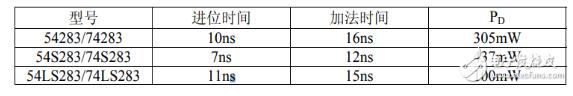

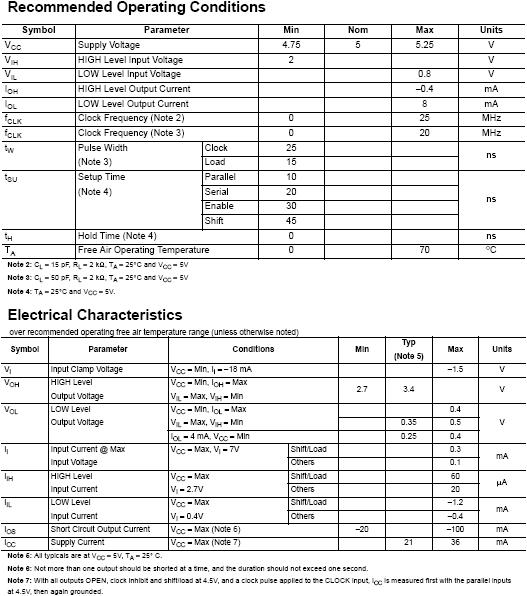

主要电特性如下:

工作原理:

当移位\植入控制端(SH/LD)为低电平时,并行数据(A-H)被置入寄存器,而时钟(CLK,CLKINH)及串行数据(SER)均无关。当SH/LD)为高电平时,并行置数功能被禁止。CLK和CLKINK在功能上是等价的,可以交换使用。当CLK和CLKINK有一个为低电平并且SH/LD为高电平时,另一个时钟可以输入。当CLR和CLKINK有一个为高电平时,另一个时钟被禁止。只有在CLK为高电平时CLKINK才可变为高电平。

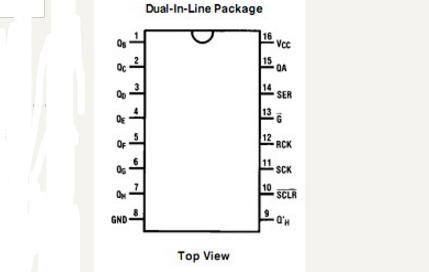

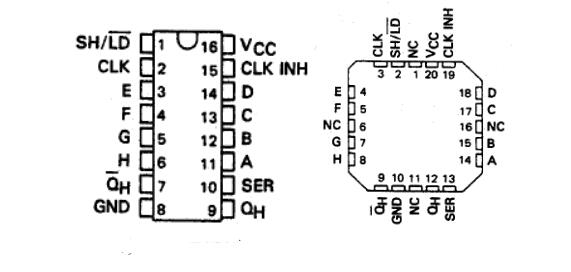

引出端符号

CLK; CLK INK 时钟输入端(上升沿有效)

A-H 并行数据输入端

SER 串行数据输入端

QH 输出端

QH“ 互补输出端

Sh/LD”移位控制/置入控制(低电平有效)

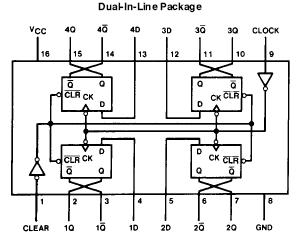

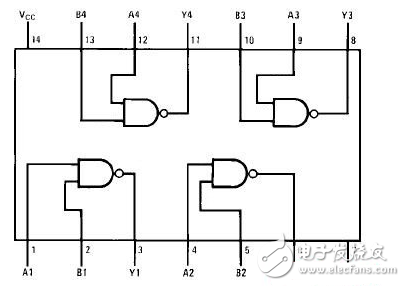

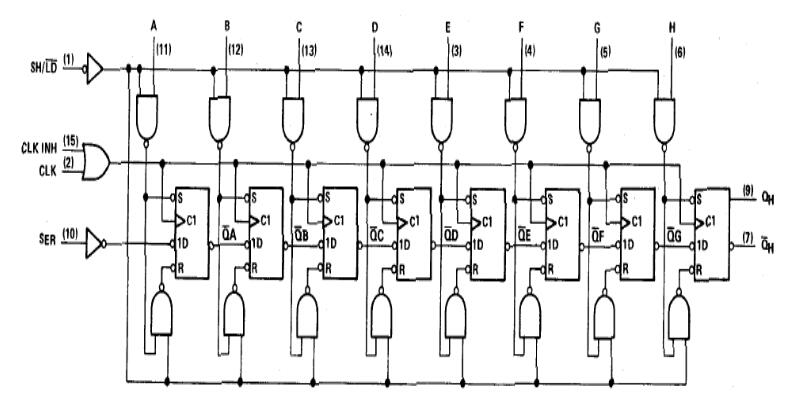

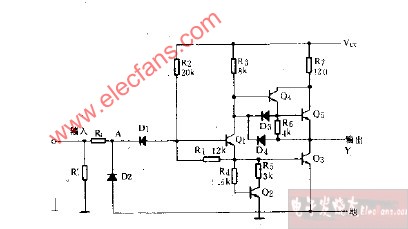

逻辑图

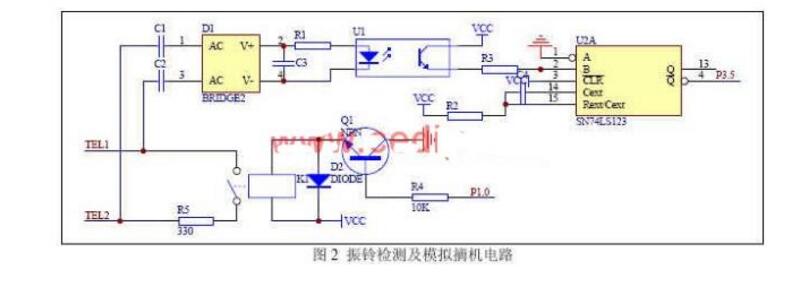

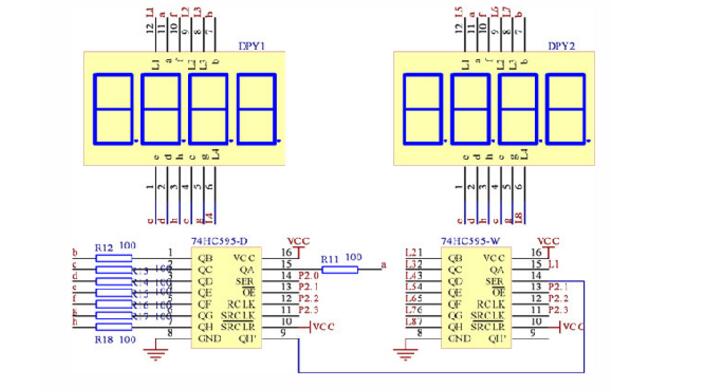

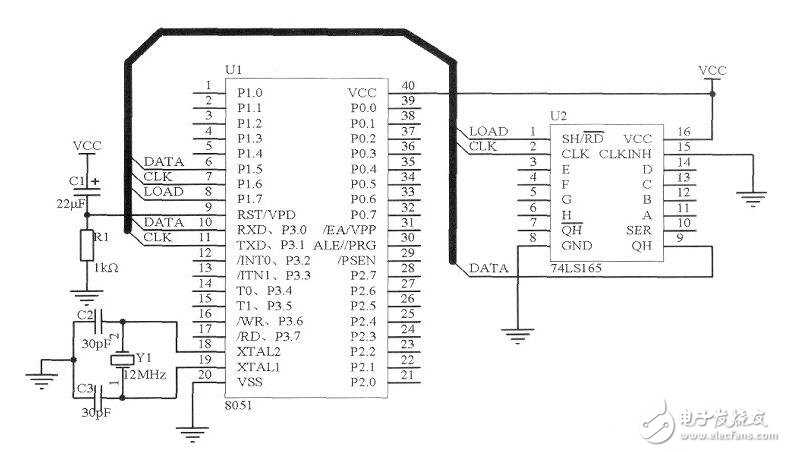

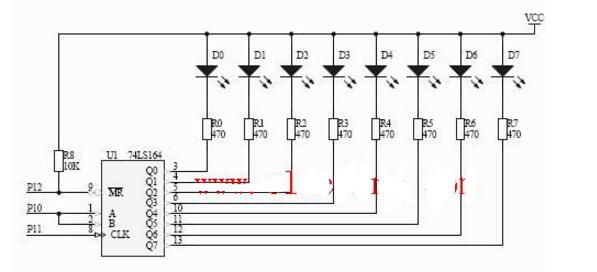

单片机I/O端口驱动74LS165电路

用I/O模拟移位寄存器的时序驱动74LS165,实现并行数据的输入。如下图所示,P1.5被用于串行数据输入,P1.6用于移位时钟输出,P1.7用来控制74LS165的工作状态。

单片机I/O端口驱动74LS165主要包括函数声明管脚定义部分、数据输入函数以及数据输出函数。

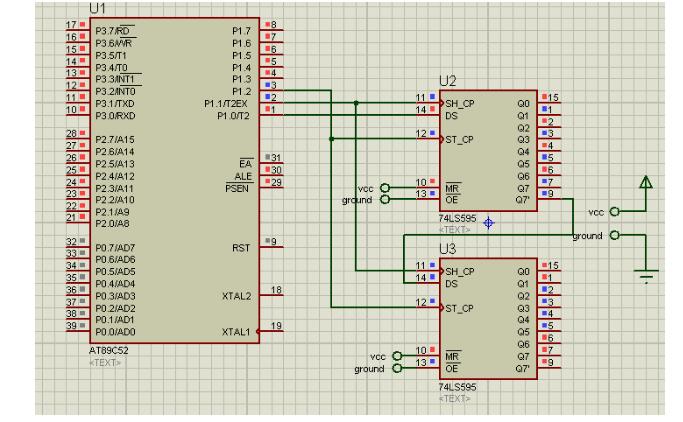

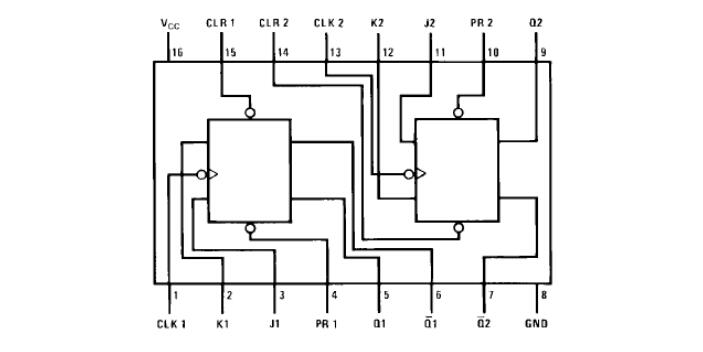

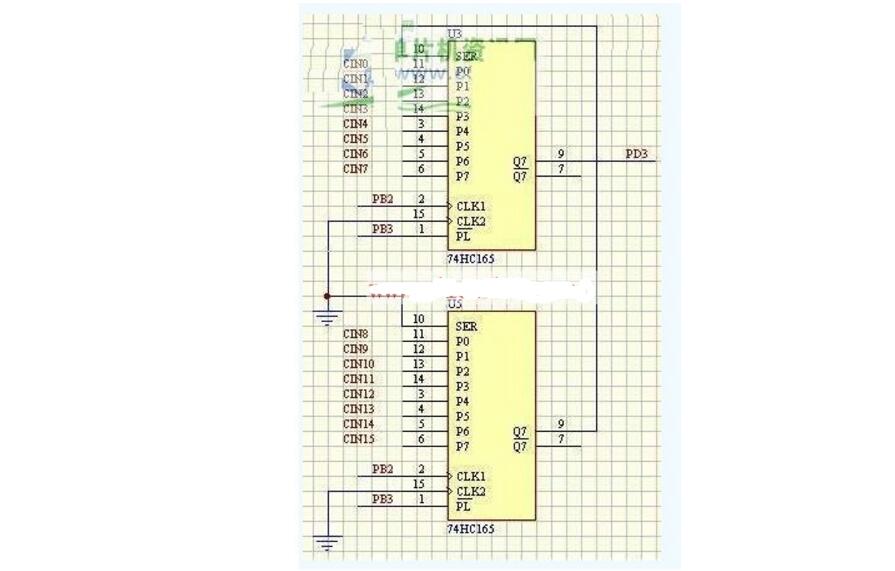

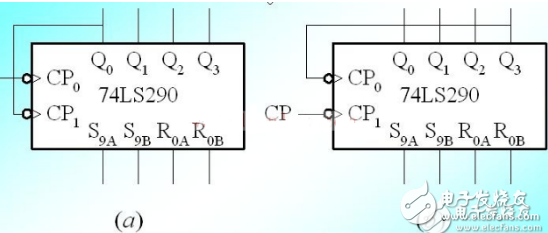

74ls165级联测试程序与proteus仿真电路图

关于如何做74ls165级联测试程序与proteus仿真电路图,内容请看下文:

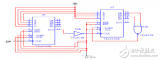

下面是proteus仿真原理图:

电子发烧友App

电子发烧友App

评论