74ls163实现十进制计数器电路(一)

改变74LS163二进制计数器为十进制计数器

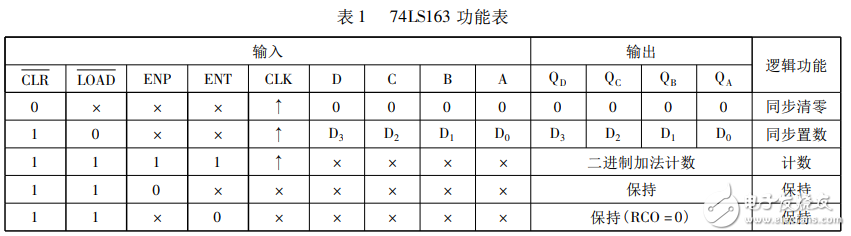

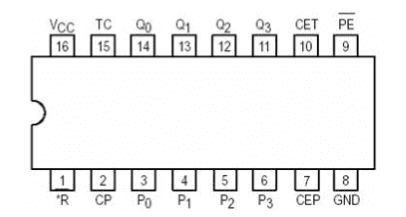

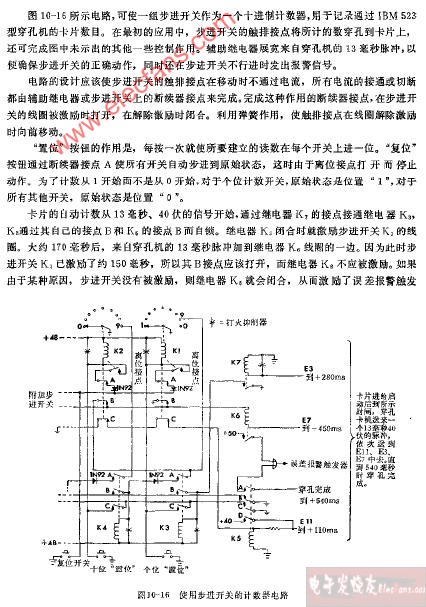

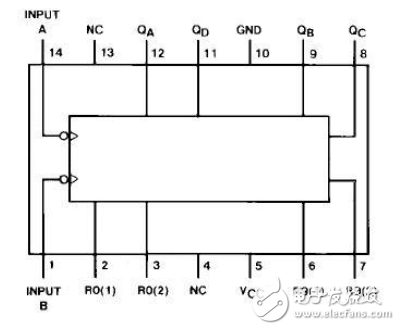

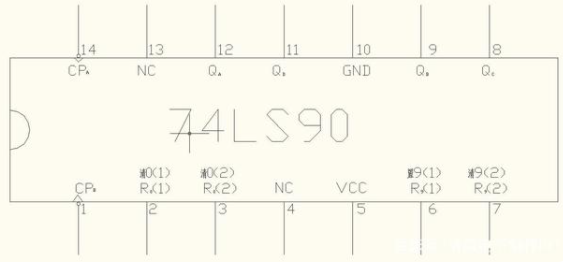

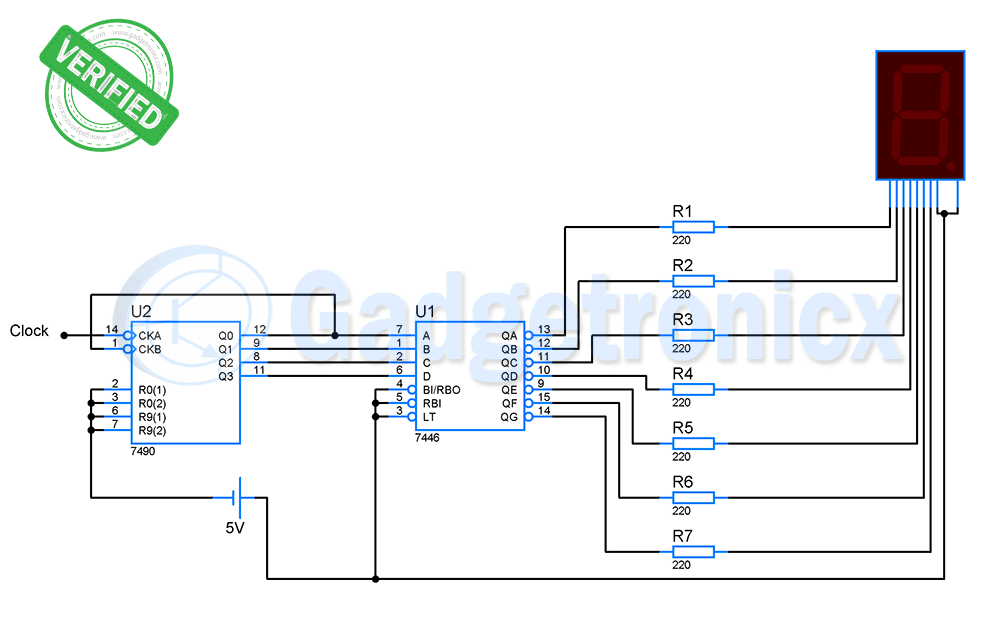

连接电路图如图22.2所示,即用一FDS4435BZ个与非门,其两个输人取自QA和QD,输出接清零端α‘R。当第9个脉冲结束时,钣和QD都为“1”,则与非门输出为低电平“O”,并加到αR端,因CIR为同步清零端,此时虽已建立清零信号,但并不执行清零,只有第1O个时钟脉冲到来后74LS163才被清零,这就是同步清零的意义所在。

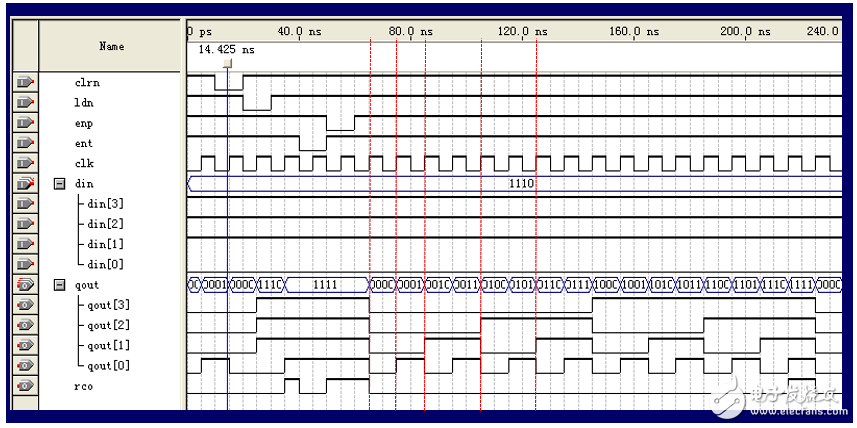

验证图是否如同一个模10计数器:

图 用74I’s163构成十进制计数器

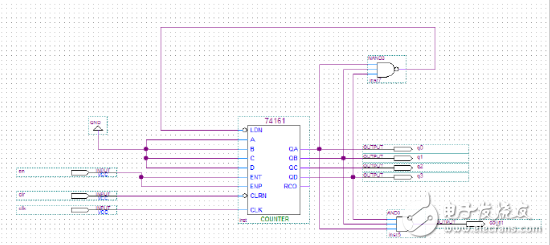

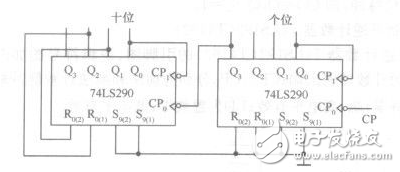

用两个74ls163连接成一个两位十进制计数器。连接电路图如图22.3所示。

当74LS163(1)记到9时(1001),产生清零信号并同时使74LS163(2)的控制端ENT为高电平,即使忽s163(2)开始计数,同样记到9时(1001)产生低电平清零信号使其清零,输出显示为0,并同时产生一进位信号(【D为高电平),可将此信号加到一发光二极管显示其进位输出。计数器的4位输出可连接到实验箱上的译码显示器的4个输人端,电路如图22.3所示(注意,计数器的QA~QD和译码器的输人端A~B一一对应连接)。

74ls163实现十进制计数器电路(二)

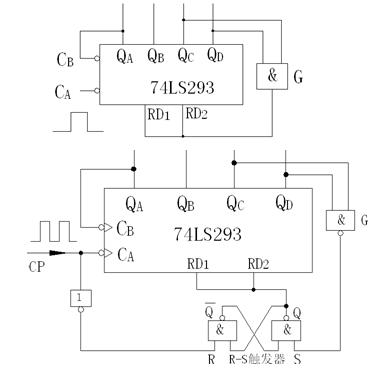

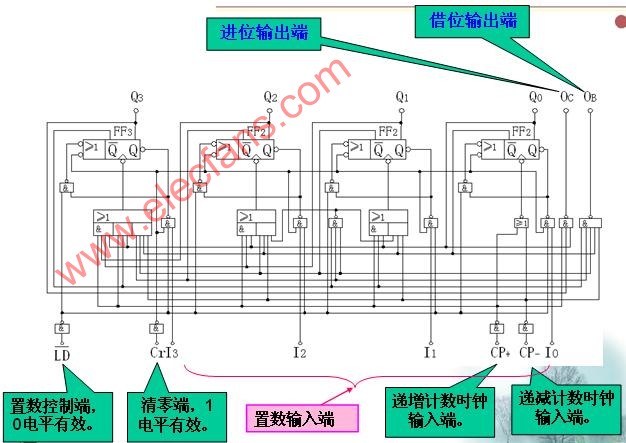

以74LS163为基础设计一个6分频电路

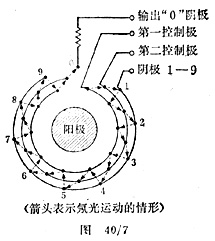

首先,需要明白什么叫分频,图3展示了分频的效果:

分频通常以CP(时钟脉冲)为基础,从图3中可以看出:qout[0]的周期为CP的2倍,qout[1]的周期为CP的4倍,qout[2]位8倍,qout[3]为16倍,显然,其频率分别为CP的1/2, 1/4, 1/8, 1/16,即所谓的2-分频,4-分频,8-分频,16-分频。

再进一步分析,对于qout[0],其变化为:当一个时钟脉冲来临时,qout[0]变化一次;对于qout[1],每两个时钟脉冲,qout[1]值变化一次;对于qout[2],每四个时钟脉冲,qout[2]值变化一次;对于qout[3],每8个时钟脉冲,qout[3]值变化一次。依次类推,如果要做6分频,显然应该是每3个时钟脉冲,值变化一次,如何用74LS163来做6-分频呢?

显然,这个问题变为:如何使74LS163中的某一位每3个时钟脉冲跳变一次。显然,只有QD和QC这两位的变化可能满足(QB每两个脉冲跳变一次,QA每个脉冲跳变一次),如果选择QC,显然可以找出一个序列:

0000 —》 0001 —》 0010 —》 1101 —》 1110 —》1111 —》0000 —》 …

对于QC,先是3个0,然后是3个1,开始循环,正好是6分频。仔细观察,发现这个循环对于QD也是6分频。

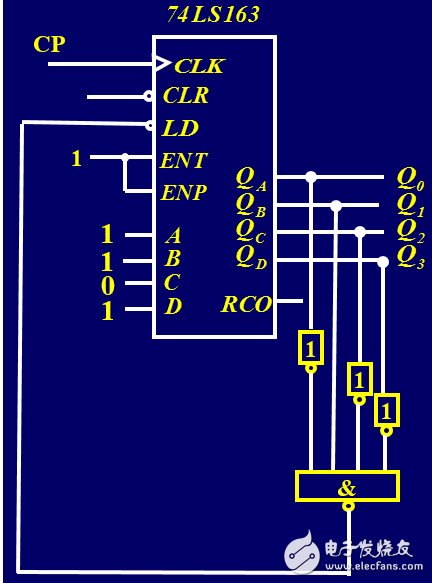

针对上面分析得到的状态迁移序列,如何用74LS163来实现呢?对于前半部0000 —》 0001 —》 0010,执行的是正常的计数功能,对于后半部1101 —》 1110 —》1111( —》0000),执行的也是正常的计数功能,只有0010 —》 1101是一个跳跃,即当计数器状态为0010时,下一个状态需要用到163计数器的并行置数功能,因此,需要对163的计数器的输出进行判断,当输出为0010时,用1101对电路进行置数(确保下一时刻电路状态为1101)。

在此分析的基础上,其电路图如图4所示:

电子发烧友App

电子发烧友App

评论