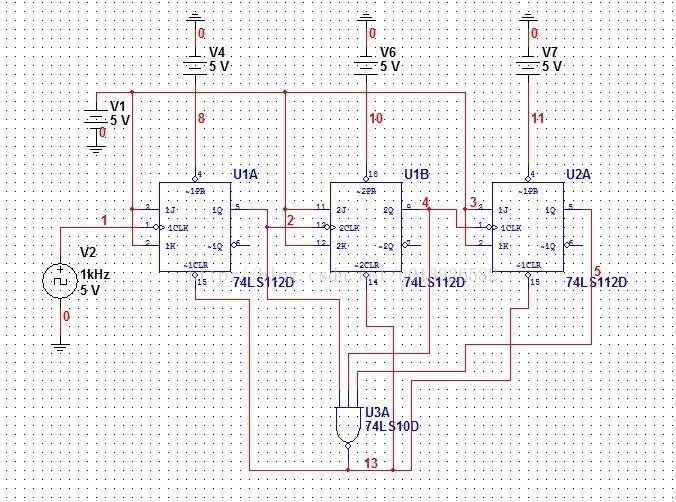

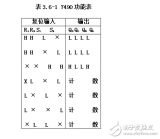

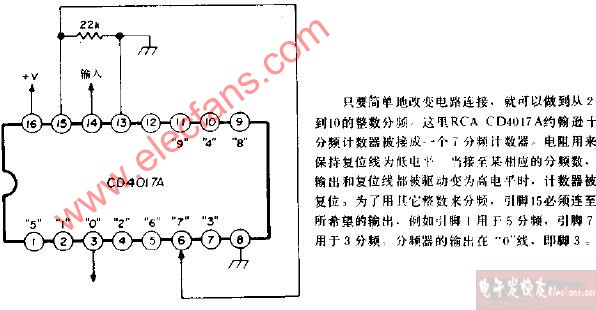

74ls90应用电路图四:

基于74LS90数字电子钟逻辑电路的设计

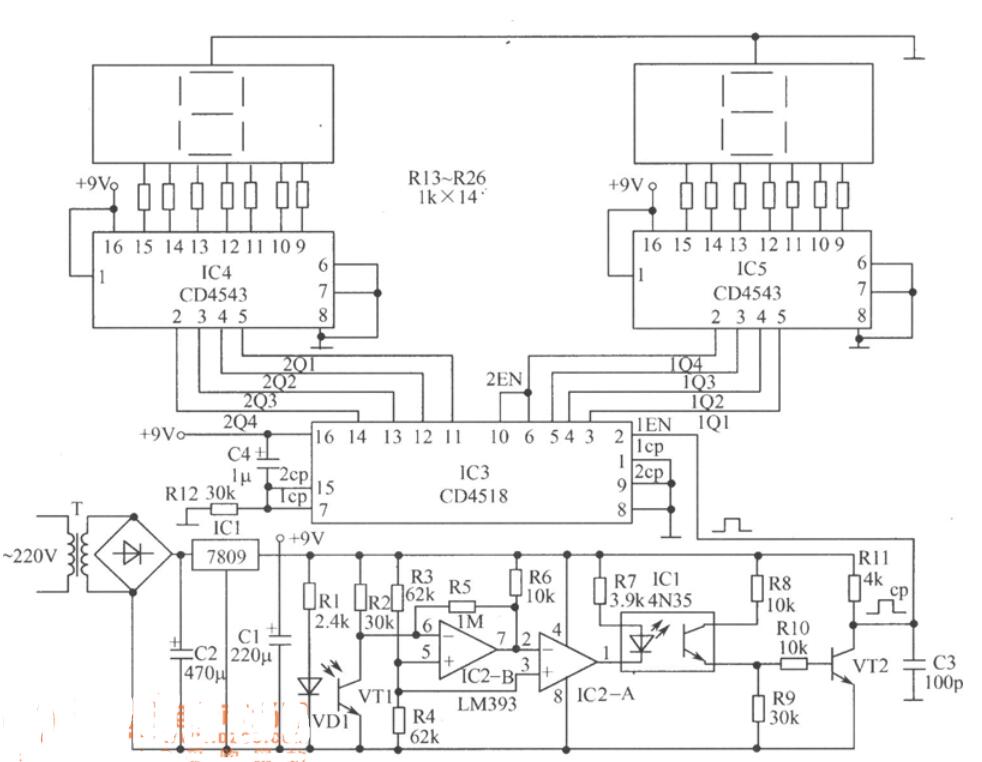

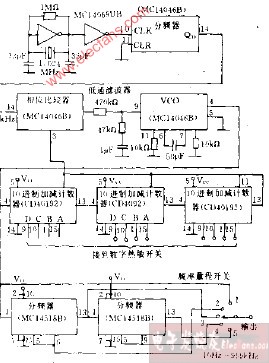

数字钟是采用数字电路实现对“时”、“分”“秒”数字显示的计时装置。数字钟的精度稳定度远远超过老式机械钟。此次设计采用LED数码管显示时、分秒,以24.小时计时方式,用100KHz的品振产生振荡脉冲,采用741LS90集成电路设计分频器和定时计数器。

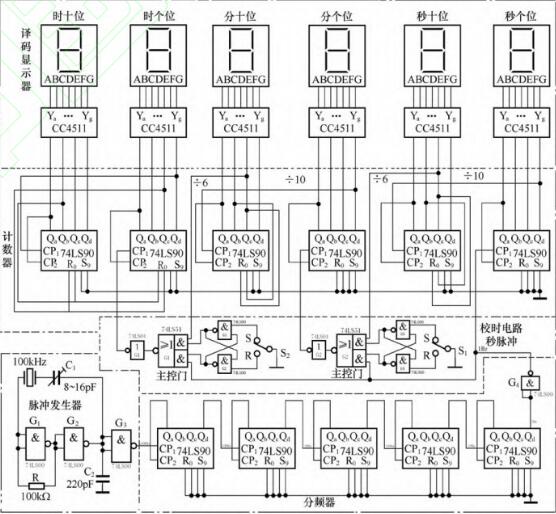

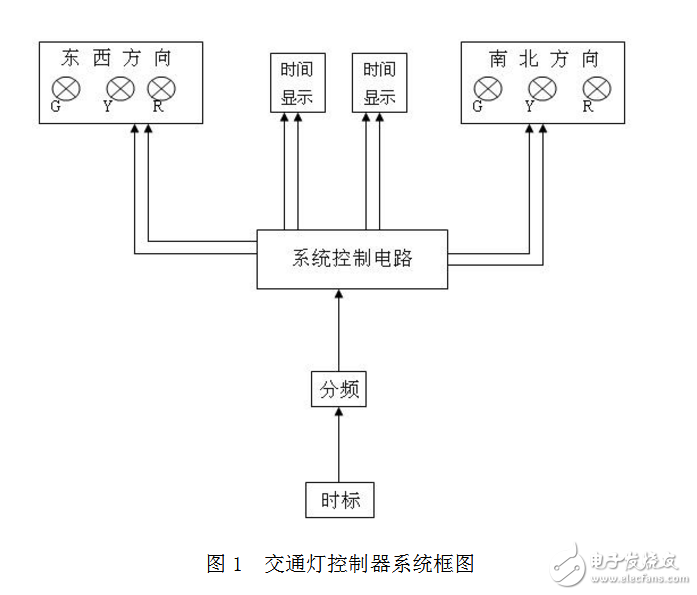

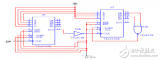

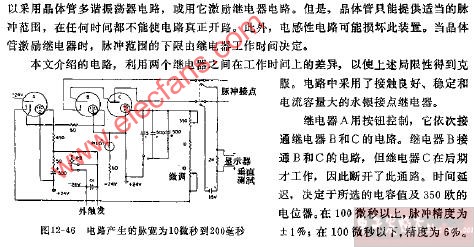

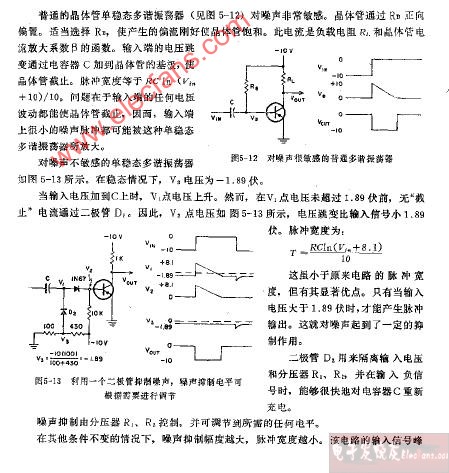

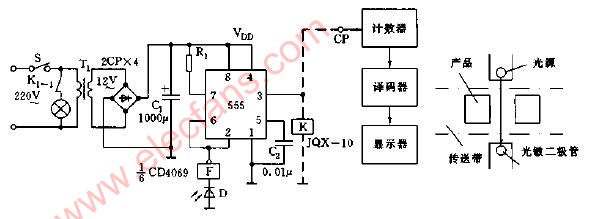

1、数字电子钟各部分逻辑电路功能(见图1)

2、数字电子钟各部分逻辑电路工作原理(见图1)

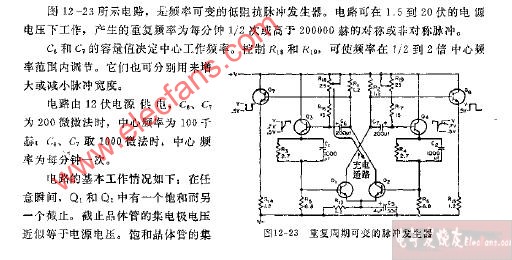

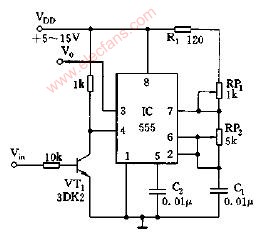

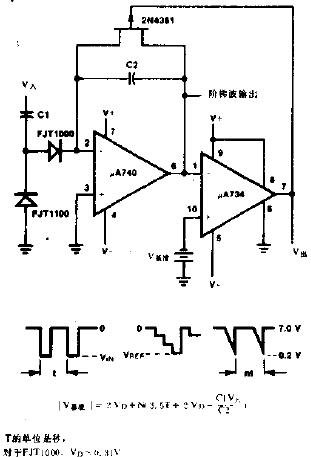

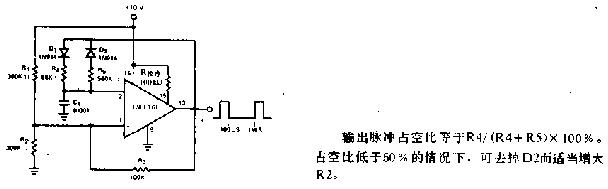

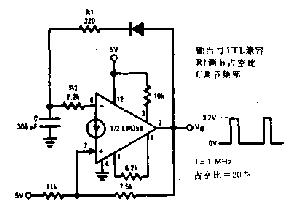

2.1、脉冲信号发生器

石英晶体振荡器的振荡频率最稳定,其产生的信号频率为100KHz,通过整形缓冲级G3输出矩形波信号。

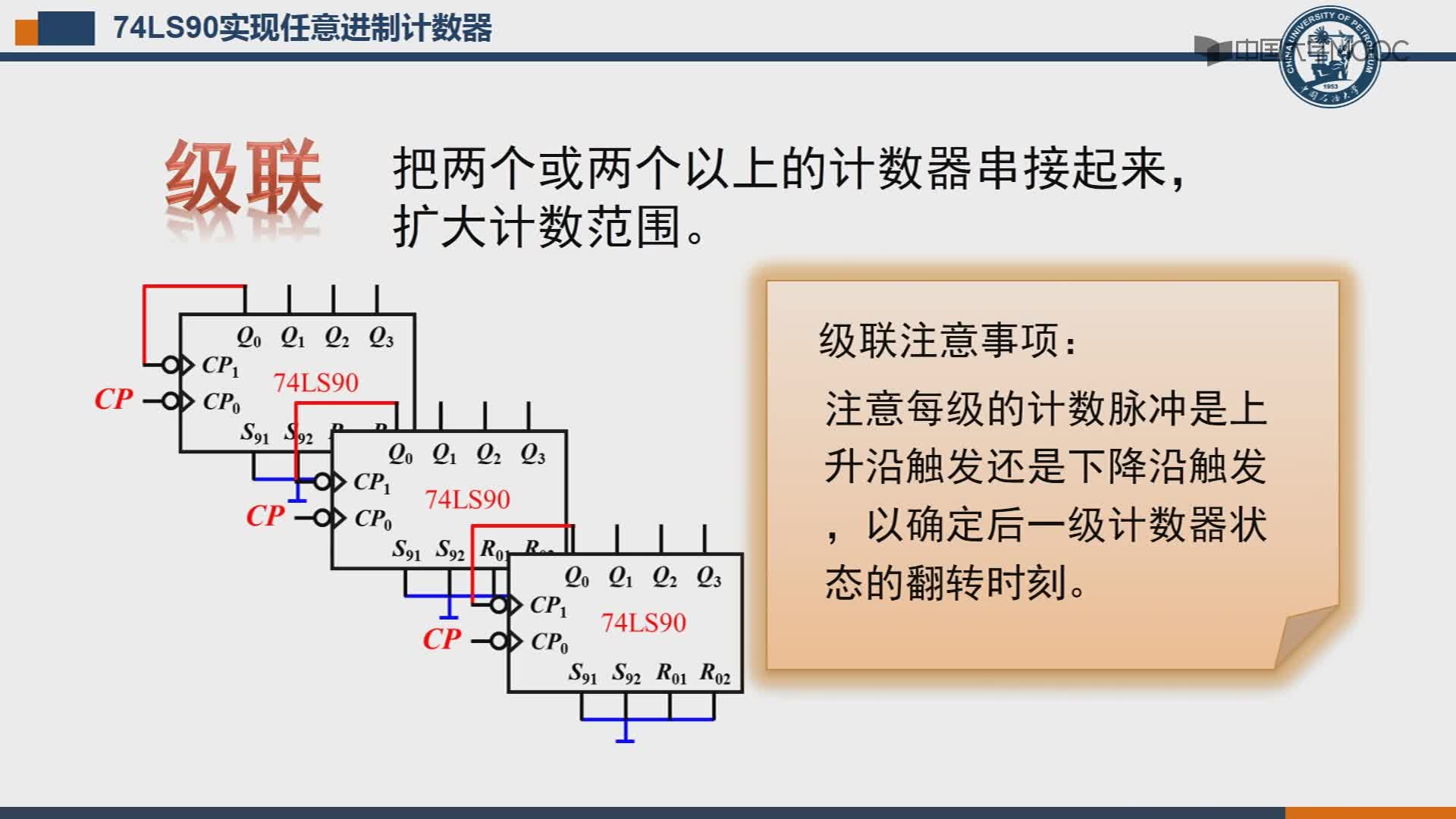

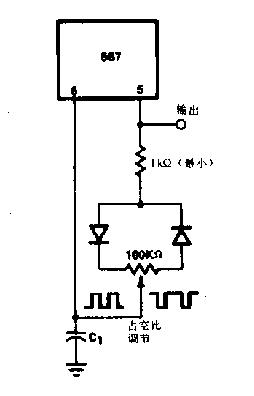

2.2、分频器

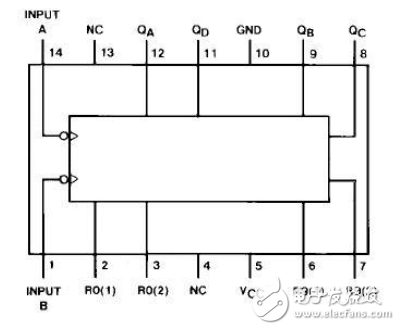

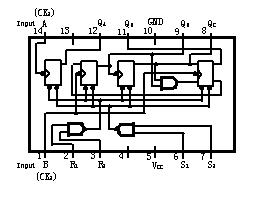

石英晶体振荡器产生的信号频率为100KHz,要得到1Hz的秒脉冲信号,则需要分频。图中采用5个中规模计数器74LS90,将其串接起来组成105分频器。每块74LS90的输出脉冲信号为输入信号的十分频,则100KHz的输入脉冲信号通

过五级分频正好获得秒脉冲信号,秒信号送到计数器的时钟脉冲CP端进行计数。首先,将74LS90连成十进制计数器(共需5块),再把第一级的CP1接脉冲发生器的输出端。第-级的Qd端接第二级的CP1,第二级的Qd端接第三级的C.。。。。第五级的输出Qd就是秒脉冲信号。

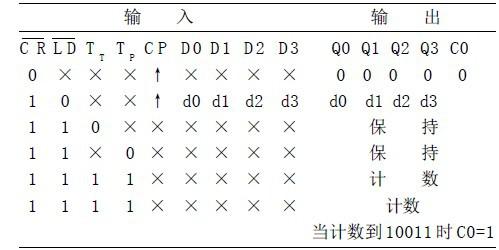

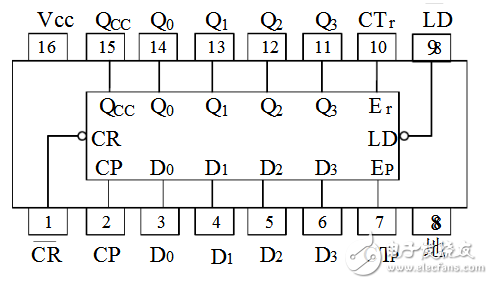

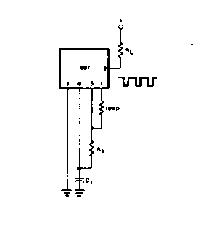

2.3、计数器

秒计数器采用两块74LS90接成六十进制计数器,分计数器也是采用两块74LS90接成六十进制计数器。时计数器则采用两块74LS90接成二十四进制计数器,秒脉冲信号经秒计数器累计,达到“60”时秒计数器复位归零并向分计数器送出一个分脉冲信号,分脉冲信号再经分计数器累计,达到“60”时分计数器复位归零并向时计数器送出一个时脉冲信号,时脉冲信号再经时计数器累计,达到“24”时复位归零。

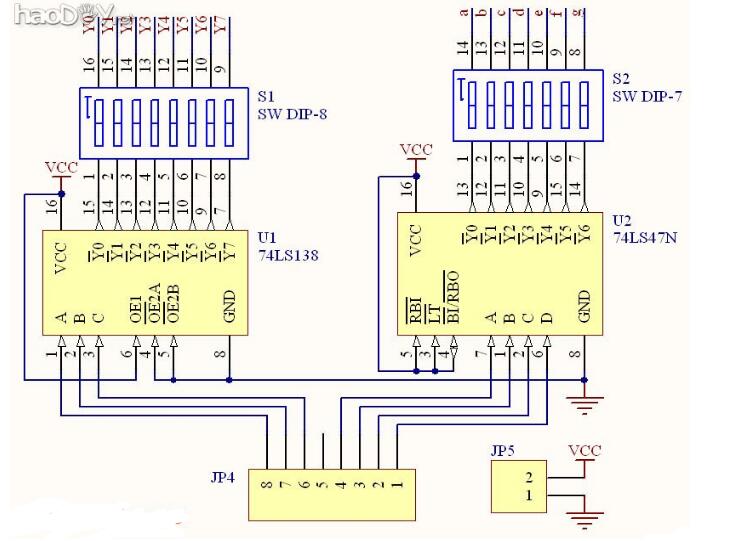

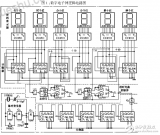

2.4、译码显示电路

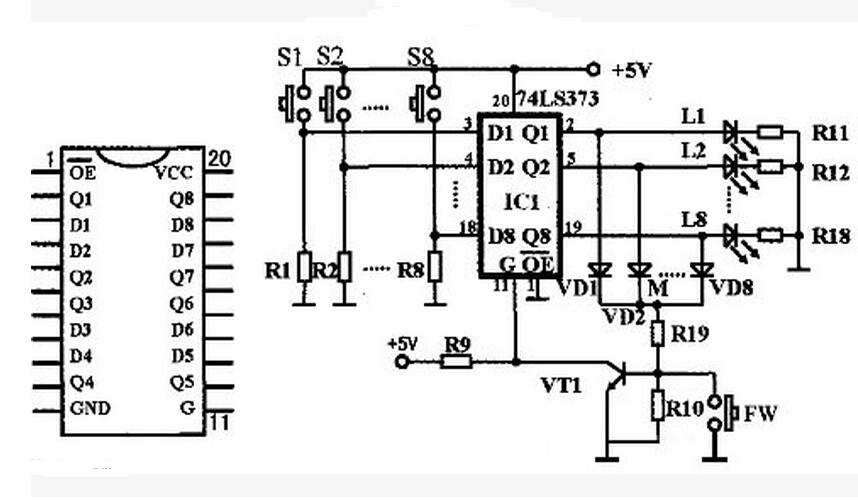

时、分、秒计数器的个位与十位分别通过每位对应一块七段显示译码器CC4511和半导体数码管,随时显示出时,分、秒的数值。

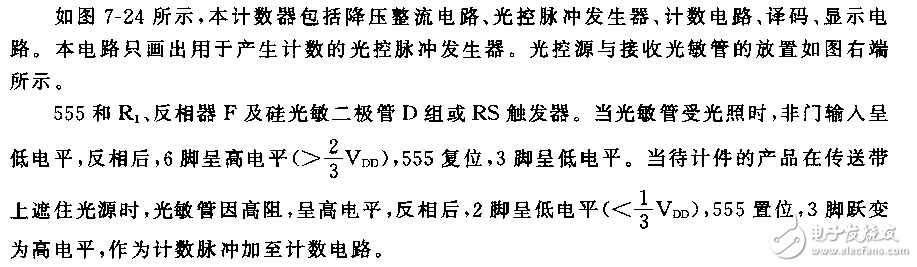

2.5、校时电路

在图中设有两个快速校时电路,它是由基本RS触发器和与或非广]组成的控制电路,电子钟正常T.作时,开关SI、S2合到S端,将基本RS触发器置“1”,分、时脉冲信号可以通过控制门电路。当开关SI、S2合到R端时,将基本RS触发器置“0”,封锁了控制门电路,使正常的计时信号不能通过控制电路,而秒脉冲信号则可以通过控制门电路,使分。时计数器变成了秒计数器,实现了快速校准。

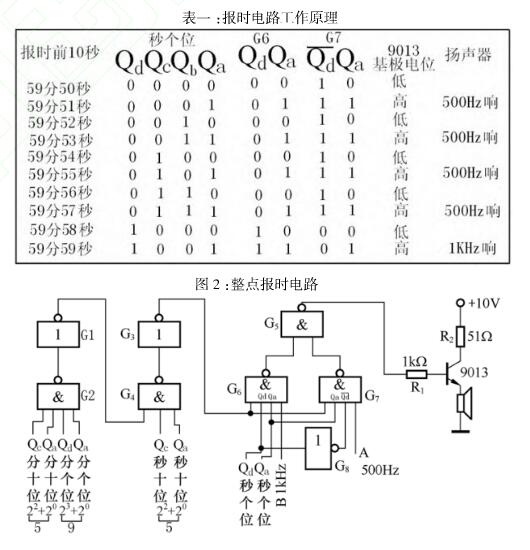

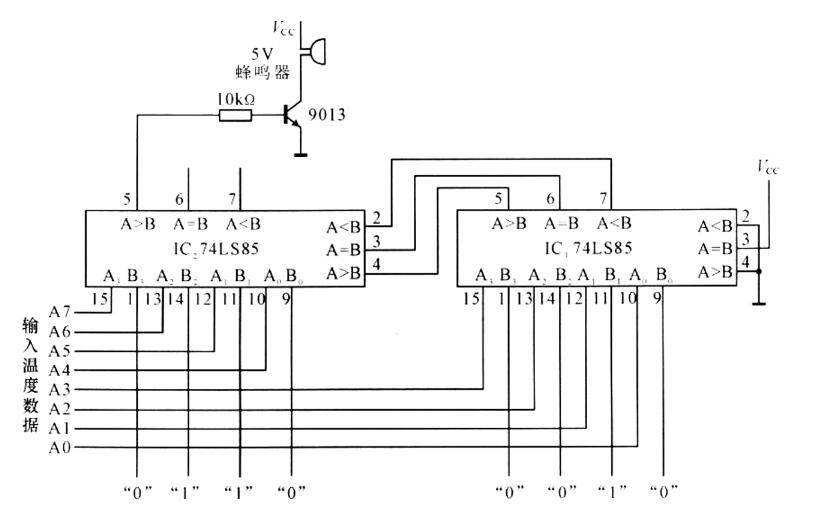

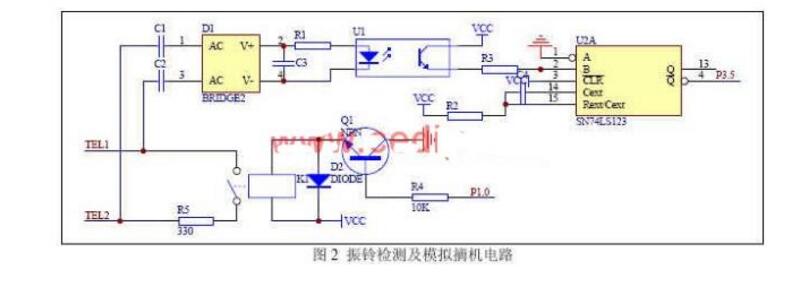

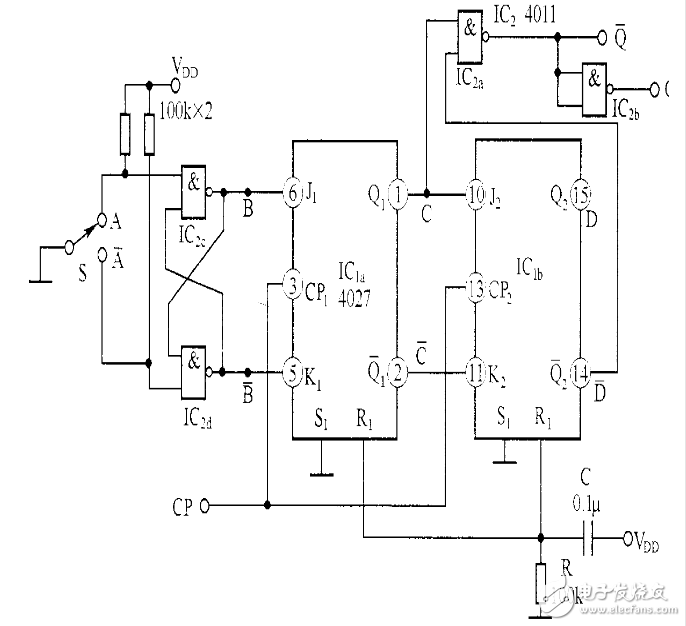

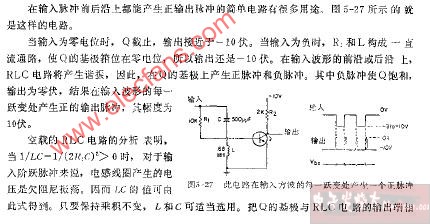

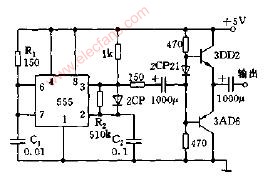

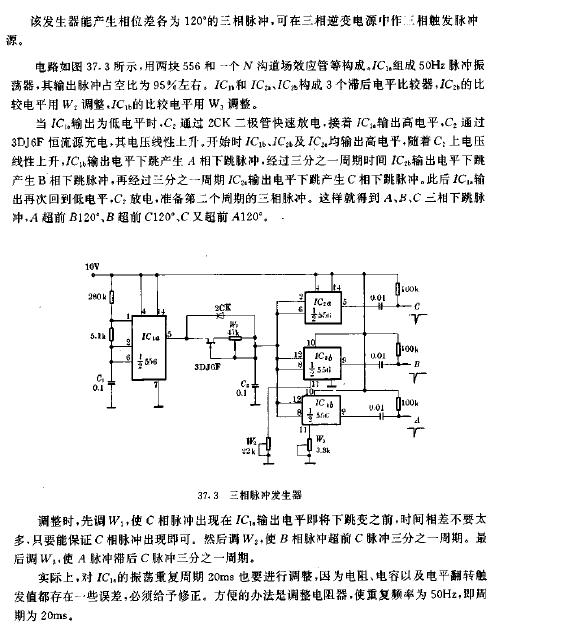

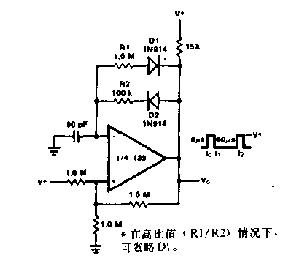

2.6、整点报时电路(见图2.表1)

每当分计数器和秒计数器计到59分50秒时,便白动驱动音响电路,在10 秒内自动发出5次鸣叫声,每隔1秒叫一次,每次叫声持续1秒,并且前4声的音调低,最后一响的音调高,此时计数器指示

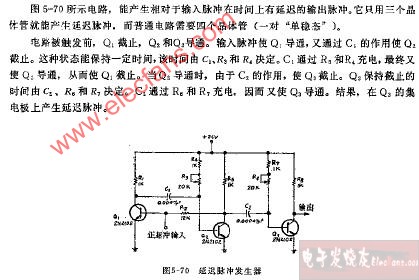

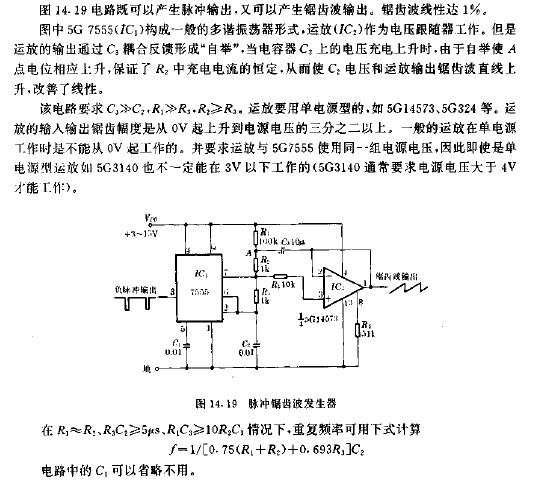

上式中,n表示输人信号总周期数。在实际T程中,倍压电路中的两个电容分别取C;=2.2uF, Cz=340uF。 充电电压情况如下表:

由电容充电曲线可知,到了电容充电后期,其曲线的上升斜率降低,充电速度减缓。通过式1-1的计算,达到充电额定值80%的时长为5秒。

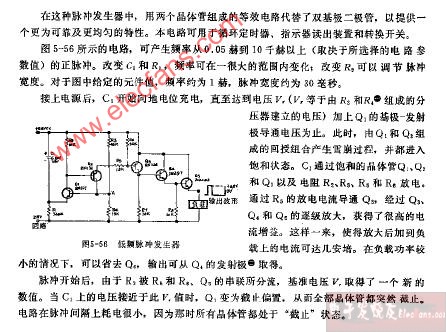

下表列举了在本公司的模拟器项目中,使用辅助模块前和使用后氙灯触发成功率的对比。改进后氙灯的触发率几乎达到100%。

综上所述,在增加成本不多的情况下,我们通过简单的电路改进、增加了辅助电压模块,解决了大功率内触发式长弧氚灯触发效率低的问题,模块的成本费用在人民币300元以内。

电子发烧友App

电子发烧友App

评论