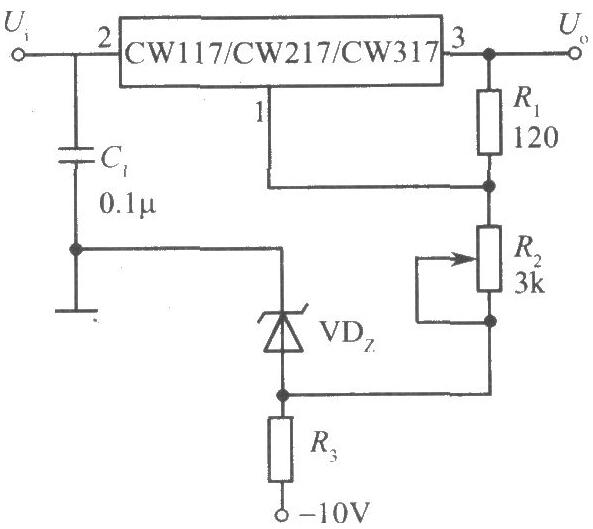

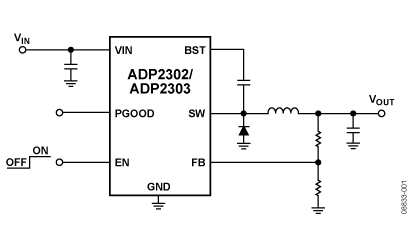

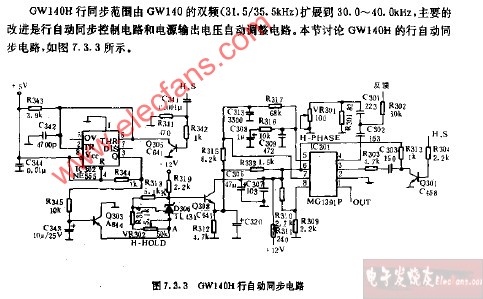

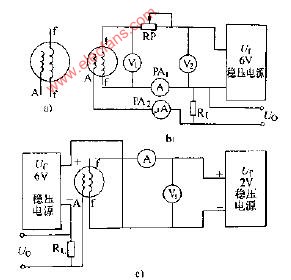

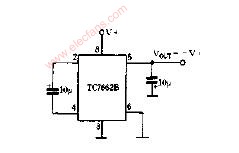

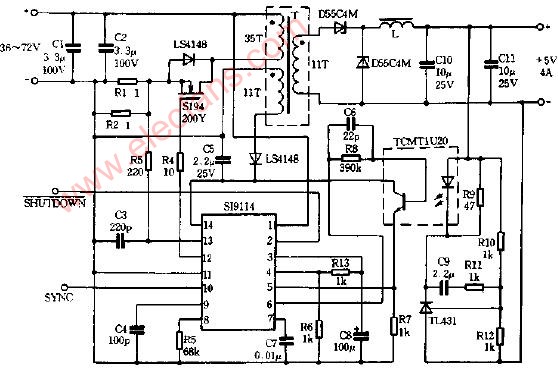

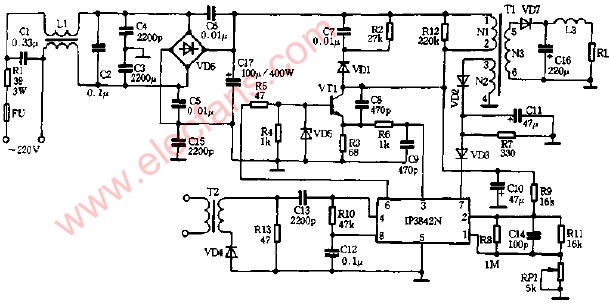

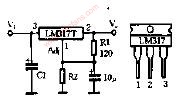

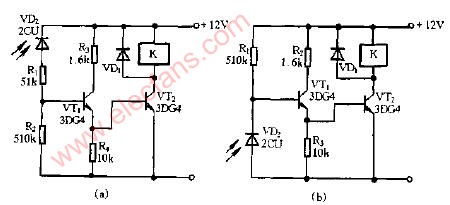

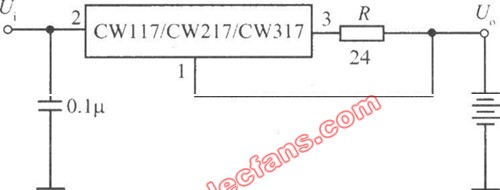

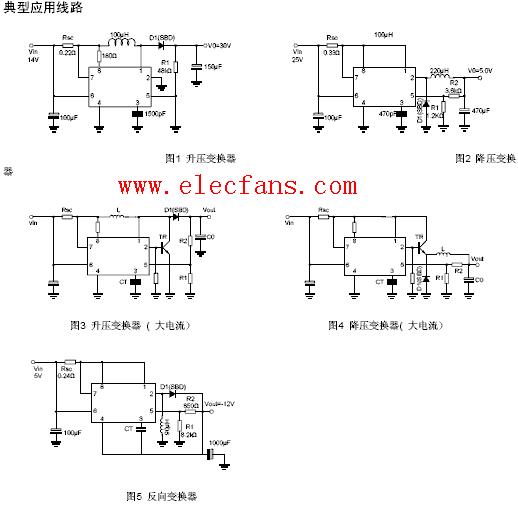

CW117典型应用电路图(一)

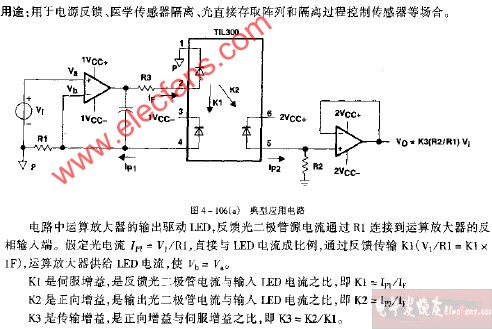

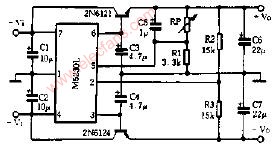

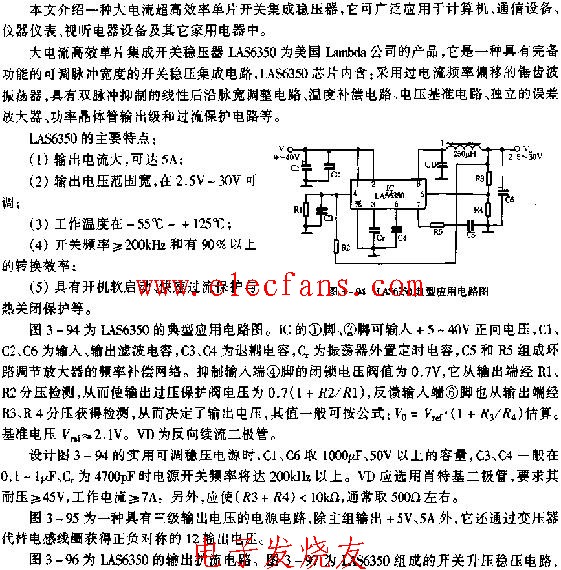

计算公式:Vo=1.25V(1+R2/R1)+IADJR2。

C1、C2≥ 1μ(独石电容)、R1=120~240O(金属膜)、R2<5K(金属膜)、C3≤22μ钽电容(必须考虑C3 的漏电阻。且Do 必须并存);50HZ 时滤波电容:CD≥ [1500~2000]μ×Io(A)。

输出端一般不要接大的滤波电解电容,否则Di 应与之并存。在I/O 端并接有较大感性元件时、必须在对应端增加保护二极管DF/DL。(正常时不必接Di、Dl、Df;一般应用不必接C3 和Do。

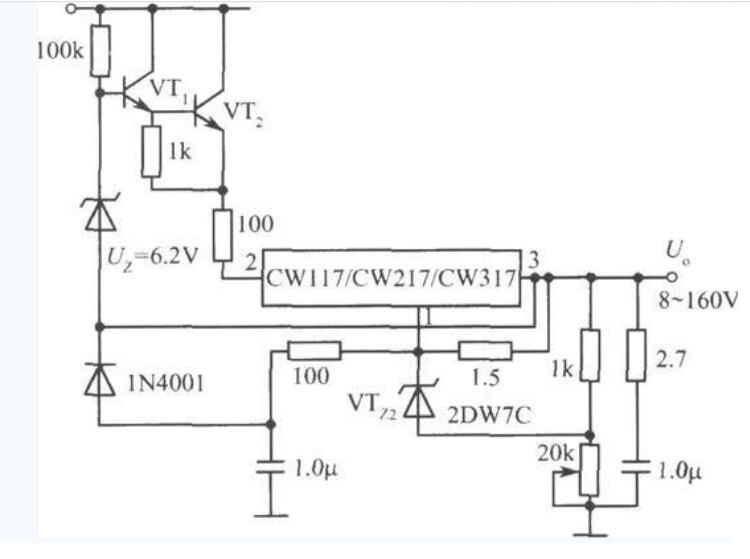

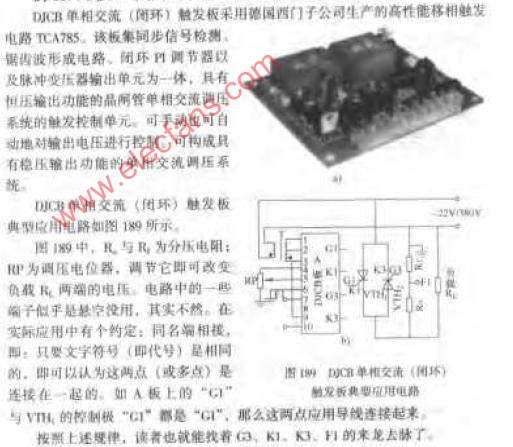

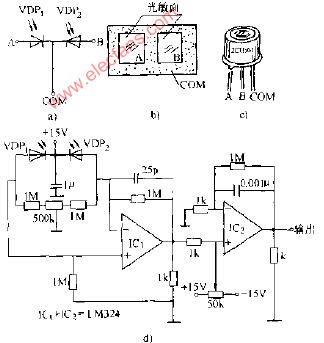

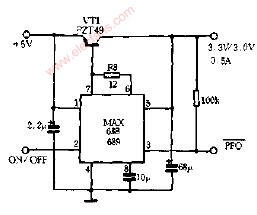

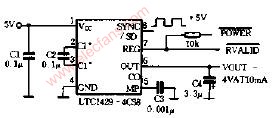

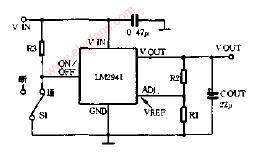

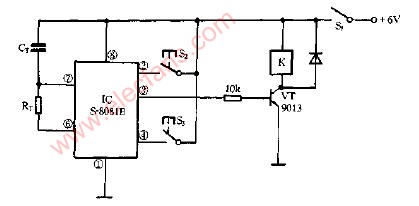

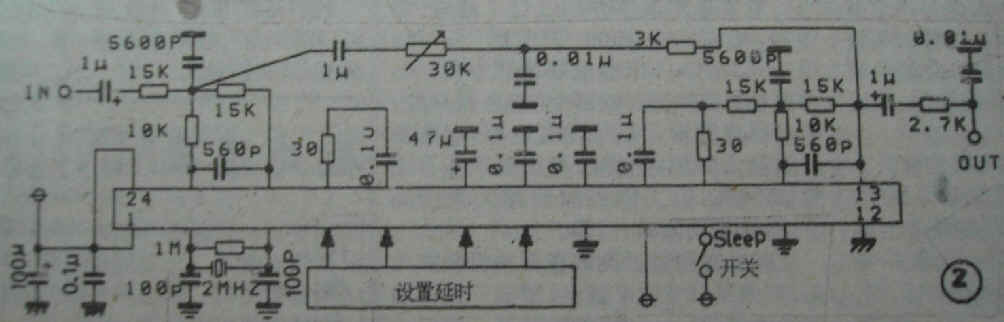

CW117典型应用电路图(二)

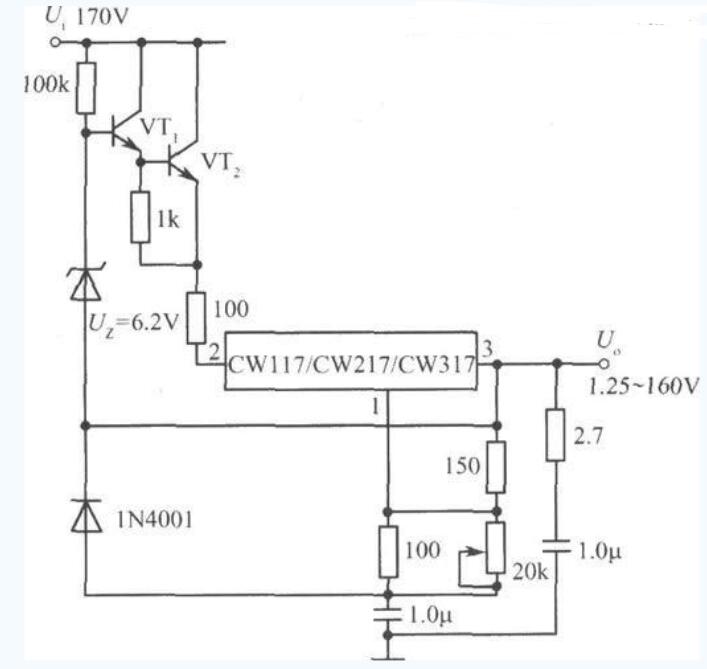

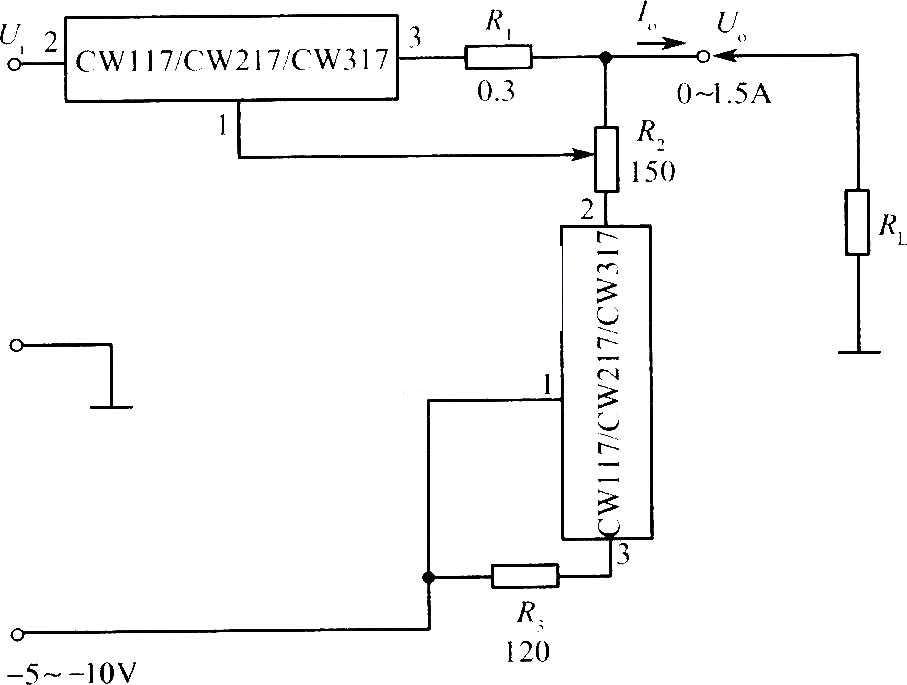

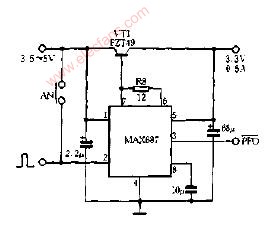

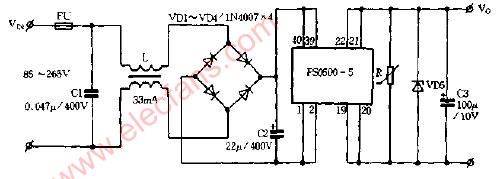

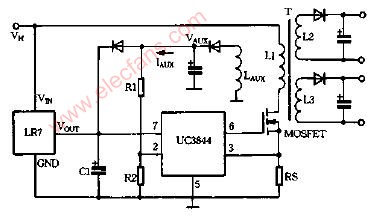

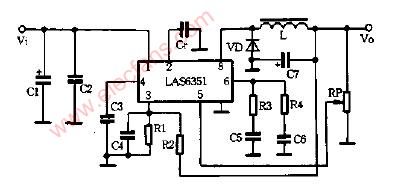

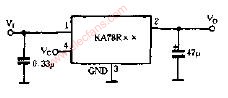

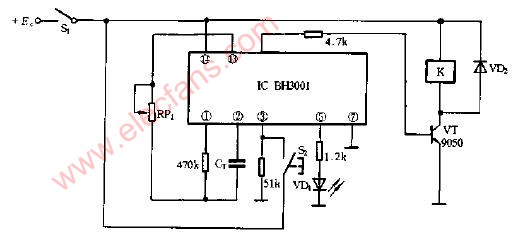

CW117典型应用电路图(三)

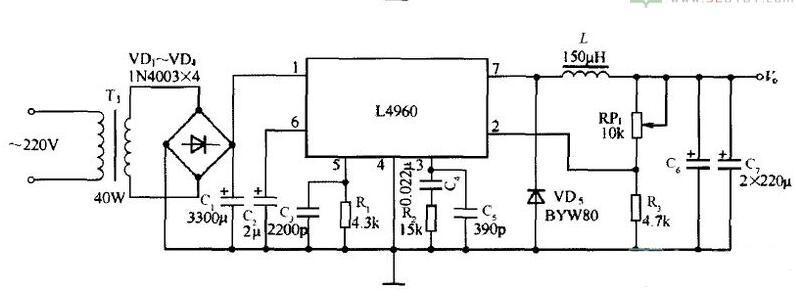

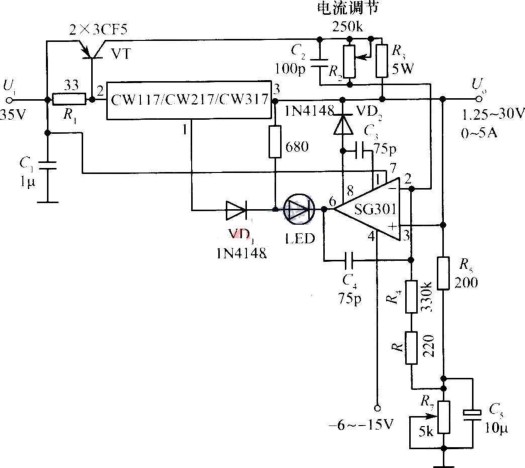

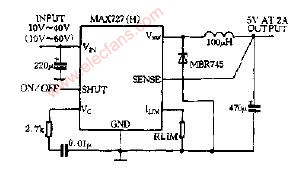

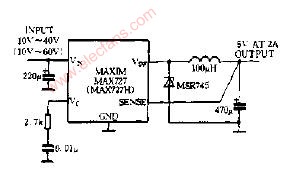

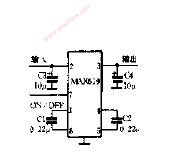

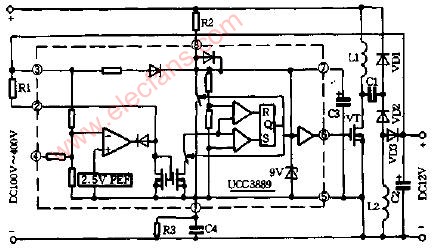

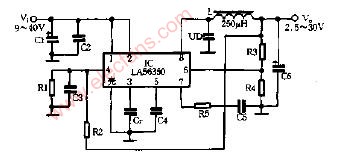

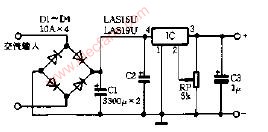

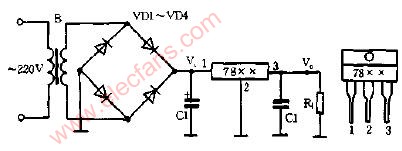

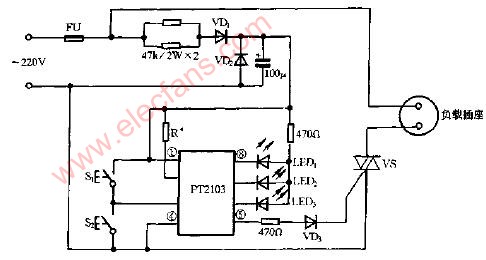

CW117典型应用电路图(四)

电子发烧友App

电子发烧友App

评论