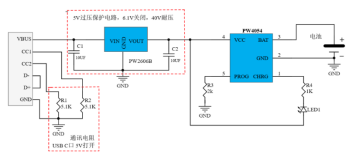

CSS-1---单节电池保护解决方案

引言:功率MOSFET需要串联连接在锂离子电池组和输出负载之间,同时专用锂电池保护IC用于控制MOSFET的导通和关断,以管理电池的充电和放电。 在诸如手机、笔记本电脑等消费电子系统中,具有控制IC、功率MOSFET和其他电子部件的完整电路系统称为保护电路模块(PCM)。

1.背靠背连接的功率MOS

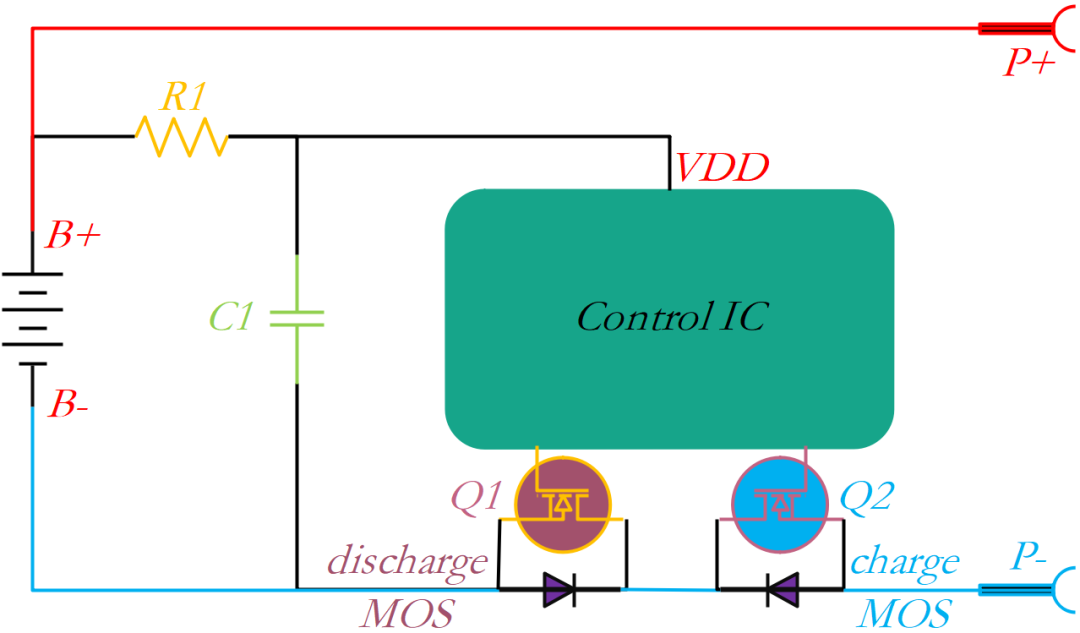

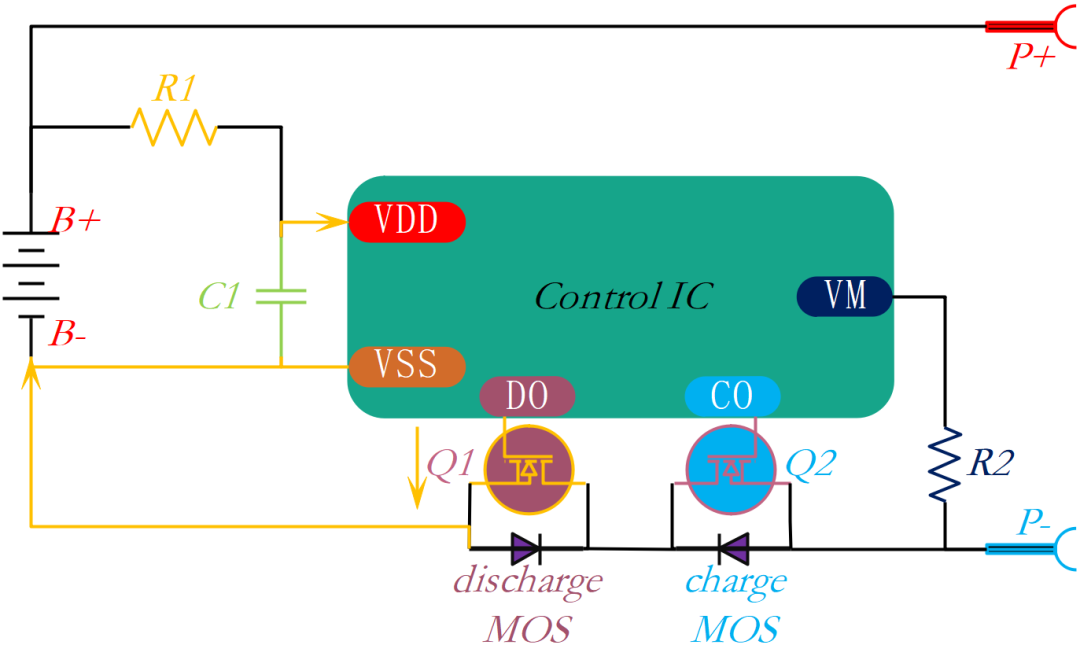

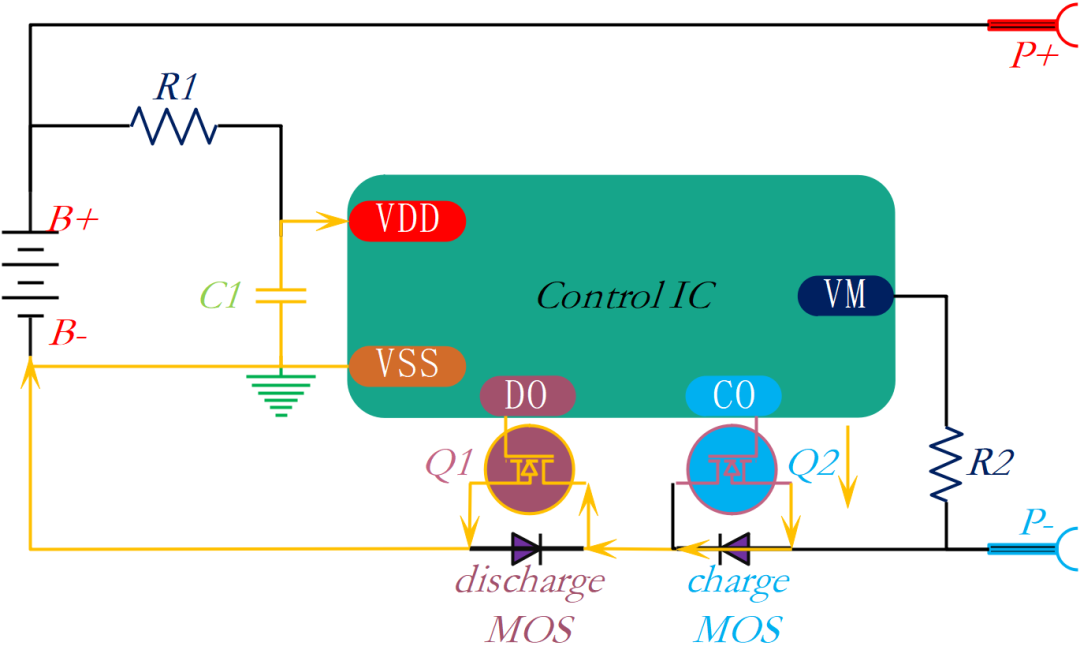

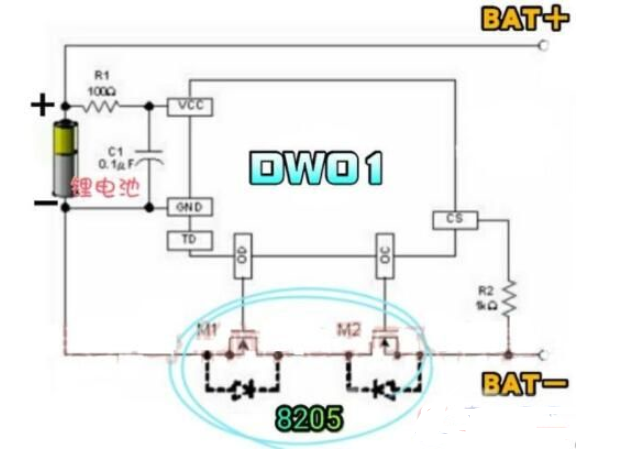

如图1-1所示,在PCM中一个功率MOSFET用于充电,另一个用于放电。 功率MOSFET以两种配置背靠背串联连接:一种配置是两个功率MOSFET漏极D连接在一起。 在第二种配置中,两个功率MOSFET源极S连接在一起(传送门:SCD-4:如何用双MOS设计分立式负载开关? )。 此外还有有两种方法可以将功率MOSFET与电池串联:一种方法是将其放置在电池的负端,称为“接地端”或低侧; 另一种是将其放置在电池的正极,称为高压侧。 两种不同的功率MOSFET背对背连接模式及其不同的放置方式有其各自的优点和缺点,对应于不同的系统要求。

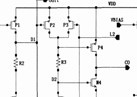

图1-1:背靠背共漏NMOS配置电池保护板电路简图

PCM需要低导通电阻MOSFET,因此通常使用N沟道功率MOSFET。 由于驱动简单灵活,一些应用在正端的也会使用P沟道MOSFET。 但是P沟道MOSFET的导通电阻要相对高于N沟道MOSFET,价格也偏高,并且选择也受到限制。

2. 工作原理

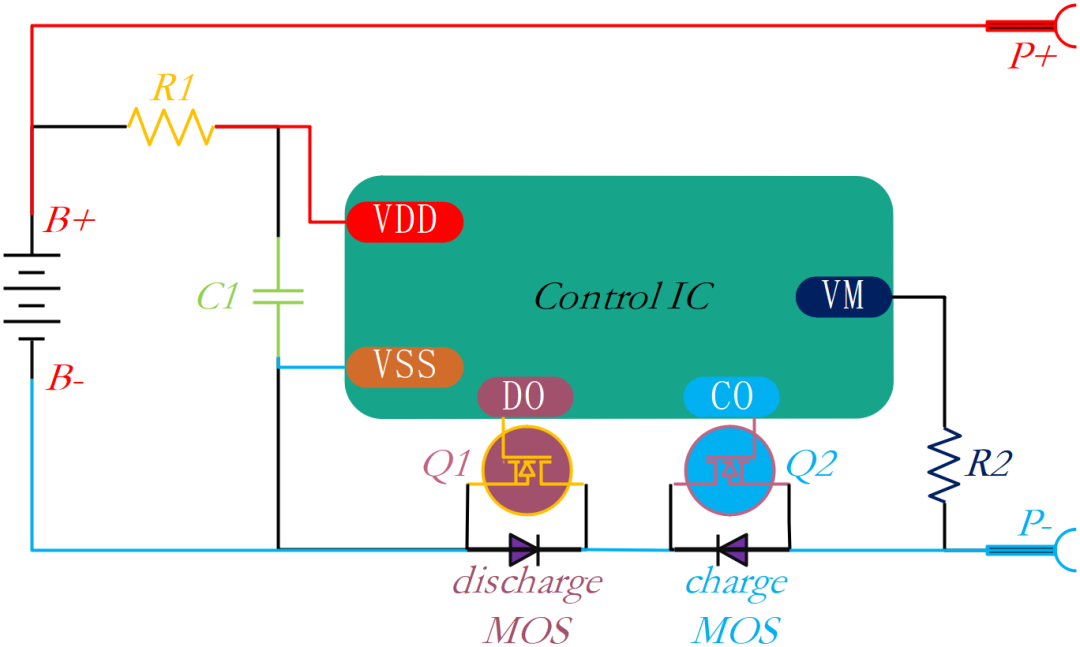

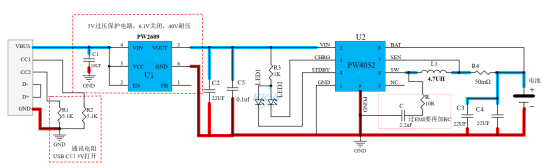

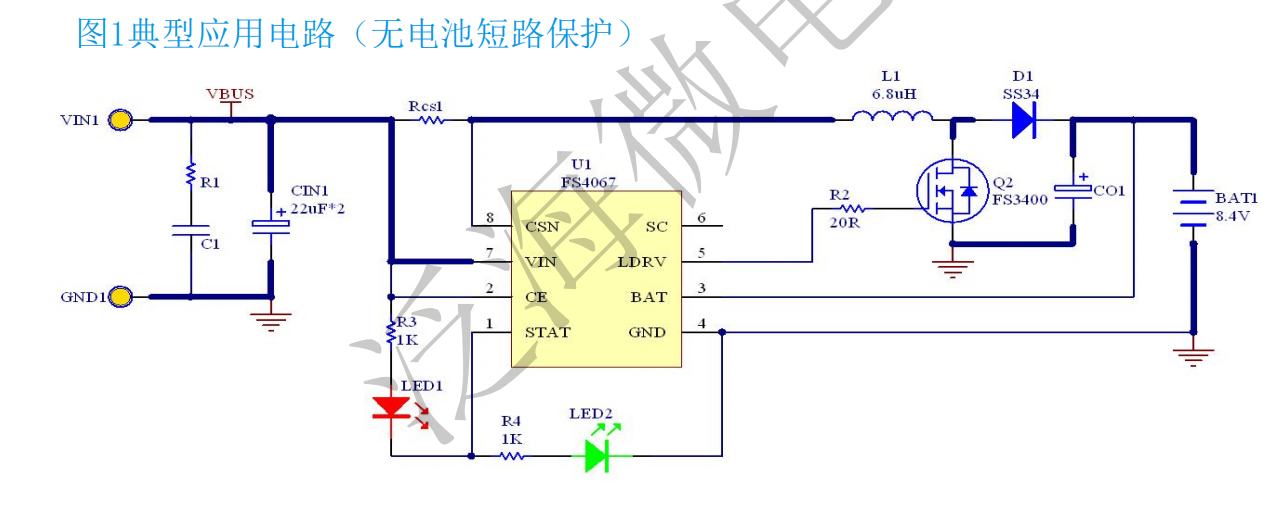

如图1-2,用于管理充电和放电的两个N沟道功率MOSFET位于接地端,漏极背靠背连接,这是PCM的常见方案之一。 在该配置中,Q1是用于电池放电的功率MOSFET,Q2是用于电池充电的功率MOSFET,B+是电池的正极,B-是电池的负极,P+是电池组的正极,P-是电池组负极,VSS是电池保护管理IC的接地,电池的负极,VSS和Q1的源极连接在一起。 在PCM板工作之前,Q1、Q2均关闭。

图1-2:功率MOSFET接地端和漏极背靠背电路图

充电

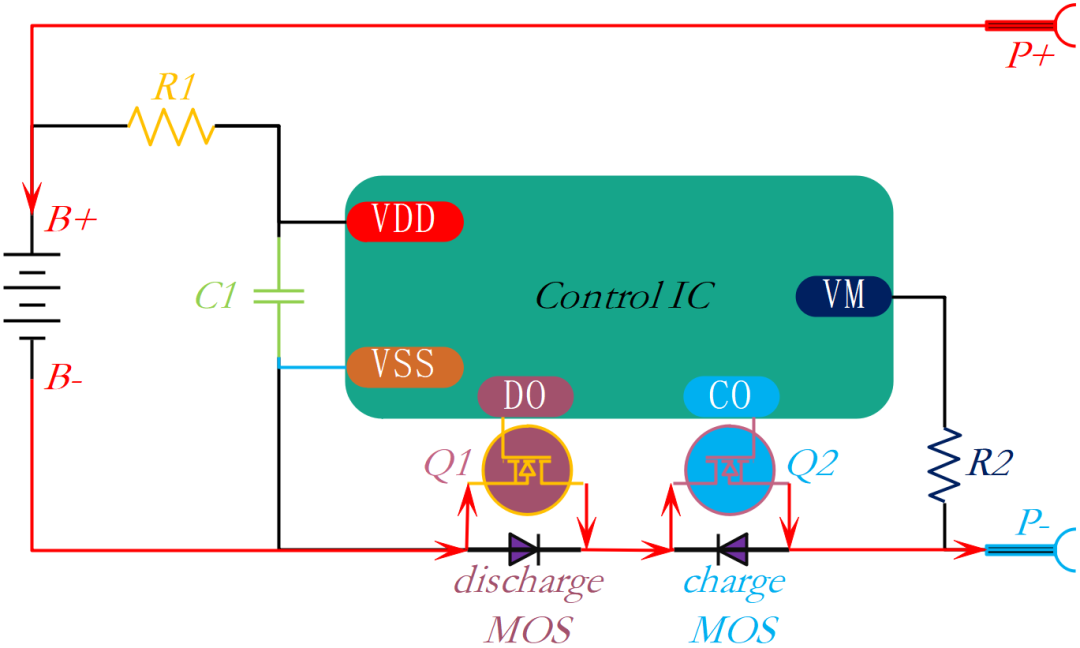

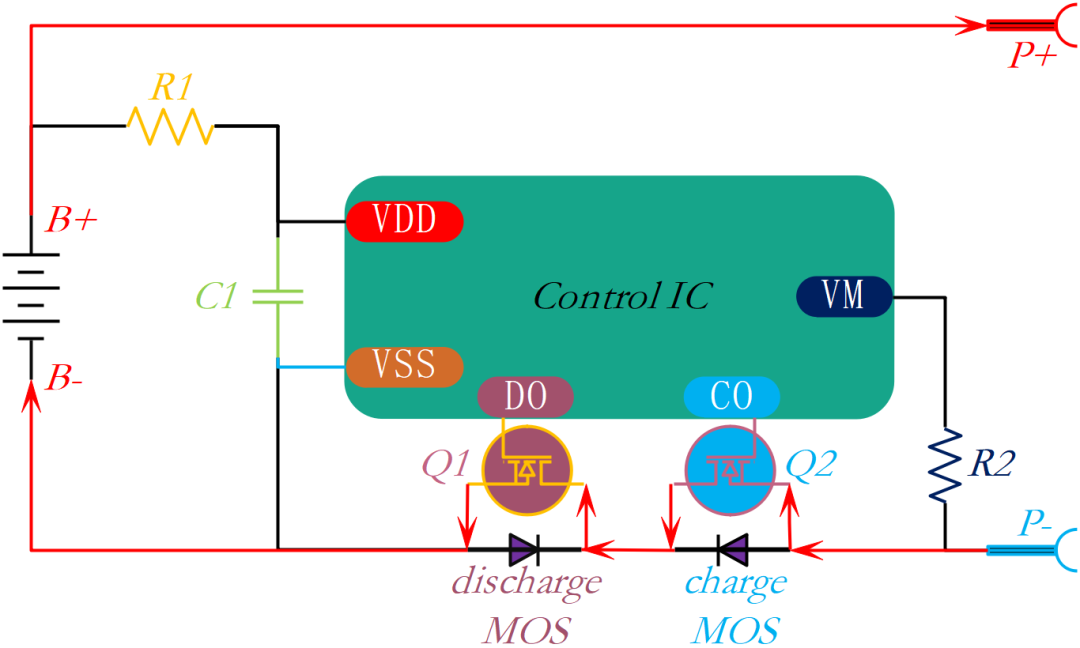

充电时,控制IC向充电功率MOSFET(Q2)的栅极提供驱动信号CO,Q2栅极的驱动信号路径为:外部充电电路的正端→P+→B+→R1→VDD→CO→Q2源极→P-→外部充电电路的负端。 完整的驱动回路如图1-3所示:

图1-3:充电时Q2门的驱动信号回路

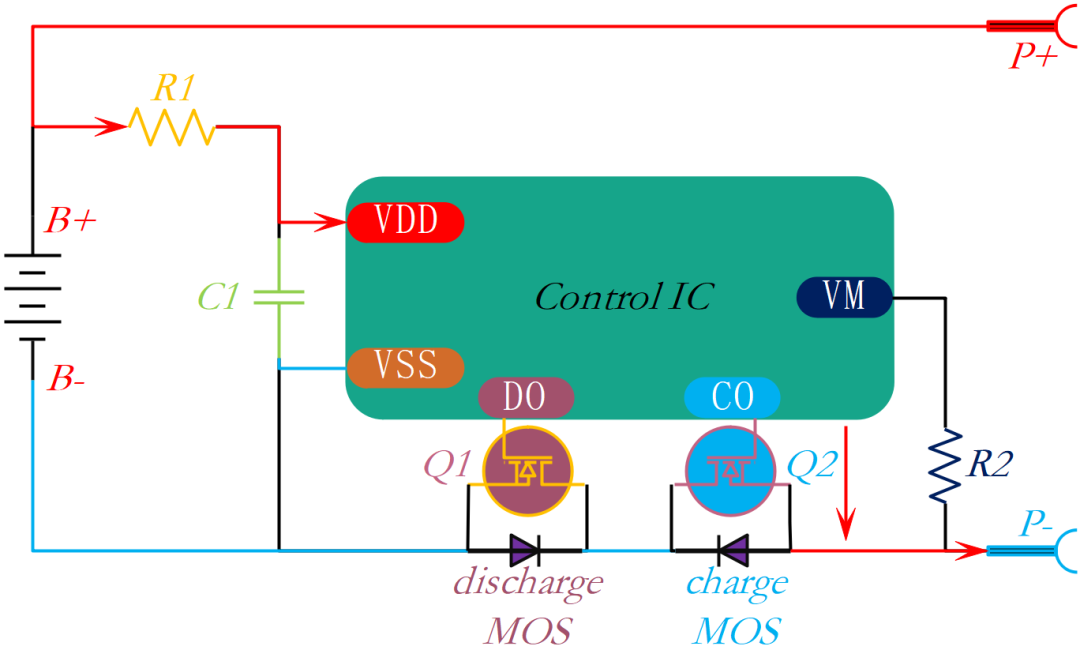

当Q2打开时,充电电流路径为:P+→B+→B-→Q1内部寄生二极管→Q2通道→P-。 然后,可以如图1-4所示对电池进行充电。

图1-4:当Q2打开时的充电回路

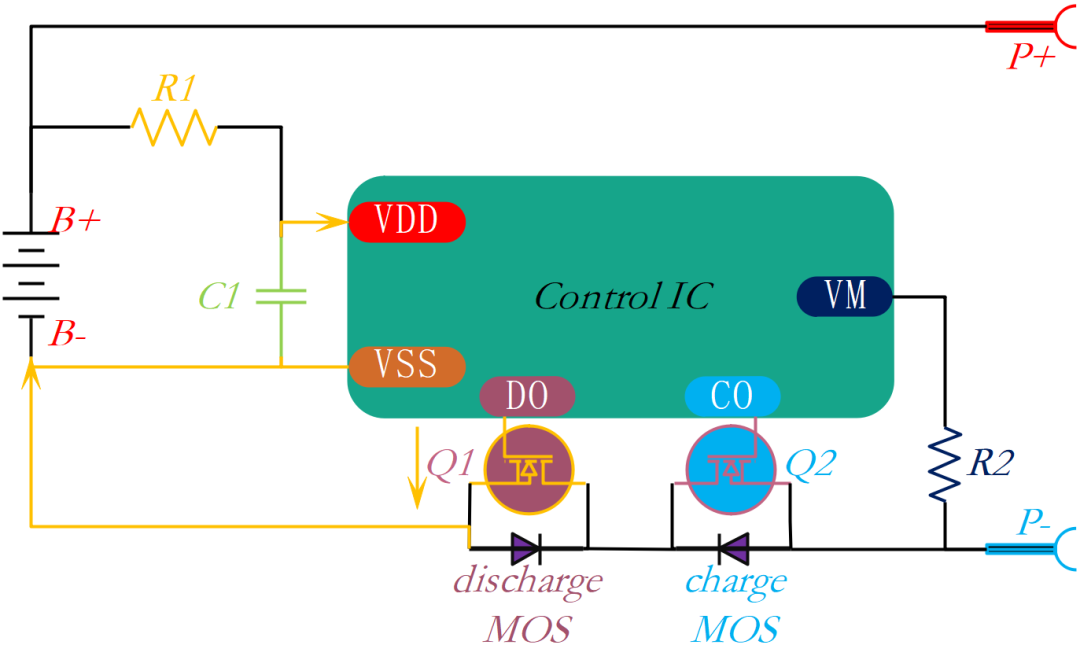

为了减少Q2导通时Q1的损耗,控制IC的DO引脚被拉高以使放电功率MOSFET Q1导通。 由于Q1的低RDSON,其导通损耗远低于寄生二极管的导通损耗,并且可以提高充电效率。 Q1的电流驱动路径为:VDD→DO→Q1栅极→Q1源极→B-→VSS,如图1-5所示:

图1-5:充电期间,当Q2打开时,DO输出Q1驱动信号环路

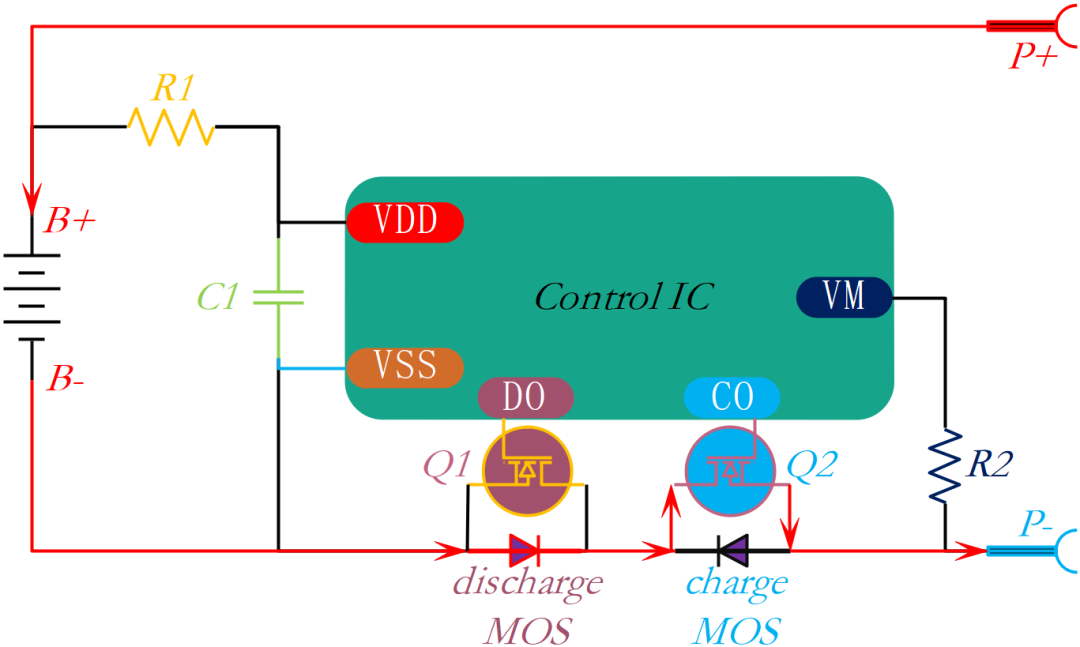

当Q2和Q1同时处于导通状态时,充电电流路径为:P+→B+→B-→Q1通道→Q2通道→P-,如图1-6所示:

图1-6:当Q1和Q2打开时的充电回路

放电:

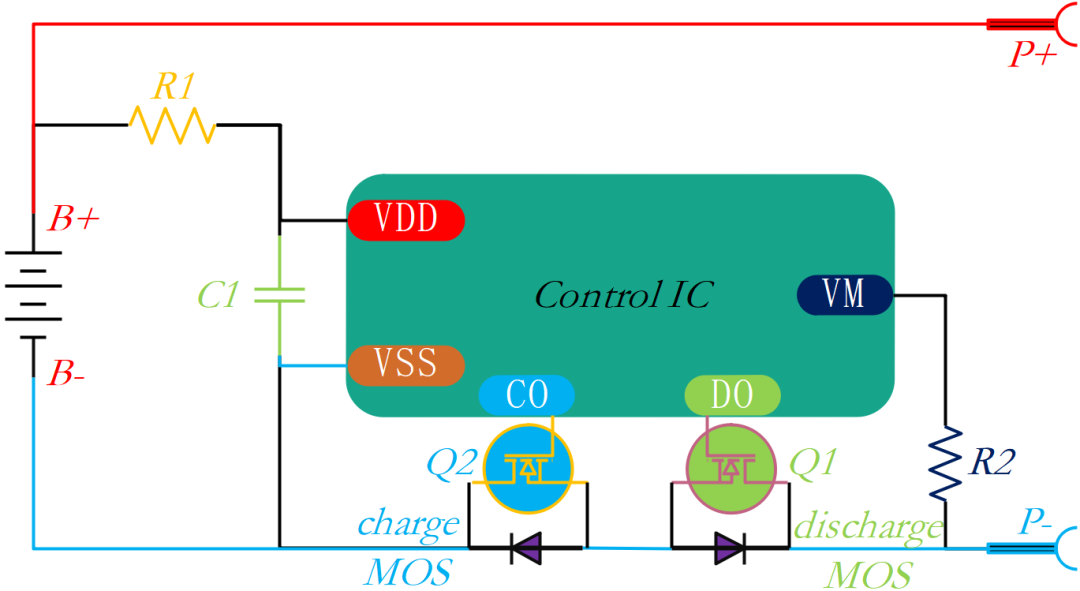

放电时,控制IC向放电功率MOSFET(Q1)的栅极提供驱动信号DO,Q1的栅极驱动信号路径为:VDD→DO(驱动器输出)→Q1栅极→Q1源极→B-→VSS,如图1-7所示:

图1-7:DO输出Q1的放电、驱动信号回路

当Q1导通时,放电电流路径为:P-→Q2内部寄生二极管→Q1通道→B-→B+→P+。 然后电池可以放电,如图1-8所示:

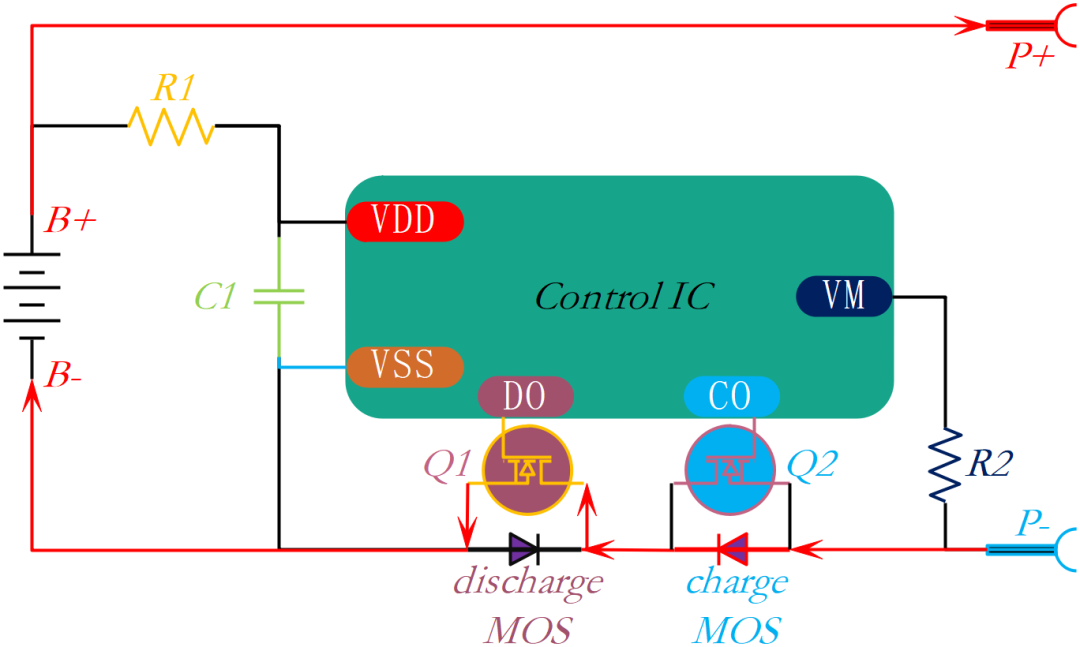

图1-8:Q1接通时的放电回路

为了减少Q2的损耗,当Q1导通时,控制IC向充电功率MOSFET Q2的栅极提供驱动信号CO,从而使Q2导通。 由于Q2的低导通电阻,导通损耗远低于寄生二极管的导通损耗,从而提高电池使用时间。 Q2驱动电流的路径为:VDD→CO→Q2栅极→Q2源极→Q2内部寄生二极管→Q1通道→B-→VSS,如图1-9所示:

图1-9:CO输出Q2的放电、驱动信号回路

Q1和Q2同时处于导通状态,放电电流的路径为:P-→Q2通道→Q1通道→B-→B+→P+,如图1-10所示:

图1-10:Q1和Q2上的放电回路

电子发烧友App

电子发烧友App

评论