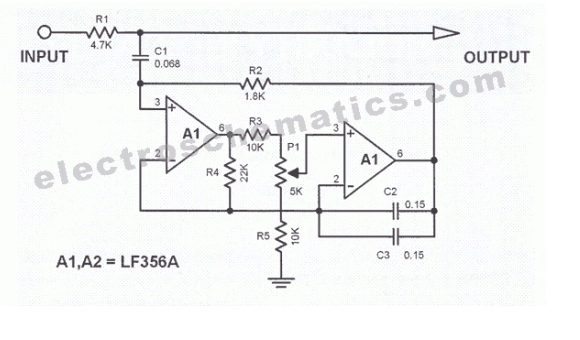

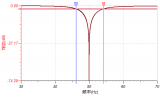

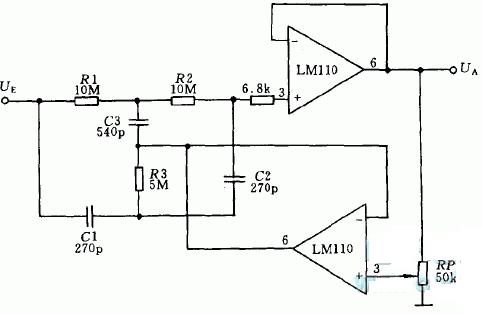

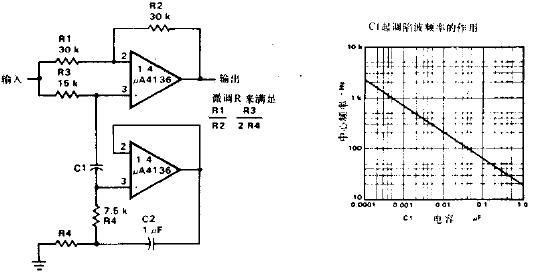

INA110制作的60Hz输入陷波滤波器电路

- 滤波器电路(24151)

相关推荐

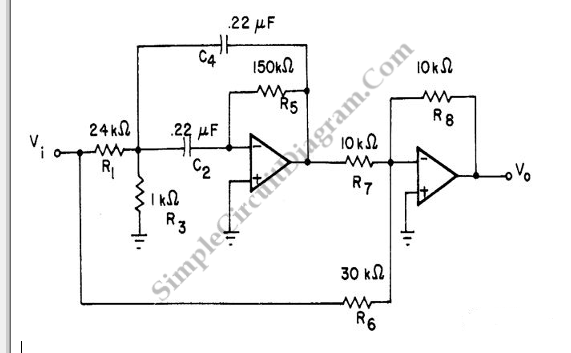

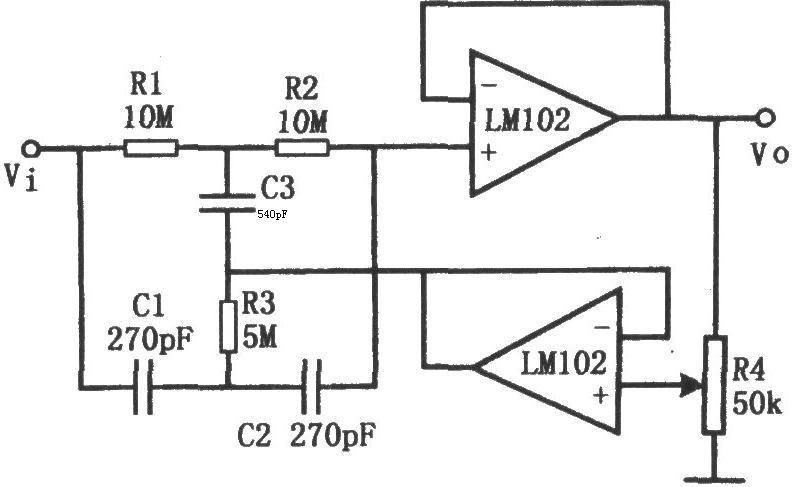

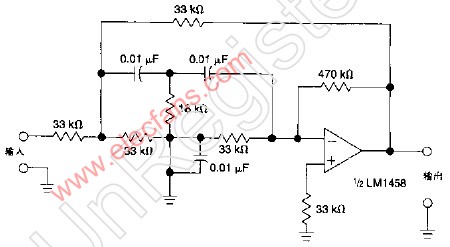

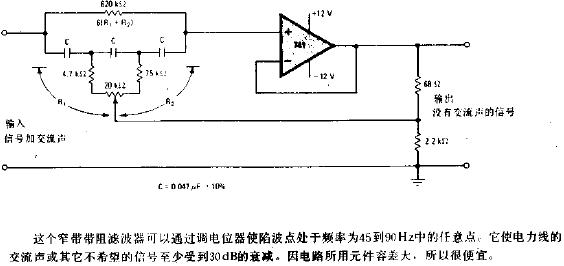

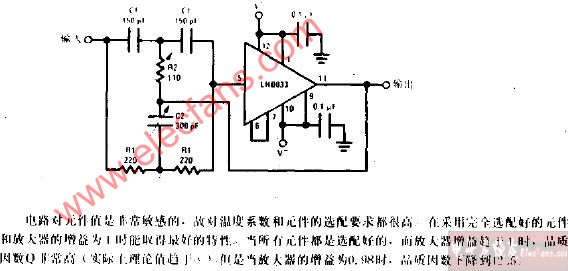

50Hz纹波滤波电路分析

纹波滤波电路经过专门设计,可滤除来自音频线路的50 Hz纹波信号。50 Hz 噪声通常在欧洲国家发现。在许多情况下,不可能消除纹波噪声的原因。特色有源滤波器陷波滤波器解决了 suvh 情况下的问题。它允许期望的信号以最小的衰减通过。在电感值为10 H时,滤波器的Q因数为150。

2023-07-28 14:10:14 597

597

597

597

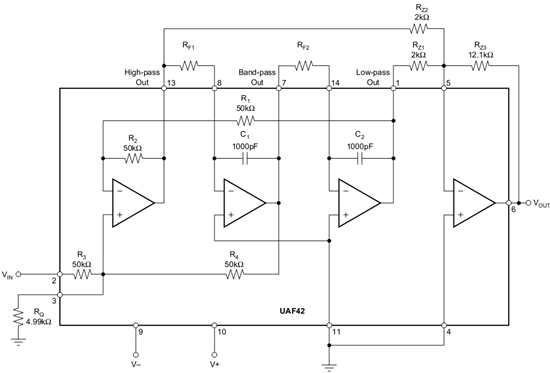

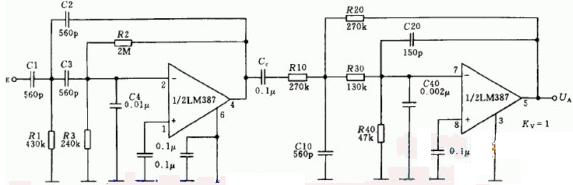

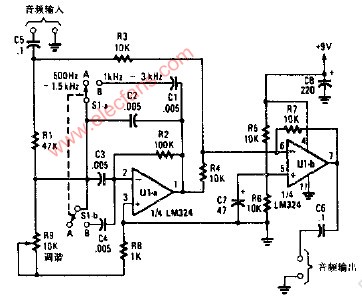

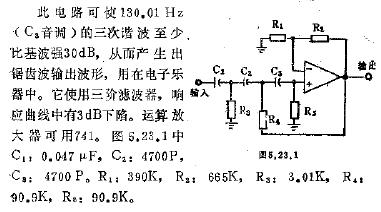

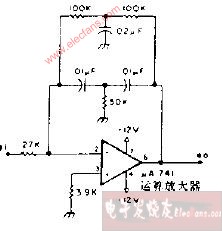

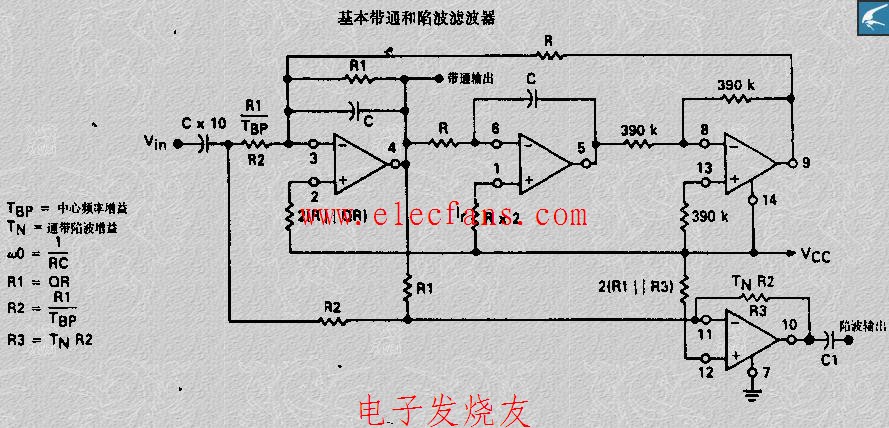

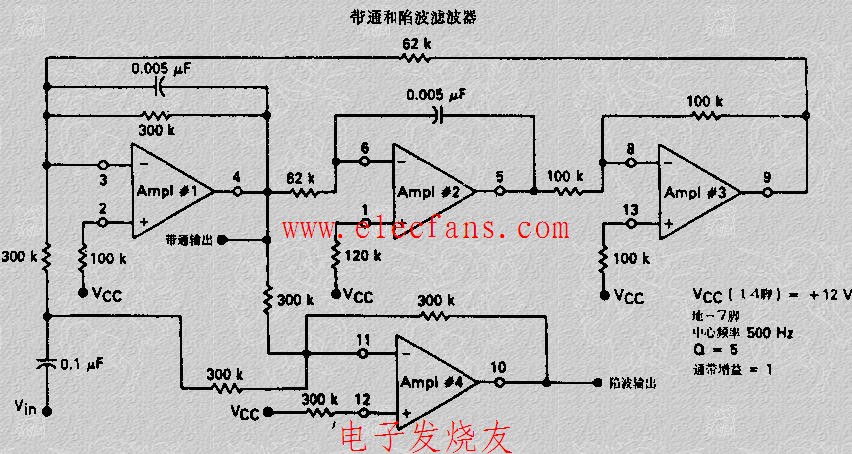

60Hz陷波滤波器电路图

陷波滤波器是去除某个B的滤波器,理想情况下,陷波滤波器将仅去除单点频率分量,但实际上它将去除有限范围的频谱。频谱应具有非常小的带宽,以接近理想的陷波滤波器。下面的电路图设计基于通带增益3和Q值6。运算放大器可以是 741。通过从输入信号中减去带通滤波器的输出信号,得到陷波响应。

2023-07-27 14:44:22 310

310

310

310

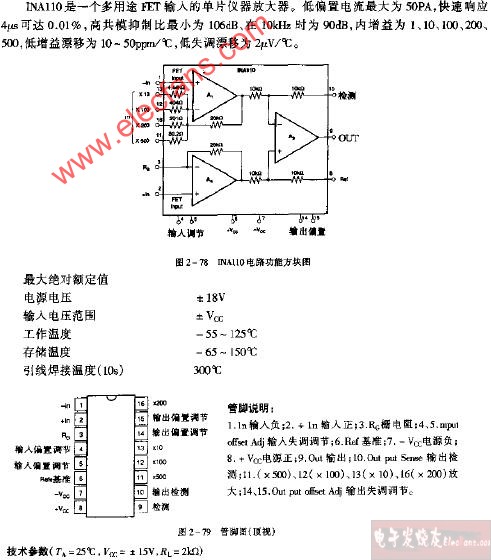

INA110失调电压调节电路

INA110失调电压调节电路本文所应用到的相关器件资料: INA110 600) {i=this.width; j

2008-09-20 09:15:26

理解高性能Σ-ΔADC中时钟公差对50Hz/60Hz噪声抑制的影响

Σ-Δ ADC利用一个调制器将模拟输入转变成一串脉冲。调制器输出端“1”与“0”脉冲之比代表模拟输入的平均值。调制器输出送入一个数字滤波器。Σ-Δ ADC的数字滤波器一般用SINC (Sin(x)/x)函数的脉冲响应低通滤波器实现。该滤波器输出接至抽样电路,以降低输出码率。

2023-02-09 14:21:04 305

305

305

305

了解时钟容差对高性能Σ-Δ型ADC中50/60Hz噪声抑制的影响

本文探讨时钟容差对Σ-Δ型ADC固有的低通抽取和数字滤波器性能的影响,尤其是滤波器陷波频率。低带宽Σ-Δ应用通常利用数字滤波器提供50Hz、60Hz或同步50Hz/60Hz噪声抑制。在选择外部时钟晶体或选择内部时钟时,了解时钟频率与数字滤波器滤波器特性之间的关系非常重要。

2023-01-10 09:48:38 536

536

536

536

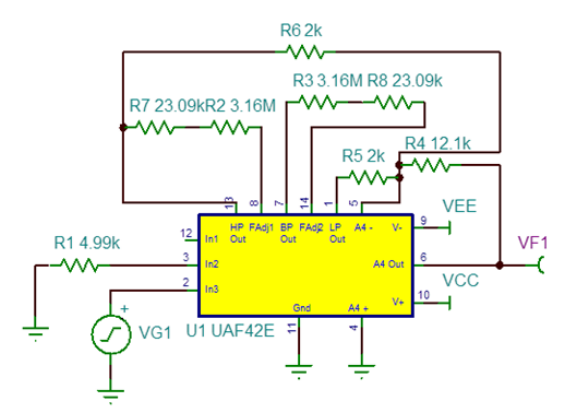

基于UAF42的50Hz陷波器设计与仿真

UAF42是一个集成化的二阶滤波器,可以用来设计复杂的滤波器。众所周知,在滤波器设计时,运放的精度和温度稳定性是关键。UAF42里面集成了两片0.5%精度的1000pF的电容。

在工业应用中,多种

2022-11-30 11:00:31 2

2

2

250HZ转60HZ变频电源规格

50HZ转60HZ变频电源规格特点一般国内的频率是50HZ,其实实际上应该是从50HZ到60HZ之间波动的。那么,变频电源的中港扬盛产品优点是什么:CNZGYS,,,C0M1.具有过压、 过流、过热

2022-01-07 13:33:59 4

4

4

4基于UAF42的50Hz陷波器设计与仿真

Other Parts Discussed in Post: UAF42, ALP基于UAF42的50Hz陷波器设计与仿真【1】

UAF42是一个集成化的二阶滤波器,可以用来设计复杂的滤波器

2021-11-23 16:03:37 2584

2584

2584

2584

Bainter陷波滤波器

Bainter电路是一种简单的陷波滤波器(见参考文献部分),它由简单的电路模块构成,带有两个反馈环路,如图1所示。可以实现低通、高通和标准陷波响应。

2021-03-22 15:51:52 17

17

17

17如何使用UAF42二阶滤波器实现50Hz陷波器的设计与仿真

UAF42是一个集成化的二阶滤波器,可以用来设计复杂的滤波器。众所周知,在滤波器设计时,运放的精度和温度稳定性是关键。UAF42里面集成了两片0.5%精度的1000pF的电容。在工业应用中,多种场合

2020-09-30 10:44:00 3

3

3

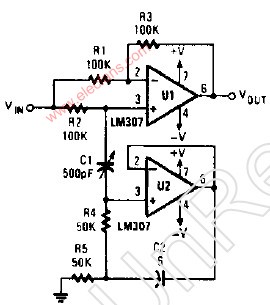

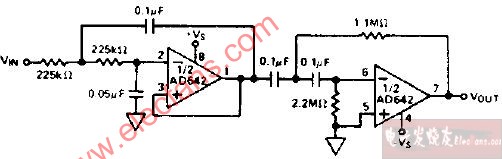

3INA111输入低通滤波电路

关键词:INA111 , 低通滤波 如图所示为输入低通滤波电路。INA111为FET输入,允许在输入端采用RC滤波器而不会因为偏流产生大的失调电压。输入端采用RC低通滤波器可以使INA111具有

2019-02-14 16:05:01 329

329

329

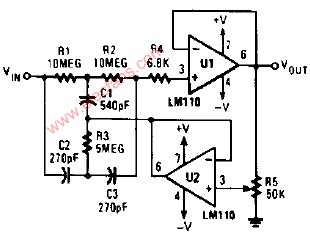

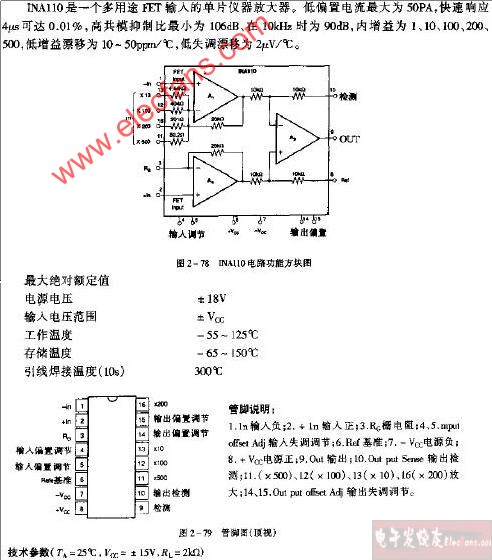

329快速稳定时间FET输入放大器INA110

系统的理想器件,信号可在4μs内稳定到0.01%,其内部电阻提供增益设定为1、10、100、200、500V/V,连接RG可得到所需的增益。输入端提供保护,对于差模和共模输入电压可达±Vcc。极高的输入阻抗和低的输入偏流,使得INA110成为用于输入滤波或输入保护电路的理想器件。INA11

2019-02-12 11:46:01 599

599

599

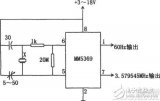

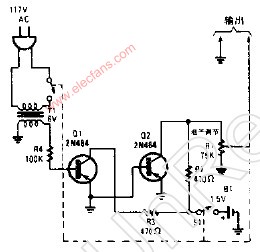

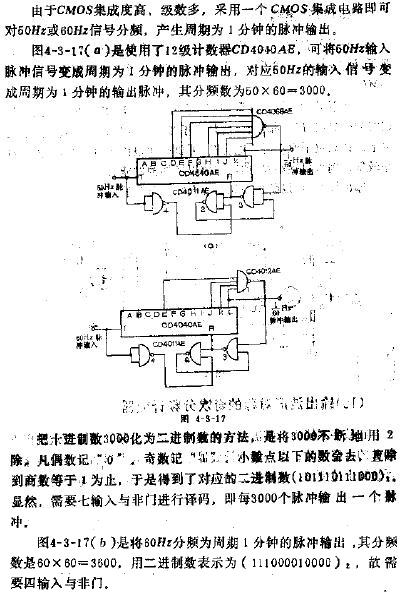

599基于60Hz脉冲的发生电路设计

60Hz脉冲信号是时钟电路常用到的信号。本文介绍一种60Hz脉冲信号发生电路,分析其存在的误差,并给出减少误差的改进电路。

2019-02-05 01:56:00 3922

3922

3922

3922

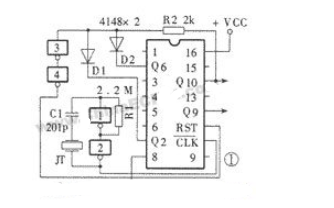

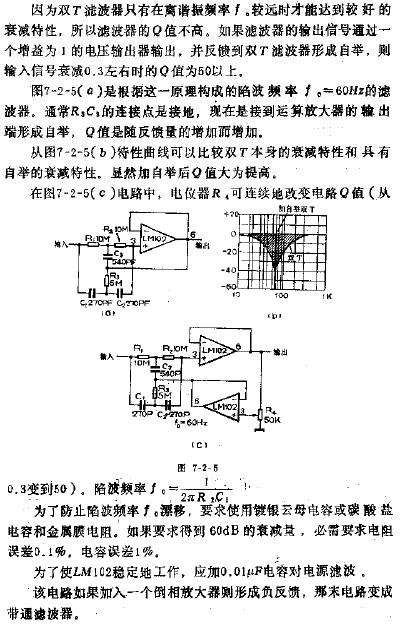

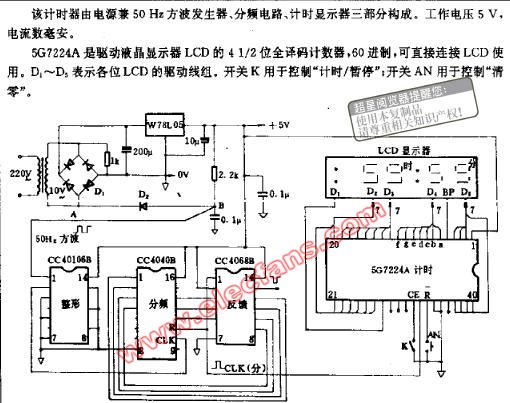

将50Hz或60Hz频率变成1/60频率的分频器(CD4040)

关键词:CD4040 , 分频器 如图所示为将50Hz或60Hz频率变成1/60频率的分频电路。由于CMOS集成度高,级数多,采用一个CMOS集成电路即可对50Hz或60Hz信号进行分频,产生周期为

2018-10-03 18:43:02 2296

2296

2296

229660Hz时基信号发生电路,60Hz timer circuit

60Hz时基信号发生电路,60Hz timer circuit

关键字:时钟信号发生电路,CD4060信号发生器

附图1电路是由12为

2018-09-20 19:22:32 1343

1343

1343

1343时钟调谐的高选择性陷波滤波器

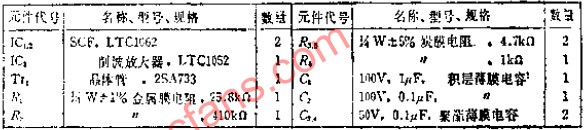

该电路示出了一种通过改变单个电阻器的阻值来调谐一个陷波滤波器中心频率的快速和简洁的方法,可对此电路进行开关切换。LTC1062 开关电容器滤波器和 A1 形成了一个时钟可调谐型陷波滤波器 (见

2018-06-29 18:43:30 196

196

196

196图示60Hz时基发生电路

如图所示为60Hz时基发生电路。在很多场合,60Hz已经成为一个基准参考频率,如电子钟、定时器、控制器等,都设计以60Hz为其工作参考信号。因此常常需要一个独立的60Hz信号源,以适用于便携式或由

2018-06-01 14:33:00 2665

2665

2665

2665

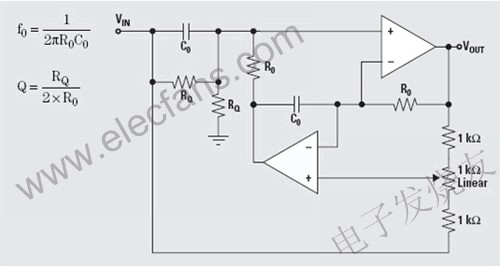

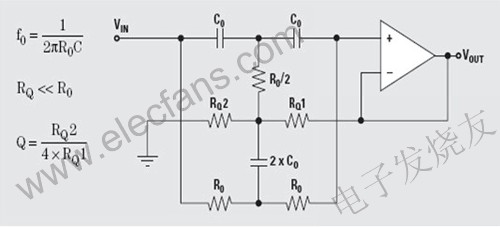

使用UAF42设计一个高性能的50Hz陷波器

场合需要用到50Hz陷波器。本节将介绍使用UAF42设计一个高性能的50Hz陷波器。使用UAF42来设计50Hz陷波器,只需要外加6个电阻即可组成一个50Hz陷波器。如下图所示 UAF42的辅助运放将高通和低通滤波器的输出相加,即得到陷波器。陷波器的陷波频率由下面的公式所决定,

2018-04-27 10:00:30 15868

15868

15868

15868

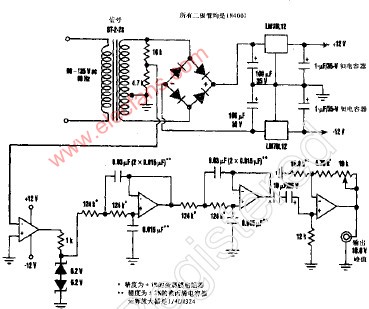

电源滤波器参数

电源滤波器是由滤波电感、电容组成的无源器件。它允许工频(50Hz、60Hz、400Hz)通过,而对电磁干扰信号有很大的衰减。电源滤波器双向可逆,既能防止电网上的电磁干扰通过电源进入设备,又能防止设备本身产生的电磁干扰对电网造成污染,是抑制传导干扰的有效配置。

2018-01-12 10:40:18 5174

5174

5174

5174

TI 工程师原创 - 基于UAF42的50Hz陷波器设计与仿真

基于UAF42的50Hz陷波器设计与仿真【1】 UAF42是一个集成化的二阶滤波器,可以用来设计复杂的滤波器。众所周知,在滤波器设计时,运放的精度和温度稳定性是关键。UAF42里面集成了两片0.5%精度的1000pF的电容。在工业应用中,多种场合需要用到50Hz陷波器。

2017-04-08 10:37:12 4161

4161

4161

4161

基于集成化的二阶滤波器UAF42设计50Hz陷波器

UAF42是一个集成化的二阶滤波器,可以用来设计复杂的滤波器。本文介绍了如何基于UAF42设计一个高性能的50Hz陷波器,并使用免费的仿真软件TINA对这个电路进行了仿真分析,供工程师参考和学习。

2015-10-06 11:07:00 2523

2523

2523

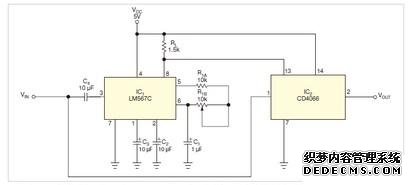

2523PLL陷波滤波器可以用于阻拦不需要的频率

经常有要阻挡某些频率信号的情况,其中最常见的是50Hz或60Hz的电力线工频。图1中的PLL陷波滤波器可以用于阻拦不需要的频率。

2011-03-12 10:30:21 1817

1817

1817

1817

CD4040和CD4069构成的60Hz数字钟时基电路

CD4040和CD4069构成的60Hz数字钟时基电路

图1电路是由12为二进制串行计数器/分频器CD4040

2010-10-06 09:43:47 7179

7179

7179

7179INA110,pdf(Fast-Settling FET-I

The INA110 is a versatile monolithic FET-input instrumentation amplifier. Its current-feedback

2010-09-24 21:27:54 8

8

8

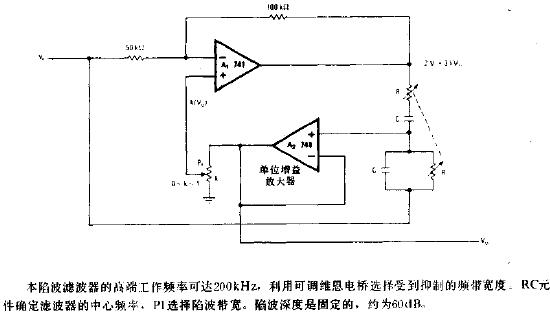

8高速陷波滤波器低功耗无线应用

有源陷波滤波器在过去就已被广泛用来消除50 到60Hz 的噪声干扰,但在中心频率(f0) 的调谐、稳定性和可重复性方面,有源陷波滤波器尚存在不足之处。高速放大器的出现使设

2010-09-07 17:04:00 14

14

14

14Fliege陷波滤波器的拓扑结构

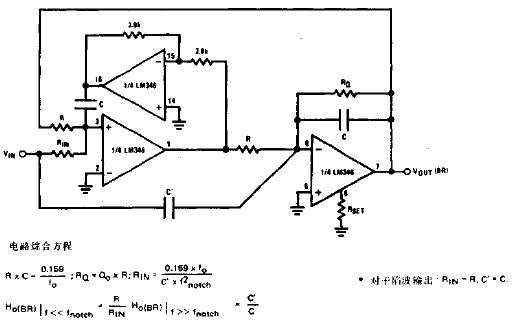

Fliege 陷波滤波器的拓扑结构如图 所示,该滤波电路与双 T 结构相比具有以下优势:仅用四个高精度组件(两个 RS 和两个 CS)就可实现中心频率的调谐。该电路的一个重要特点是允

2010-09-03 11:25:27 1657

1657

1657

1657

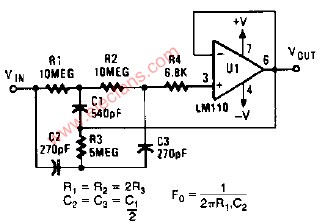

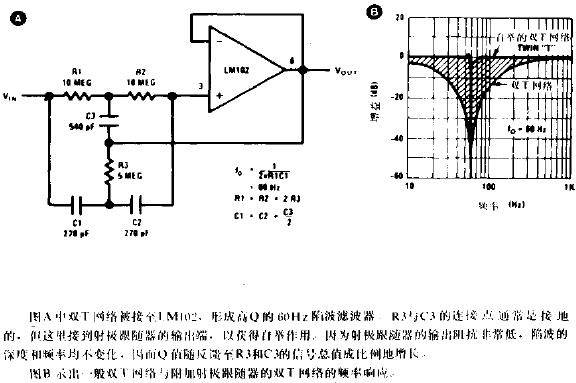

双T陷波滤波器拓扑结构图

双 T 陷波滤波器

这里值得一提的是图中的双 T 拓扑结构,因为可以利用一个运算放大器来实施一个陷波滤波器。由于中心频率难以调整,所以该滤波器并不像想象中的那样

2010-09-03 11:24:14 3533

3533

3533

3533

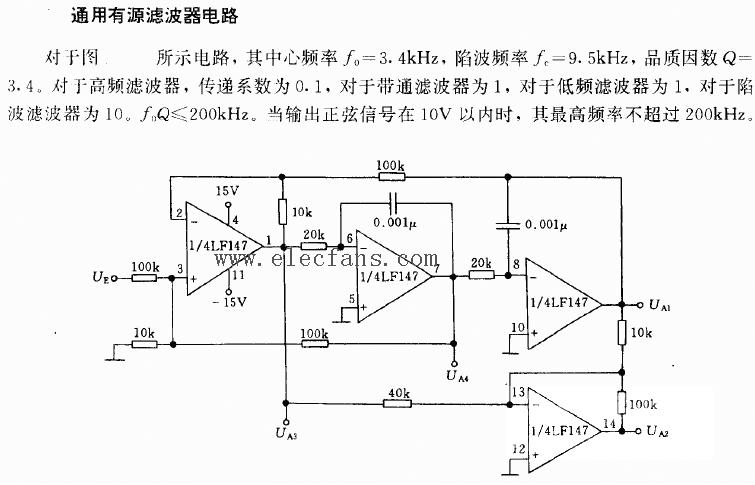

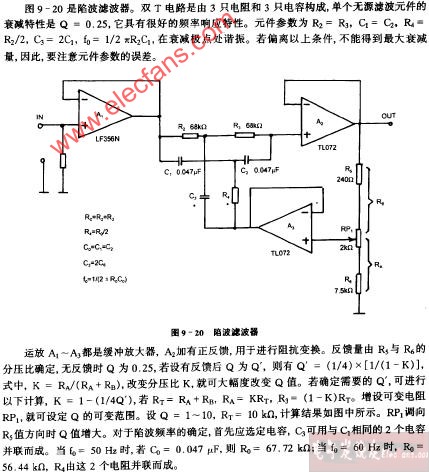

通用有源滤波器电路

通用有源滤波器电路

对于下图的有源滤波器电路,其中心频率为fo=3.4khz,陷波频率为fc=9.5khz,品质因数Q=3.4.对于高频滤波器,传递系数为0.1,对于带通滤滤波器

2009-12-07 11:36:59 1132

1132

1132

1132理解高性能ADC中时钟公差对50Hz/60Hz噪声抑制的影响

摘要:本文探讨了时钟公差对Σ-Δ ADC中低通抽样和数字滤波器的影响,特别是对滤波器陷波频率的影响。窄带Σ-Δ应用通常利用数字滤波器提供50Hz、60Hz或50Hz/60Hz的噪声抑制。在选择

2009-05-07 11:35:53 723

723

723

723

理解高性能ADC中时钟公差对50Hz/60Hz噪声抑制的影响

摘要:本文探讨了时钟公差对Σ-Δ ADC中低通抽样和数字滤波器的影响,特别是对滤波器陷波频率的影响。窄带Σ-Δ应用通常利用数字滤波器提供50Hz、60Hz或50Hz/60Hz的噪声抑制。在选择

2009-04-24 14:11:59 755

755

755

755

理解高性能Σ-Δ ADC中时钟公差对50Hz/60Hz噪声抑

摘要:本文探讨了时钟公差对Σ-Δ ADC中低通抽样和数字滤波器的影响,特别是对滤波器陷波频率的影响。窄带Σ-Δ应用通常利用数字滤波器提供50Hz、60Hz或50Hz/60Hz的噪声抑制。在选择

2009-04-20 15:53:19 586

586

586

586

有源滤波器电路图

如图所示,其中心频率为F=3。4KHZ,陷波频率为F=9.5kHZ,品质因素为Q=3.4.对于高频滤波器,传递系数0。1,对于带通滤波器为1,对于低通滤波器为1,对于陷波滤波器为10,F小于等于200

2008-05-09 10:24:10 3147

3147

3147

3147

电子发烧友App

电子发烧友App

评论