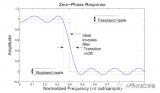

Scopel显示的是50Hz正弦波,Scope2显示的是50Hz叠加上250Hz、350Hz正弦波后的波形,Scope显示的是通过我们设计的低通滤波器后的波形,对比图3(a)、(b)可以看出,滤波后的波形保留了50Hz的信号,且略有延迟,并将高频部分有效地滤除,说明设计的滤波器符合要求。

3、数字低通滤波器FPGA实现

数字滤波器的实现方法一般有以下几种:

(1)采用加法器、乘法器、延时器设计专用的滤波电路。

(2)在通用计算机系统中加上专用的加速处理机设计实现。

(4)用专用的DSP芯片实现。在一些特殊的场合,要求的信号处理速度极高,用通用DSP芯片很难实现。这种芯片将相应的滤波算法在芯片内部用硬件实现,无需进行编程。

(5)采用FPGA/CPLD设计实现。

在上述几种方法中,第(2)种方法的缺点是速度较慢,一般可用于DSP算法的模拟。第(1)、(4)种方法专用性强,应用受到很大的限制。第(3)、(5)种方法都可以通过编程来实现各种数字滤波,使用DSP器件实现虽然简单,但由于程序顺序执行,执行速度必然不快。FPGA有着规整的内部逻辑阵列和丰富的连线资源,特别适合于数字信号处理任务,相对于串行运算为主导的通用DSP芯片来说,其并行性和可扩展性更好。但长期以来,FPGA一直被用于系统逻辑或时序控制上,很少有信号处理方面的应用,其原因主要是因为在FPGA中缺乏实现乘法运算的有效结构。现在这个问题得到了解决,使FPGA在数字信号处理方面有了长足的发展。

在MATLAB中设计出数字低通滤波器后,得到其系统函数H(z)的系数,然后将系数转换为二进制,再利用VHDL语言进行编程,而编程的过程非常繁琐。

本文利用FDATool可以直接得到VHDL文件,在其菜单栏中的选择Fargets\GenerateHDL,在打开的界面中选择VHDLfile,建立文件名为filter.vhd,同时可以得到测试文件filtertb.vhd。利用QuartusII软件打开以上文件进行编译、综合,最后将其下载到FPGA中即可实现低通滤波器的功能。

4、结束语

本文利用Matlab中的FDATool实现了IIR数字低通滤波器的设计及仿真,设计过程简单、直接,大大缩减了设计开发的时间。采用FPGA进行滤波器的硬件设计,能够达到谐波检测实时性和准确性的要求,为电力有源滤波器谐波检测中低通滤波器的设计提供了参考。同时在实际应用中,可以方便地对滤波器参数进行修改,很容易实现其他各种滤波器的设计,具有一定的工程设计参考价值。

电子发烧友App

电子发烧友App

评论