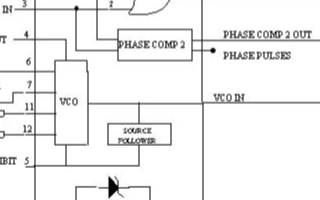

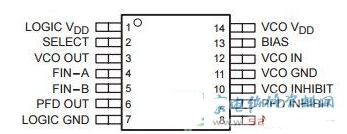

74HC046/74HCT4046A- -带压控振荡器(VCO)的锁相环电路概述:74HC/HCT4046A 是高速硅门CMOS 器件,与“4000B”系列的“4046”引脚兼容,并且符合JEDEC

2008-10-10 17:31:41

锁相环是如何实现倍频的? 锁相环(Phase Locked Loop, PLL)是一种电路,用于稳定和恢复输入信号的相位和频率。它可以广泛应用于通信、计算机、音频等领域中。其中一个重要的应用就是

2023-09-02 14:59:37 386

386 硬件锁相环电路怎么设计?硬件锁相环电路的设计通常包括以下步骤。

2023-08-08 11:16:46 223

223 锁相环电路,是调频电路的重要组成之一,锁相环电路的原理的认识是DDS学习的一个重点之一。

2023-07-24 15:37:05 791

791

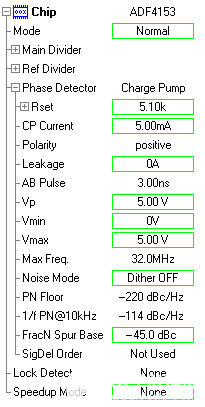

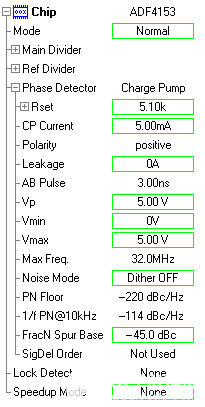

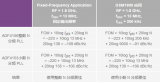

许多工程师对如何选择参考频率感到困惑,但参考频率和输出频率阶跃之间的关系很简单。对于整数N分频PLL,输出频率阶跃等于鉴频鉴相器(PFD)输入端的频率,即参考频率除以参考分频器R。对于小数N分频PLL,输出频率阶跃等于PFD输入频率除以MOD值,因此您可以使用较高的参考频率来获得较小的频率步进。在决定是使用整数N还是小数N分频时,频率阶跃可以用相位噪声换取,PFD频率越低,输出频率分辨率越好,但相位噪声越差。

2023-01-30 15:25:32 739

739

锁相环 (PLL) 电路存在于各种高频应用中,从简单的时钟清理电路到用于高性能无线电通信链路的本振 (LO),再到矢量网络分析仪 (VNA) 中的超快速开关频率合成器。本文解释了锁相环电路的一些构建模块,并参考了每种应用,以帮助指导新手和锁相环专家导航器件选择以及每种不同应用固有的权衡取舍。

2022-12-23 14:03:54 2293

2293

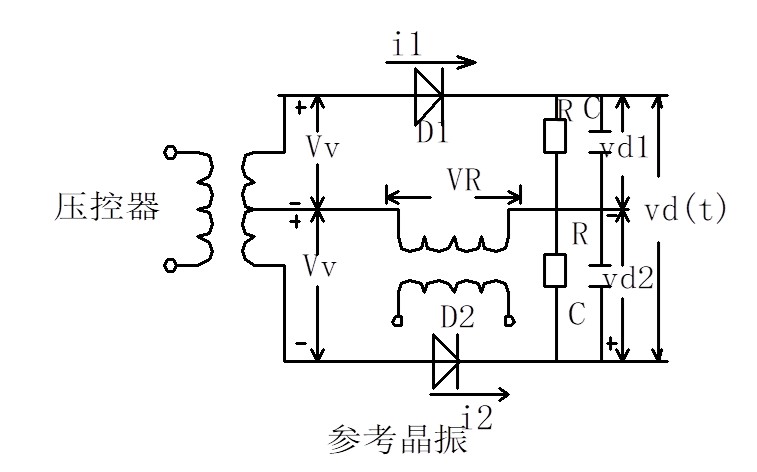

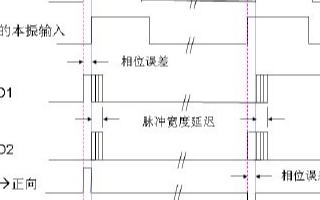

鉴相器是锁相环路的关键部件。在频率合成器中所采用的鉴相器主要有正弦波相位检波器与脉冲取样保持相位比较器两种。

2022-11-11 16:56:47 2674

2674

晶振通常配合和锁相环电路配合使用,以提供系统所需要的时钟频率,如果不同子系统需要不同频率的时钟信号,可以用与同一个晶振相连的不同锁相环来提供。

2022-08-06 15:40:22 1222

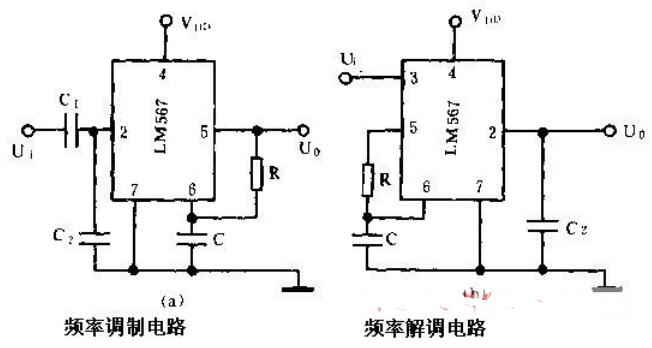

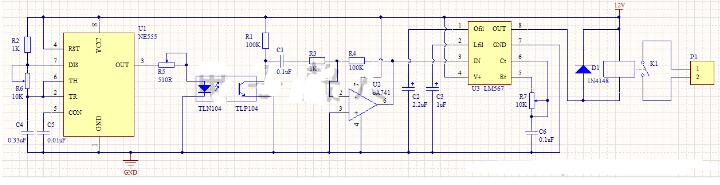

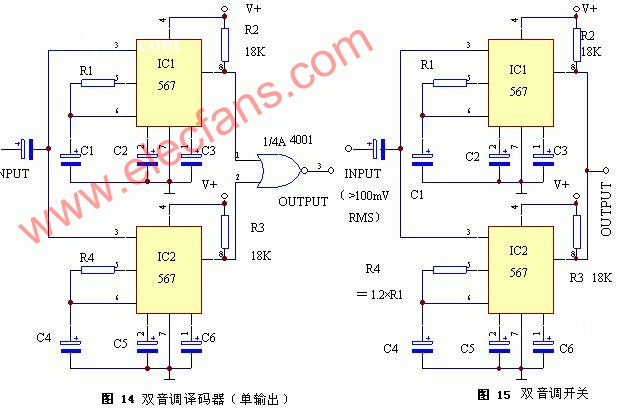

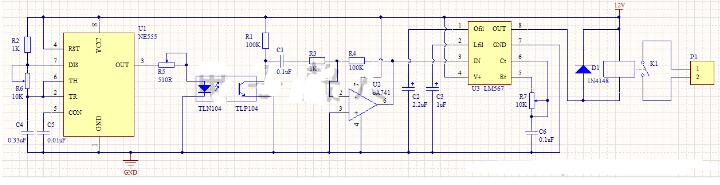

1222 LM567为通用锁相环电路音调译码器,本电路是用LM567组成的调制电路和解调电路。

2021-05-01 16:47:00 3930

3930

有一些网友学不好LM567的锁相环电路(主要是指我自己),主要是总是跑频,下面是一个网友发给我的电路,我感觉非常的好,就发上来分享了。

2021-04-05 17:35:00 1609

1609

,已经成为电子设备中常用的基本部件之一。为了便于调整,降低成本和提高可靠性,目前已有多种不同性能的集成锁相环电路,主要分为模拟和数字两种。

2021-03-31 11:59:11 3409

3409

如果没有深入了解 PLL 理论以及逻辑开发过程,可能你在设计并调试锁相环(PLL)电路时会感到非常棘手。那有没有比较容易理解或学习妙招呢?小A今日就为大家送上一份妙计锦囊,并提供有效、符合逻辑的方法

2021-02-24 07:35:28 15

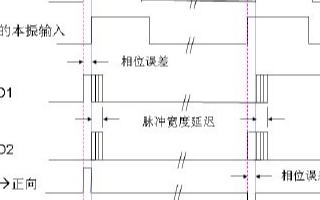

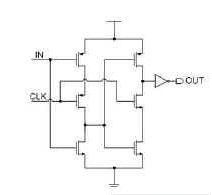

15 电荷泵锁相环的锁定检测电路设计,包括模拟锁定检测和数字锁定检测两种方法。其中,模拟检测电路采用经鉴频鉴相器PFD 输出的相位误差,产生脉冲信号对外部电容进行充电和放电,需要较长的时间以达到稳定的电平

2020-08-24 14:11:38 2743

2743

的相位变换,提出了一种基于锁相环(PLL)的QPSK调制器。由于采用了三输入异或门和求和电路,该系统中的锁相环电路不同于传统的锁相环电路。利用这些附加组件,所提出的PLL在QPSK信号中提供连续的相位变化。因此,当使用所述电路时,传输QPSK信号所需的带宽

2020-05-15 08:00:00 3

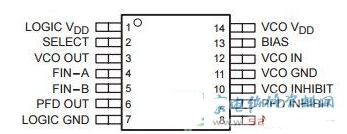

3 TLC2932是德州仪器公司出品的一款锁相环电路(PLL)芯片,它由压控振荡器和以沿触发方式工作的鉴相器(PFD:phflsefrequencydeteclor)组成。

2020-03-30 15:52:23 2674

2674

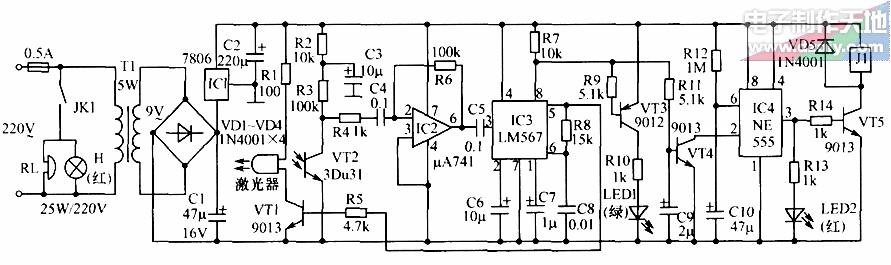

本例电路利用555芯片,LM567通用锁相环电路音调译码器芯片和红外发射接收管组成的红外开关控制电路,可用于自动水龙头的控制。

2019-10-01 15:00:00 5875

5875

如果不在特定条件下进行仿真,则估计一个 PLL 电路的规格将会是十分困难的。因此,进行 PLL 设计的第一步应当是仿真。建议工程师使用ADIsimPLL 软件运行基于系统要求的仿真,包括参考频率、步进频率、相位噪声(抖动)和频率杂散限制。

2019-07-24 11:09:04 2630

2630

锁相环(PLL)是模拟电路中的一个重要模块,本文研究的是广泛使用的电荷泵型锁相环(CPPLL)。锁相环电路通过比较参考输入和输出反馈信号的频率/相位,并将此特征转化为电压,然后通过与压控振荡器

2019-06-14 08:03:00 2892

2892

如果不在特定条件下进行仿真,则估计一个 PLL 电路的规格将会是十分困难的。因此,进行 PLL 设计的第一步应当是仿真。

2019-05-08 17:47:19 5071

5071

一。 试验要求:1. 用systemview设计并仿真一个完整的数字锁相环电路。2. 试验条件设定

信号速率 10Hz

系统采样时钟设定:100Hz

2019-01-29 11:15:08 69

69 如图所示为大范围激光防盗报警器电路。电路的核心是以IC3(LM567)及其外围阻容元件构成的锁相环电路。

2019-01-26 07:28:00 3889

3889

锁相环电路当用作选频时,它的选频频率主要由6、7脚间外接的电容值和11脚外接电阻值决定,只要选定了这几个元件的参数,锁相环的压控振荡器的中心频率即被确定,锁相环的选频频率也就被确定。

2018-05-04 10:04:00 1835

1835

本文实现了一种全集成可变带宽中频宽带低通滤波器,讨论分析了跨导放大器-电容(OTA—C)连续时间型滤波器的结构、设计和具体实现,使用外部可编程电路对所设计滤波器带宽进行控制,并利用ADS软件进行

2017-12-12 07:15:02 2939

2939

本文设计了一种宽频率范围的CMOS锁相环(PLL)电路,通过提高电荷泵电路的电流镜镜像精度和增加开关噪声抵消电路,有效地改善了传统电路中由于电流失配、电荷共享、时钟馈通等导致的相位偏差问题。 设计了

2017-11-18 09:52:14 10

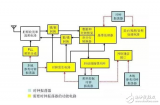

10 作为一种间接频率合成方法,锁相环应用非常广泛,包括存储器、微处理器、硬盘驱动电路、射频和无线收发器等领域。集成电路的飞速发展使锁相环电路能够以较低的成本集成在芯片内部。片上集成锁相环可以根据一个低频

2017-11-07 10:33:22 6

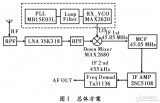

6 讲解之前先讲下锁相环电路,由于调频电路中很多地方用到锁相环电路,因而这个基础必须打坚实了。

2017-09-22 10:44:04 6

6 锁相环是电路功能中最通用的。它们用于时钟处理器(相当良性的情况),以及在固定和调谐频率发射机和接收机建立调谐。

2017-05-16 10:42:41 8

8 结合了MEMS和高分辨率锁相环电路的DCXO,能支持最小量化噪声设计的高速数字锁相环路和不受频率牵引范围影响的相位噪声,适合于应用到各种射频和通信系统中。

2017-04-27 10:35:59 2471

2471

电子芯片手册,很好的资料,设计师必备资料。

2016-05-30 16:32:11 43

43 有关锁相环的部分资料,对制作锁相环有一定的帮助。

2015-10-29 14:16:55 62

62 2015-08-12 13:58:08 29

29 2015-08-10 18:14:16 9

9 2015-04-23 15:20:36 11

11 在传统LC压控振荡器基础上,通过采用二次谐波滤波技术降低了振荡器的相位噪声,并完成了电路的仿真。仿真结果表明,该压控振荡器的振荡频率在1.9~2.1 GHz,其频率调节范围达到

2012-01-13 15:28:55 159

159 锁相环英文为PLL,即PLL锁相环。可以分为模拟锁相环和数字锁相环。两种分类的锁相环原理有较大区别,通过不同的锁相环电路实现不同的功能。

2011-10-26 12:40:28

频率跟踪的 锁相环电路 由专用锁相芯片CD4046和分频芯片CD4040组成,以实现工频信号的锁相倍频,分频比为1/64。在工频信号恰好为50 Hz的情况下,该电路的锁相倍频频率为5064=3 200 Hz,相

2011-10-26 11:17:47 8375

8375

电荷泵锁相环的锁定指示电路设计,常用的方法是在PFD 电路中通过检测经分频后的参考输入和本振反馈信 号的相位误差来实现,当相位误差超过某个锁定检测窗口时,锁相环电路就上报失锁告警。由于数字锁定指示电路 设计简单,易于被监控而被广泛应用。在实际的

2011-03-16 10:20:51 58

58 本文涉及的锁相环路是基于相位控制的时钟恢复系统。目的是用锁相环电路-PLL和DLL实现USB2.0收发器宏单远UTM的时钟恢复木块。其中PLL环路构成的时钟发生器奖外部晶振的12MHZ的正弦信号

2011-03-03 14:58:34 50

50 D3361调频立体声解码电路,采用锁相环方式解码,它比D3301解码电路多了一个锁相环电路,因此性能较D3301优越.主要

2010-10-11 13:10:13 2022

2022

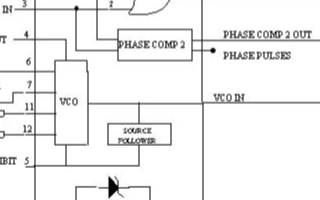

锁相环的英文全称是Phase-Locked Loop,简称PLL。它是由鉴相器(PD)、环路滤波器(LPF)和压控振荡器(VCO)三部分构成的一种信号相差自动调节反馈电路(环)。PLL电路框图如下,其

2010-09-07 16:33:52 662

662 MC44802A是莫托洛拉采用MOSAIC工艺制成的调谐电路的锁相环芯片。它和压控振荡器MC1648连接可组成调谐电路,其调谐频率可由微控制器MC68HCllE9的串行接口控制。本文叙述用MC44802A组成的

2010-05-30 09:54:54 42

42 Signet ic畦}司生产的集成块SE567/NE567,是具有同步调幅锁定捡测和功率输出性能的高稳定性锁相环电路 它的主要功能是一旦输入信号的额率在它检测范周时能驱动负载 它的带宽 中心

2010-04-26 10:44:09 69

69 LM567及NE567原理及应用

音频解码器567功能概述 本文讨论锁相环电路

2010-04-14 09:23:26 19131

19131

SC9256是一个数字调谐系统锁相环电路,内置2个预分频系数。SC9256的所有功能都是通过3根串行总线控制,适用于高性能的数字调谐系统。主要特点* 优化高保真调谐器

2010-02-25 09:23:56 47

47 SC9257是一个数字调谐系统锁相环电路,内置2个预分频系数。SC9257是一个用于数字调谐系统的PLL频率合成器。适用于高性能的数字调谐系统,例如:收音机和随身听。它可

2010-02-25 09:20:12 38

38 本文讨论锁相环电路,介绍NE567单片音调解码器集成电路。此音调解码块包含一个稳定的锁相环路和一个晶体管开关,当在此集成块的输入端加上所先定的音频时,即可产生一个接地

2009-11-23 15:03:42 22

22 时钟和低功耗模式片内集成有PLL(锁相环)电路。外接的基准晶体+PLL(锁相环)电路共同组成系统时钟电路。有关引脚:XTAL1/CLKIN:外接的基准晶体到片内振荡器输入引脚

2009-09-16 12:37:52 12

12 The CD4046BC micropower phase-locked loop (PLL) consistsof a low power, linear, voltage-controlled oscillator(VCO), a source follower, a zener diode, and two phasecomparators. The two phase comparators have a commonsigna

2009-08-08 10:00:01 132

132 锁相环电路的设计:

2009-07-25 17:05:36 536

536 This application note is intended as a guide to designing a phaselocked loop based on the Philips UMA1014T frequency synthesizerintegrated circuit. The UMA1014T is a low power single chip solutionto frequency synthesis in the r

2009-06-30 10:53:58 45

45 本文主要设计了基于相位控制技术的时钟恢复系统的PLL 锁相环路。分别对各单元电路结构——鉴频鉴相器、电荷泵、环路滤波器、压控振荡器、分频器进行设计。采用2.5V,0.25μm

2009-06-01 15:51:53 53

53 本文提出了一种基于锁相技术的组合式三相逆变器控制策略,详细分析了锁相技术的基本工作原理及锁相控制策略,并给出了锁相环电路的关键参数设计及实验验证。通过仅远程采

2009-04-08 15:08:23 38

38

常用锁相环电路集成电路

2006-06-30 19:20:57 606

606 BA1404对于一般的调频发射已经够了,但它却有一个致命的缺点:没有锁相环电路,即PLL,容易跑频!对

2006-04-15 20:46:26 5414

5414

电子发烧友App

电子发烧友App

硬声App

硬声App

386

386 739

739

2293

2293

1222

1222 1609

1609

3409

3409

15

15 2743

2743

3

3 2674

2674

5875

5875

2630

2630

2892

2892

69

69 1835

1835

2939

2939

10

10 6

6 8

8 2471

2471

29

29 9

9 11

11 159

159 8375

8375

58

58 50

50 2022

2022

662

662 42

42 69

69 47

47 38

38 22

22 12

12 132

132 45

45 53

53 38

38

评论