基于FPGA的锁相环位同步提取电路

- fpga(588988)

- 锁相环(86948)

相关推荐

锁相环(PLL)基本原理 当锁相环无法锁定时该怎么处理的呢?

锁相环(PLL)基本原理 当锁相环无法锁定时该怎么处理的呢? 锁相环(Phase Locked Loop, PLL)是一种电路系统,它可以将输入信号的相位锁定到参考信号的相位。在锁相环中,反馈回路

2023-10-23 10:10:15 47

47

47

47软件锁相环在频率突变时锁不住 锁相环无法锁定怎么办?

软件锁相环在频率突变时锁不住 锁相环无法锁定怎么办? 锁相环(PLL)是一种用于在电路中生成稳定频率的技术。它是在1960年代开发的,并被广泛应用于通信、雷达、卫星技术等领域中。锁相环的主要作用

2023-10-13 17:39:58 97

97

97

97什么是锁相环?PLL和DLL都是锁相环区别在哪里?

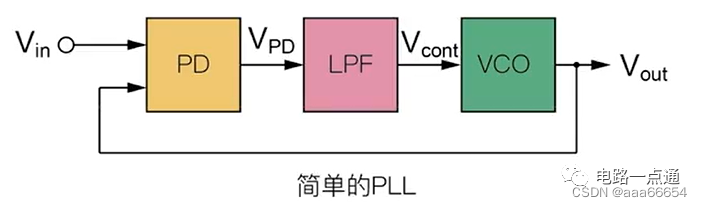

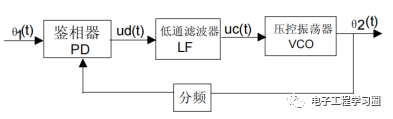

比较,通过不断调整内部振荡器的频率,使得输出信号的相位与参考信号的相位保持一致,从而实现同步。锁相环广泛应用于数字通信、音频解码、数字信号处理等领域。 在锁相环的基本结构中,包含一个相位检测器、一个积分环节、一个低通滤波器和一个控制振荡器。参考

2023-10-13 17:39:53 106

106

106

106pll锁相环的作用 pll锁相环的三种配置模式

pll锁相环的作用 pll锁相环的三种配置模式 PLL锁相环是现代电子技术中广泛应用的一种电路,它的作用是将一个特定频率的输入信号转换为固定频率的输出信号。PLL锁相环的三种配置模式分别为

2023-10-13 17:39:48 167

167

167

167数字锁相环设计源程序

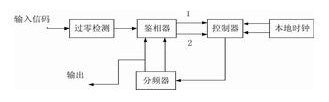

数字锁相环设计源程序PLL是数字锁相环设计源程序, 其中, Fi是输入频率(接收数据), Fo(Q5)是本地输出频率.目的是从输入数据中提取时钟信号(Q5), 其频率与数据速率一致, 时钟上升沿锁定在数据的上升和下降沿上;顶层文件是PLL.GDF

2009-12-18 10:37:37

锁相环是如何实现倍频的?

锁相环是如何实现倍频的? 锁相环(Phase Locked Loop, PLL)是一种电路,用于稳定和恢复输入信号的相位和频率。它可以广泛应用于通信、计算机、音频等领域中。其中一个重要的应用就是

2023-09-02 14:59:37 386

386

386

386pll锁相环倍频的原理

以及各种时钟信号,下面将从这些方面逐一介绍。 一、锁相环 锁相环(Phase-Locked Loop, PLL)是一种基于反馈控制的电路,由比较器、低通滤波器、振荡器和除法器等组成。输入信号和振荡器产生的参考信号经过比较器比较,将误差信号通过低通滤波器进

2023-09-02 14:59:24 444

444

444

444什么是锁相环 锁相环的组成 锁相环选型原则有哪些呢?

大家都知道锁相环很重要,它是基石,锁相环决定了收发系统的基础指标,那么如此重要的锁相环选型原则有哪些呢?

2023-08-01 09:37:05 672

672

672

672

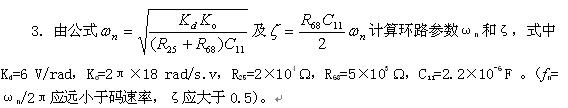

锁相环设计与仿真的基本知识

锁相环:在通信领域中,锁相环是一种利用反馈控制原理实现的频率及相位同步技术,其作用是将电路输出的时钟与其外部的参考时钟保持同步。

2023-06-30 15:53:39 1199

1199

1199

1199

模拟锁相环和数字锁相环区别

模拟锁相环和数字锁相环的主要区别在于它们的控制方式不同。模拟锁相环是通过模拟电路来控制频率和相位,而数字锁相环是通过数字信号处理技术来控制频率和相位。此外,模拟锁相环的精度较低,而数字锁相环的精度较高。

2023-02-15 13:47:53 2765

2765

2765

2765锁相环PLL的基础知识

锁相环 (PLL) 电路存在于各种高频应用中,从简单的时钟清理电路到用于高性能无线电通信链路的本振 (LO),再到矢量网络分析仪 (VNA) 中的超快速开关频率合成器。本文解释了锁相环电路的一些构建模块,并参考了每种应用,以帮助指导新手和锁相环专家导航器件选择以及每种不同应用固有的权衡取舍。

2022-12-23 14:03:54 2293

2293

2293

2293

锁相环的基本组成和工作原理

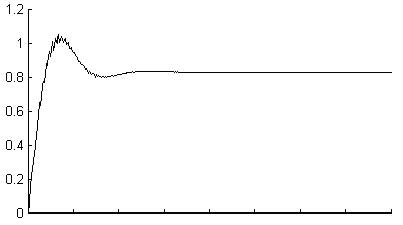

因锁相环可以实现输出信号频率对输入信号频率的自动跟踪,所以锁相环通常用于闭环跟踪电路。锁相环在工作的过程中,当输出信号的频率与输入信号的频率相等时,输出电压与输入电压保持固定的相位差值,即输出电压与输入电压的相位被锁住,这就是锁相环名称的由来。

2022-05-10 14:25:19 6544

6544

6544

6544锁相环(PLL)的工作原理及应用

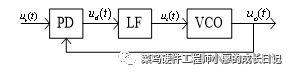

锁相环路是一种反馈控制电路,简称锁相环(PLL,Phase-Locked Loop)。锁相环的特点是:利用外部输入的参考信号控制环路内部振荡信号的频率和相位。

2022-03-29 09:54:55 10729

10729

10729

10729MCU锁相环简述(一)

)控制原理实现的频率及相位的同步技术,其作用是将电路输出的时钟与其外部的参考时钟保持同步。当参考时钟的频率或相位发生改变时,锁相环会检测到这种变化,并且通过其内部的反馈系统来调节输出频率,直到两者

2021-11-01 16:24:35 12

12

12

12锁相环CD4046原理及应用

锁相的意义是相位同步的自动控制,能够完成两个电信号相位同步的自动控制闭环系统叫做锁相环,简称PLL。它广泛应用于广播通信、频率合成、自动控制及时钟同步等技术领域。锁相环主要由相位比较器(PC)、压控振荡器(VCO)、低通滤波器三部分组成。

2021-06-21 15:13:55 56

56

56

56如何使用FPGA实现高性能全数字锁相环的设计

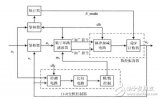

本文提出了一种适用范围广泛的全数字锁相环(ADPLL)实现方法.在锁相环输入频率未知的情况下,实现锁相锁频功能。本文从全数字锁相环的基本实现方式入手.进行改进,并使用VH DL语言建模,使用FPGA进行验证。

2021-01-26 15:03:00 65

65

65

65如何使用FPGA实现高性能全数字锁相环的设计

本文提出了一种适用范围广泛的全数字锁相环(ADPLL)实现方法.在锁相环输入频率未知的情况下,实现锁相锁频功能。本文从全数字锁相环的基本实现方式入手.进行改进,并使用VH DL语言建模,使用FPGA进行验证。

2021-01-26 15:03:00 18

18

18

18锁相环的基本组成及工作原理

因锁相环可以实现输出信号频率对输入信号频率的自动跟踪,所以锁相环通常用于闭环跟踪电路。锁相环在工作的过程中,当输出信号的频率与输入信号的频率相等时,输出电压与输入电压保持固定的相位差值,即输出电压与输入电压的相位被锁住,这就是锁相环名称的由来。

2020-11-03 14:55:49 14026

14026

14026

14026

使用FPGA实现数字锁相环的设计资料说明

锁相环路是一种反馈控制电路,简称锁相环( PLL)。锁相环的特点是:利用外部输入的参考信号控制环路内部振荡信号的频率和相位。因锁相环可以实现输出信号频率对输入信号频率的自动跟踪, 所以锁相环通常

2020-08-06 17:58:25 24

24

24

24正点原子开拓者FPGA视频:PLL锁相环实验

锁相环路是一种反馈控制电路,简称锁相环(PLL,Phase-Locked Loop)。锁相环的特点是:利用外部输入的参考信号控制环路内部振荡信号的频率和相位。因锁相环可以实现输出信号频率对输入信号频率的自动跟踪,所以锁相环通常用于闭环跟踪电路。

2019-09-20 07:05:00 3335

3335

3335

3335

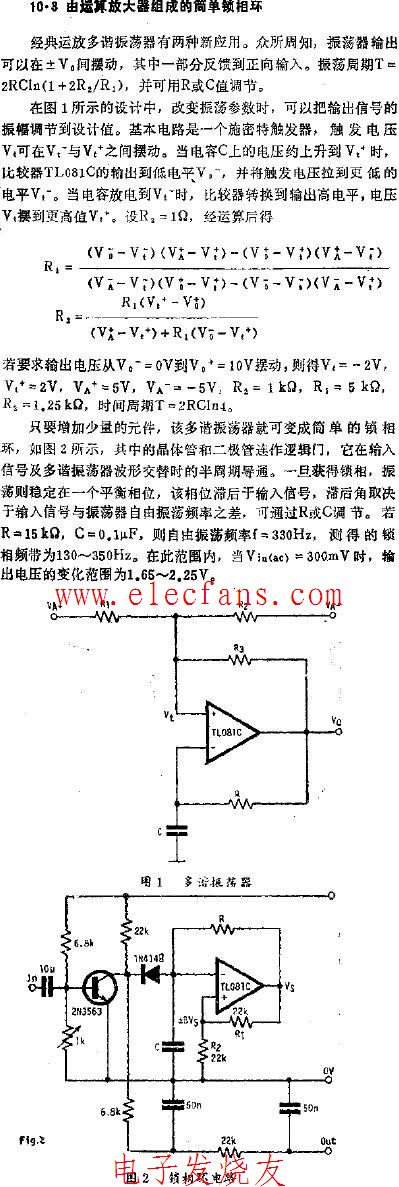

基于FPGA实现电路的同步提取性能设计

一般的位同步电路大多采用标准逻辑器件按传统数字系统设计方法构成,具有功耗大,可靠性低的缺点。用FPGA设计电路具有很高的灵活性和可靠性,可以提高集成度和设计速度,增强系统的整体性能。本文给出了一种基于fpga的数字锁相环位同步提取电路。

2019-04-19 08:24:00 2893

2893

2893

2893

用FPGA设计一阶全数字锁相环的方法

的问题进行了讨论。 引言 锁相环(PLL)技术在众多领域得到了广泛的应用。如信号处理,调制解调,时钟同步,倍频,频率综合等都应用到了锁相环技术。传统的锁相环由模拟电路实现,而全数字锁相环(DPLL)与传统的模拟电路实现的PLL相比,具有精度高

2018-10-25 09:17:13 7963

7963

7963

7963锁相环在调制和解调中的应用及概念解析

许多电子设备要正常工作,通常需要外部的输入信号与内部的振荡信号同步,利用锁相环路就可以实现这个目的。锁相环路是一种反馈控制电路,简称锁相环(PLL)。锁相环的特点是:利用外部输入的参考信号控制环路内部振荡信号的频率和相位。

2018-01-22 11:18:45 12994

12994

12994

12994

锁相环CD4046的应用设计分析

于各种各样的反馈控制系统中,例如,锁相频率合成;利用它的调制跟踪和载波跟踪特性,可以把它用于调制、解调、锁相接收、载波恢 复、位同步提取等[1- 3];利用锁相环的窄带滤波特性,可以把淹没在噪声中的信号提取出来,所以可以把它用于

2017-10-27 17:09:20 13

13

13

13详解FPGA数字锁相环平台

一、设计目标 基于锁相环的理论,以载波恢复环为依托搭建数字锁相环平台,并在FPGA中实现锁相环的基本功能。 在FPGA中实现锁相环的自动增益控制,锁定检测,锁定时间、失锁时间的统计计算,多普勒频偏

2017-10-16 11:36:45 18

18

18

18锁相环的作用是什么_锁相环的主要作用_什么是锁相环

锁相环是指一种电路或者模块,它用于在通信的接收机中,其作用是对接收到的信号进行处理,并从其中提取某个时钟的相位信息。或者说,对于接收到的信号,仿制一个时钟信号,使得这两个信号从某种角度来看是同步的(或者说,相干的)。

2017-07-27 10:01:51 31833

31833

31833

31833

多速率锁相环相位同步方法的研究

用常规锁相环技术可以很地的实现扰动较小条件下的交流电网的实时相位同步。为了克服当电网频率出现较大的波动而且具有凹陷型扰动时常规锁相环的相位同步误差,本文提出了一种

2011-12-28 16:17:14 27

27

27

27扩频通信的数字锁相环设计

针对扩频通信系统的载波同步,提出一套完善的数字锁相环设计方案. 该方案利用新颖的可控根法完成1~3阶模拟锁相环(APLL)环路参数设计,并实现从模拟域到数字域的转换,得到的数字锁相

2011-08-26 16:10:38 122

122

122

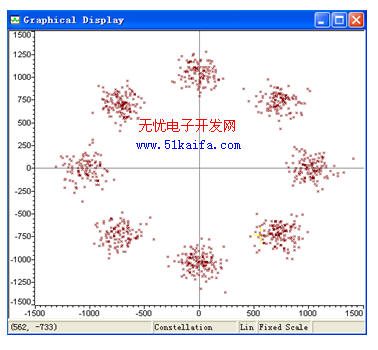

122基于CORDIC算法的载波同步锁相环设计

研究了一种利用CORDIC算法的矢量及旋转模式对载波同步中相位偏移进行估计并校正的方法。设计并实现了基于CORDIC算法的数字锁相环。通过仿真,验证了设计的有效性和高效性。

2010-12-15 14:49:43 36

36

36

36基于FPGA的自适应锁相环设计

利用锁相环进行载波跟踪是获取本地载波的一种重要方法,针对锁相环的噪声性能和跟踪速度不能同时达到最优的限制,在锁相环PLL中引入自适应模块,根据环路所处

2010-11-25 17:19:33 29

29

29

29一种基于FPGA实现的全数字锁相环

锁相环被广泛应用于电力系统的测量和控制中。介绍了一种新型的基于比例积分控制逻辑的全数字锁相环。通过对其数学模型的分析,阐述了该锁相环的各项性能指标与设计参数的

2010-07-02 16:54:10 29

29

29

29模拟锁相环,模拟锁相环原理解析

模拟锁相环,模拟锁相环原理解析

背景知识:

锁相技术是一种相位负反馈控制技术,它利用环路的反馈原理来产生新的频率点。它的主要

2010-03-23 15:08:20 5716

5716

5716

5716数字锁相环(DPLL),数字锁相环(DPLL)是什么?

数字锁相环(DPLL),数字锁相环(DPLL)是什么?

背景知识:

随着数字电路技术的发展,数字锁相环在调制解调、频率合成、FM 立体声解码、彩色副

2010-03-23 15:06:21 5312

5312

5312

5312宽频带数字锁相环的设计及基于FPGA的实现

宽频带数字锁相环的设计及基于FPGA的实现数字锁相环(DPLL)技术在数字通信、无线电电子学等众多领域得到了极为广泛的应用。与传统的模拟电路实现的

2009-11-23 21:00:58 1101

1101

1101

1101

智能全数字锁相环的设计

智能全数字锁相环的设计:在FPGA片内实现全数字锁相环用途极广。本文在集成数字锁相环74297的基础上进行改进,设计了锁相状态检测电路,配合CPU对环路滤波参数进行动态智能配

2009-06-25 23:32:57 70

70

70

70智能全数字锁相环的设计

摘要: 在FPGA片内实现全数字锁相环用途极广。本文在集成数字锁相环74297的基础上进行改进,设计了锁相状态检测电路,配合CPU对环路滤波参数进行动态智

2009-06-20 12:39:32 1313

1313

1313

1313

基于DSP的高阶COSTAS锁相环的设计

基于DSP的高阶COSTAS锁相环的设计

COSTAS环是一种闭环自适应系统,用于提取相干载波。本文主要介绍了一种用于载波同步的高阶COSTAS环路,用于完成MPSK的相干解调中的载

2009-05-25 18:15:36 1110

1110

1110

1110

模拟锁相环应用实验

一、实验目的1、掌握模拟锁相环的组成及工作原理。2、学习用集成锁相环构成锁相解调电路。3、学习用集成锁相环构成锁相倍频电路。

二、锁相环路的基本原理

2009-03-22 11:44:37 124

124

124

124锁相环CD4046应用

锁相环CD4046应用

锁相的意义是相位同步的自动控制,能够完成两个电信号相位同步的自动控制闭环系统叫做锁相环,简称PLL。它广泛应用于广播通信、

2009-03-18 15:11:18 1965

1965

1965

1965

锁相环的研究和频率合成

锁相环的研究和频率合成一、实验目的:1. 振荡器(VCO)的V—f 特性的研究2. 对称波锁相环基本特性的研究3. 利用锁相环实现频率合成二、锁相环原理:

2009-03-06 20:02:52 1771

1771

1771

1771

应用于锁相环的脉宽调整电路的设计

应用于锁相环的脉宽调整电路的设计

前言

在锁相环PLL、DLL和时钟数据恢复电路CDR等电路的应用中,人们普遍要求输出时钟信号有50%的占空比,以便在时钟上升及下

2008-10-16 08:59:42 967

967

967

967

软件锁相环的设计与应用

根据虚拟无线电技术的特点和锁相环的基本原理,提出一种适于计算机软件化实现的锁相环数学模型,分析不同参数对锁相环捕获和跟踪性能的影响,得出不同情况下参数设定的基

2008-08-15 12:36:19 98

98

98

98锁相环原理

锁相环原理

锁相环路是一种反馈电路,锁相环的英文全称是Phase-Locked Loop,简称PLL。其作用是使得电路上的时钟和某一外部时钟的相位同步。因锁相环可以

2007-08-21 14:46:04 4689

4689

4689

4689 电子发烧友App

电子发烧友App

评论