【原书名】 High-Speed Digital System Design: A Handbook of Interconnect Theory and Design Practices [原书信息]

【原出版社】 John Wiley & Sons,Inc.

【作者】 (美)Stephen H.Hall,Garrett W.Hall, James A.McCall

【译者】 伍微等

【丛书名】 电子与电气工程丛书

【出版社】 机械工业出版社

【书号】 7-111-16822-4

【开本】 16开 【页码】 252

【出版日期】 2005-8-1 【版次】 1-1

市场价: ¥33.00

《高速数字系统设计:互连理论和设计实践手册》

数字系统设计员必须面对当今微处理器运行速度不断增加所带来的挑战,因此,理解高速互连现象是不可或缺的。本书基于硬件平台,将从基本的传输线理论到数字时序分析,再到高速测量技术等概念,逐一为读者进行高速数字系统设计说明并将通俗易懂的原理解释与大量实用问题解决方案结合起来,为当前的数字系统设计技术提供实践指导。本书由3位Intel高级工程师编写,详细解释常被忽略的有关数字总线上高频效应的主题,介绍多种成熟技术和应用实例。

本书特点

●从数字角度详细介绍基本传输线理论。

●理论层面的理解有助于读者摆脱当前实践应用的局限,进而能够解决本书中未涉及的问题。

●书中理论适用于任何高速数字系统。

●书中涵盖的所有方法都已经应用于实际数字产品,且这些产品的大批量生产和销售已经获得成功。

http://www.china-pub.com/computers/common/info.asp?id=26449

中国PCB论坛网斑竹winworm评价:

首先肯定一下,高速数字系统设计中的时序设计章节是所有高速数字设计书籍中讲得最清楚的,尽管Howard在书中也讲到了时序,但没有这本书中讲得好。

但是,我觉得时序设计可以简化,没有必要搞这么复杂,很多时候,尽管已经理解了,时序公式还是记不住,尤其是哪个量应该加,哪个量应该减,而且时序系统不止文中所说的2种类型,还有其它的一些变型,关键是要把握好时序设计的基本点,抓住建立时间和保持时间,剩下的事情都好办。

时序设计应该有一个好的设计工具,而不是靠一个简单的时序计算表。

本书目录:

第1章互连设计的重要性1

1?1基础1

1?2过去和未来3

第2章理想传输线基本原理5

2?1PCB或MCM上的传输线结构5

2?2波的传播6

2?3传输线参数6

2?3?1特征阻抗7

2?3?2传播速度、时间和距离9

2?3?3SPICE仿真中的等效电路模型10

2?4发送初始波和传输线反射12

2?4?1初始电波12

2?4?2多次反射14

2?4?3上升时间对反射的影响20

2?4?4电抗性负载的反射21

2?4?5消除反射的匹配方案22

2?5补充示例25

2?5?1问题25

2?5?2目标25

2?5?3计算PCB的横截面几何结构25

2?5?4计算传输延迟26

2?5?5确定接收端波形27

2?5?6创建等效电路27

第3章串扰29

3?1互感和互容29

3?2电感矩阵和电容矩阵29

3?3场仿真器30

3?4串扰感应噪声31

3?5用等效电路模型仿真串扰35

3?6串扰感应延迟时间和信号完整性变化36

3?6?1开关模式对传输线性能的影响36

3?6?2使用单线等效模型模拟多导线系统中的走线40

3?7串扰引起的阻抗变化41

3?8奇、偶模传输线对的匹配43

3?8?1Pi型匹配网络44

3?8?2T型匹配网络45

3?9串扰最小化设计45

3?10补充示例46

3?10?1问题46

3?10?2目标47

3?10?3计算串扰引起的阻抗变化和传播速度变化的最大值47

3?10?4判断串扰是否会导致误触发48

第4章非理想互连问题51

4?1传输线损耗51

4?1?1导线直流损耗51

4?1?2介质直流损耗52

4?1?3趋肤效应52

4?1?4与频率相关的介电损耗60

4?2介电常数的变化62

4?3走线弯曲63

4?4符号间干扰65

4?590°转角效应67

4?6拓扑效应68

第5章连接器、封装和过孔71

5?1过孔71

5?2连接器72

5?2?1串联电感73

5?2?2并联电容73

5?2?3连接器串扰73

5?2?4电感耦合引起的连接器引脚场效应74

5?2?5EMI76

5?2?6连接器设计指南76

5?3芯片封装78

5?3?1常见的封装类型78

5?3?2创建封装模型81

5?3?3封装的影响84

5?3?4最佳引脚布局88

第6章非理想回路、同步开关噪声和功率传输91

6?1非理想电流回路91

6?1?1最小电感通路91

6?1?2信号通过地槽92

6?1?3切换参考面的信号94

6?1?4以电源或地为参考面的信号95

6?1?5其他非理想回路98

6?1?6差分信号98

6?2本地功率传输网络99

6?2?1高速I/O设计中求解本地去耦需求100

6?2?2系统级功率传输102

6?2?3选择去耦电容104

6?2?4功率传输系统的频率响应105

6?3SSO/SSN105

第7章缓冲器建模109

7?1模型分类109

7?2基本的CMOS输出缓冲器110

7?2?1基本操作110

7?2?2为CMOS缓冲器建立线性模型114

7?2?3为CMOS缓冲器建立行为模型119

7?3在饱和区中工作的输出缓冲器121

7?4小结122

第8章数字时序分析123

8?1公用时钟时序123

8?2源同步时序127

8?2?1源同步时序方程128

8?2?2根据眼图推导源同步时序方程131

8?2?3其他源同步方案131

8?3其他总线信号传输技术132

8?3?1时钟伴随133

8?3?2时钟嵌入133

第9章设计方法学135

9?1时序135

9?1?1最差情况时序表136

9?1?2统计时序表138

9?2时序度量、信号质量度量和测试负载140

9?2?1参考电压的不确定度140

9?2?2对参考负载进行仿真140

9?2?3延迟时间143

9?2?4延迟时间偏差144

9?2?5信号完整性145

9?3设计优化147

9?3?1图纸分析147

9?3?2制板分析148

9?4灵敏度分析149

9?4?1初步的趋势分析和显著性分析150

9?4?2有序参数扫描154

9?4?3解空间求解的第1阶段155

9?4?4解空间求解的第2阶段157

9?4?5解空间求解的第3阶段159

9?5设计指南159

9?6参数提取160

9?7在设计系统时应遵循的通用经验方法160

第10章辐射规范和系统噪声最小化163

10?1FCC辐射规范163

10?2辐射的物理原理164

10?2?1差模辐射164

10?2?2共模辐射168

10?2?3波阻抗171

10?3去耦与扼流172

10?3?1系统级高频去耦173

10?3?2扼流电缆、本地电源平面和本地地平面176

10?3?3低频去耦与地平面隔离182

10?4补充的PCB设计准则、封装须知与引脚布局183

10?4?1高速器件和高速走线的布局183

10?4?2串扰183

10?4?3引脚布局和封装选择184

10?5机箱设计184

10?5?1电磁屏蔽基本知识184

10?5?2孔径186

10?5?3谐振189

10?6时钟频谱扩展190

第11章高速测量技术193

11?1数字示波器193

11?1?1带宽193

11?1?2采样194

11?1?3其他效应196

11?1?4统计197

11?2时域反射计197

11?2?1TDR理论198

11?2?2测量要素199

11?3TDR的精度201

11?3?1入射寄生效应202

11?3?2探针类型203

11?3?3反射204

11?3?4接口传输损耗204

11?3?5电缆损耗204

11?3?6幅度漂移误差205

11?4阻抗测量205

11?4?1阻抗的精确测量205

11?4?2TDR阻抗分析中的测量区域206

11?5奇模阻抗和偶模阻抗207

11?6串扰噪声208

11?7传播速度208

11?7?1长度差分法209

11?7?2Y截距法209

11?7?3TDT法209

11?8矢量网络分析仪210

11?8?1S参数简介211

11?8?2仪器211

11?8?3单端口测量(Zo、L、C)212

11?8?4双端口测量(Td、衰减、串扰)214

11?8?5校准217

11?8?6单端口测量校准218

11?8?7双端口测量校准218

11?8?8校准验证219

附录A阻抗公式的其他特性221

附录BGTL电流模式分析223

附录C数字信号的频域分量229

附录D有用的S参数变换231

附录E分贝的定义235

附录FFCC辐射限制237

参考书目239

索引241

- 高速数字(8300)

- 实践手册(5850)

相关推荐

高速数字系统设计——互连理论和设计实践手册

0

0RA6快速设计指南 [完结] 一般布线实践 (下)高速信号设计注意事项

655

655探索开源创新理论|2023开放原子全球开源峰会开源创新理论与实践分论坛成功召开

472

472探索开源创新理论|2023 开放原子全球开源峰会开源创新理论与实践分论坛成功召开

300

300

展望开源产业与数字经济未来|2023 开放原子全球开源峰会开源创新理论与实践分论坛即将启幕

189

189

展望开源产业与数字经济未来|2023开放原子全球开源峰会开源创新理论与实践分论坛即将启幕

204

204

如何区分高速信号和低速信号

4587

4587高速PCB布线实践指南介绍

11

112020年大连理工大学《单片机原理及应用》期末试卷

31

31高速数字电路设计中的信号反射抑制综述

15

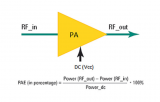

15解读放大器负载对PAE的影响-从理论到实践

2377

2377

高速数字系统设计互连理论和设计实践手册PDF电子书免费下载

49

49高速电路设计实践的电子教材免费下载

85

85高速PCB设计中高速信号与高速PCB设计须知

9850

9850

高速电路设计实践PDF电子教材免费下载

185

185高数据速率数字互连解决方案面向高速背板应用

2891

2891变频器的故障分析和解决 实践检验、理论知识及维修水平

3709

3709

高速电路设计实践PDF电子书免费下载

373

373探讨高速信号完整性理论和PCB仿真设计

1215

1215

学好电子技术关键是理论知识和实践动手能力

6525

6525高速电路信号完整性分析与设计—高速信号完整性的基本理论

1536

1536现代通信的理论与实践_吉家骝

95

95高速数字设计_英文版

130

130高速数字系统的互连完整性和散热问题

843

843

高速数字设计_沈立译

52

52应用于光互连的高速误码仪的设计

28

28数字逻辑电路教学实践探讨

60

60高速互连 (第9版本)

20

20基于RapidIO和存储映射的高速互连网络

20

20高速接口互连

19

19高速互连自测试技术的原理与实现

15

15思想政治理论课开展研究性教学的实践探索

7

7高速数字设计

286

286高速PCB互连设计中的测试技术

535

535

电子发烧友App

电子发烧友App

评论