对于高频系统来说,电磁干扰(EMI)是个不小的危害,噪声具有频谱宽、隐蔽性强、难于消除等特点,因此将噪声抑制到最小对提高系统性能指标是必要的。对于抑制噪声、减小EMI,可以通过改进电源方案、降低电源噪声、优化时钟方案、正确产生逻辑信号,以及设计接口电路和信号线连接部分。本文将阐述如何通过上述方案减小高频系统控制电路产生的噪声以提高系统性能。

对于实现10纳秒触发控制电路这一基本功能并不是一件难事,但是对于某些领域,会有一些特殊的要求,要想完全达到指标,对电磁兼容性有很高要求。本文提出的设计应用于对高频电路的控制,可实现对系统无射频干扰,传输距离可达到30米,满足TTL电平要求,最高时钟频率为50MHz。

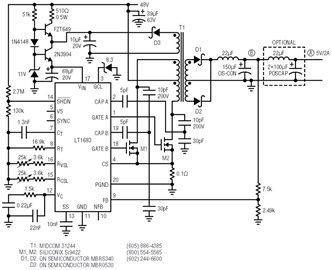

整个电路设计主要分为四部分:电源部分设计(包括底层设计)、时钟部分设计、逻辑部分设计和接口部分设计。对于减小系统噪声,电源的管理是首要的。首先采用高性能DC-DC进行电能的转换,把有纹波输出的直流电源隔离。控制电路中并不是单电源供电的,对于缓冲电路是采用5V供电,对于可编程器件采用3.3V和1.5V供电,因此还需要两个LDO对电压进行变换。

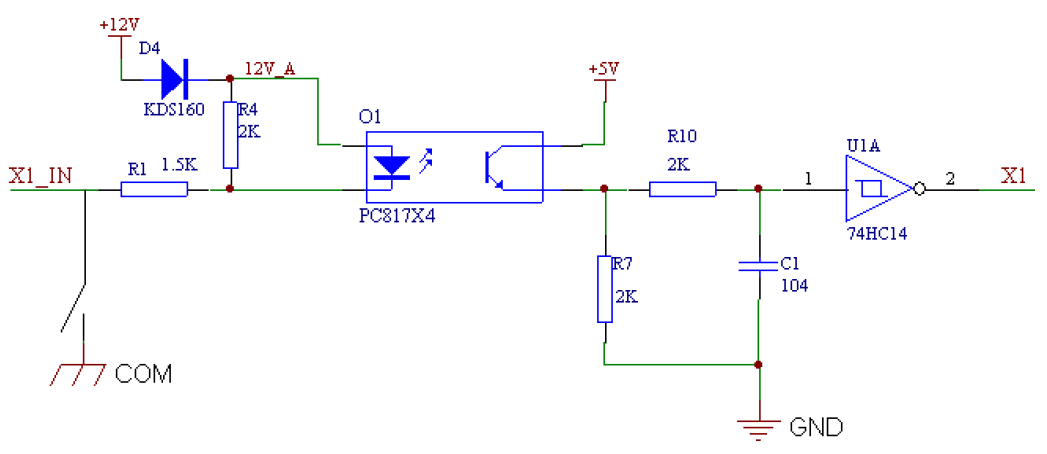

对于外部时钟部分,电路中采用了精度小于30ppm的3.3V晶振,给可编程器件提供时钟源。由于可编程逻辑器件内置锁相环,可以保持与外部时钟的同步,同时还可满足倍频需要,可编程逻辑器件还内置全局时钟总线,可满足逻辑的同步建立。为了驱动外部TTL设备,控制系统采用了可编程逻辑器件和高速CMOS器件进行缓冲,为了实现长距离传输,还需对输出信号进行终端匹配。接口部分指的是接插件,接插件具有较大的引线电感,很容易造成信号传输线的阻抗不匹配,因此需要做好屏蔽才能减少EMI问题。

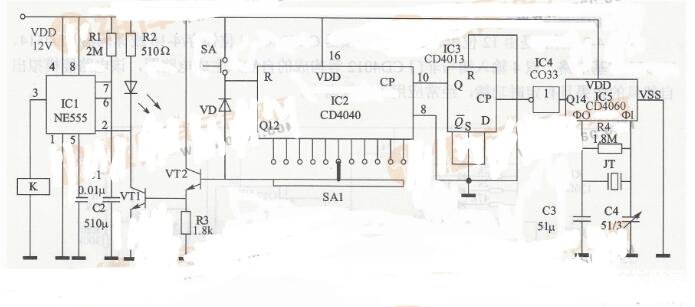

为了提高整体性能和增强抗ESD能力,电路采用四层PCB板设计。四层板的排列为:第一层为元件层和重要信号布线层,第二层为地层,第三层为电源层,第四层为一般信号布线层。第一层紧邻地层,可对信号回路提供最好的耦合,因此应布最重要的信号线,同时为了减小引线电感,顶层器件全部选用表贴器件。第二层为地平面,对地层信号提供最好的耦合回路,同时对电源层提供一定的去耦。第三层电源层只是直流电源走线,为简化设计,并未布置成电源面,对于没有电源线的空白区域,可以布置一些不是很重要的信号线,而且这些信号线要距离电源线较远,不能对电源造成串扰。第四层为信号线层,对于缓冲器后面的线,由于加了终端匹配,上升沿变缓,因此不容易超过电长走线长度,基本在第四层传到控制输出端口。控制整体框图如图1所示。

电路的电源及接地部分设计

1. 电源隔离及电压转换

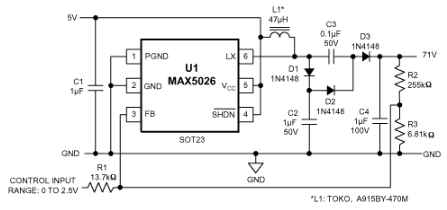

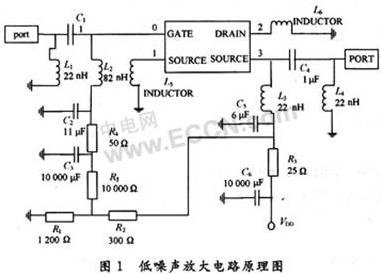

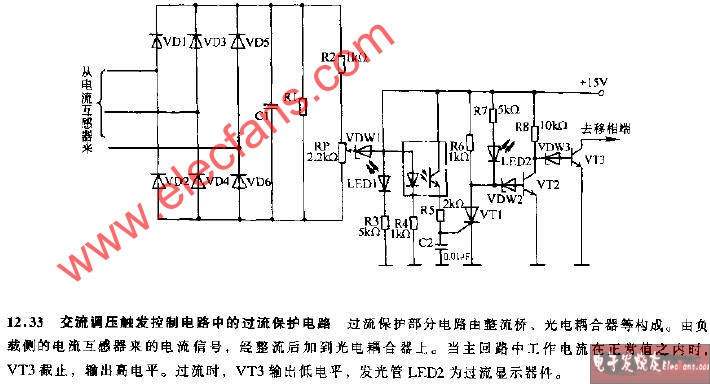

外部直流供电电源采用线性电源供电,纹波较小,但直流噪声仍然可达到50mV,通过DC- DC模块进行能量转换后,噪声可降低到25mV以下,由于DC-DC对高频进行了很好的抑制,因此,电源部分带来的噪声不会串到高频系统中。在DC-DC模块输入端加整流和电容滤波处理,是在DC-DC模块之前对噪声的抑制。DC-DC输出端加稳压处理是为了保证对供电器件的保护,同时加电容对输出的低频部分进一步做滤波处理。在控制系统中,可编程逻辑器件的供电并不是单电压的,还需要DC-DC输出的5V直流通过LDO进行变压,LDO对DC-DC输出的电压中的噪声部分还可进一步抑制,尤其是对高频部分,通过2个LDO,将5V直流电压变到3.3V和1.5V两组输出到可编程器件。DC-DC去耦处理如图2。

2. 接地部分设计

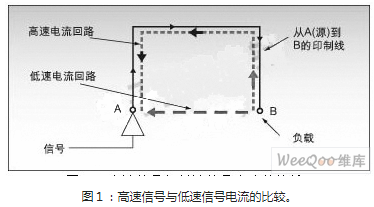

此控制系统采用四层PCB设计,具有完整的地平面,可以对信号提供低阻抗返回路径,因此可以降低信号对外界造成的辐射。对于接地部分,有单点接地和多点接地两种设计。对于1MHz以下的部分采用单点接地,这时分布阻抗的影响较小。对于1MHz或更高频率的电路部分,返回路径的电感会对电路产生作用,产生压降或射频电流,因此高于1MHz的电路部分采用多点接地。多点接地可以减少噪声产生电路与参考面间的电感。

时钟信号线最大走线长度计算

采用有源时钟主要是为可编程逻辑器件提供参考信号,时钟的精度可以直接决定控制电路的性能。本设计中时钟的精度采用30ppm,通过可编程逻辑器件内的锁相环电路,实现对参考时钟的同步。有源时钟由外部直接供电(3.3V),即可输出时钟信号,时钟输出信号升降沿基本为4~6ns,在设计时,时钟信号线的走线长度不应超过电长走线,超过此长度的线叫电气长线,就会产生传输线效应。采用基本公式计算时钟信号单程最长走线的公式为:

L=(tr/2)*VP

VP=

L:在微带线(micro strip line)中电气长线长度;

tr:信号上升沿时间,取4ns;

VP:信号在微带线中传输的速度;

C:光速

ε:元件层与地平面的相对介电常数,通常取4.5。

按上述公式计算的时钟信号在微带线中传输的速度为1.414*108m/s,因此,始终信号线最大走线长度28.3cm。

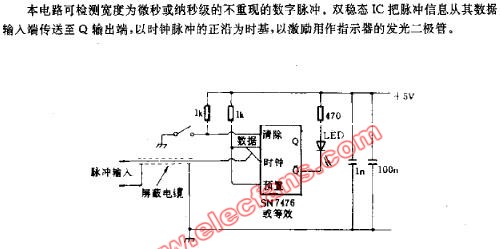

为了保证时钟信号的完整性,在有源时钟电源输入端需要加去耦器件,电路如图3所示,在此电路中,采用0.1uF和0.001uF的π型网络,比单独使用一个0.001uF的电容去耦性能在高频部分改善6dB,见图4。

另外,时钟在进行布线时不应有层间跳变,因为每个通孔会产生1~3nH的电感,这一走线电感可能引起信号完整性问题以及阻抗不匹配和潜在的RF辐射,对高频系统都可能产生负面的影响。

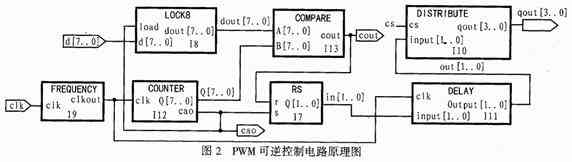

电路的逻辑部分设计

逻辑部分主要包括逻辑输入、逻辑输出、数据缓冲和终端匹配4个部分,逻辑的产生靠可编程逻辑器件来完成,由于产生的是低压逻辑信号,因此需要高速CMOS器件进行缓冲,来驱动控制设备。

1.逻辑输入

对于低电压可编程逻辑器件来说,如果输入信号电平偏高,通常在信号输入端串接一限流电阻,阻值根据具体器件和电压差而定,对于此设计电路来说,输入信号为标准TTL信号,而可编程逻辑器件输入电平最大为3.3V兼容,因此在输入信号与可编程器件之间串接一个100欧姆电阻进行限流,以保证可编程器件的使用安全。

2.逻辑输出

为了保证输出的同步性,在可编程逻辑器件内部,对输出信号做了锁存。同时,可编程逻辑器件内部的布线也是很复杂的,通常器件厂家总是公布对逻辑布线进行了很大的升级、改进,但仍然有很大的提升空间,因此,通过人为的逻辑控制以及内部的布局控制,对于改善信号输出性能会带来一定的改善。这就好比很多PCB厂商,虽然软件本身的自动布线功能一再改善,但多数情况下还是达不到完全理想的性能,还需手工修改进行补偿。

3.数据缓冲

可编程逻辑器件只是实现了逻辑关系的产生,但输出的数据驱动能力和传输距离都受到了很大的限制,因此还需要加数据缓冲来对控制设备的驱动。设计中采用高速CMOS器件进行数据缓冲,具有高扇出电流、高速、功耗低等特点,但此控制电路控制信号传输距离为30米,以此需要将TTL转为差分控制,接收端在将差分信号转为TTL信号,即可实现高速远距离的控制。

4.终端匹配

对于差分传输,1M频率的信号通常可传输90米作用,但为了保证信号的完整性,通常在差分接收端加120欧姆平衡电阻,同时在信号线上串接一匹配电阻。本设计根据实际需要选用51欧姆匹配电阻,不同的情况需要做调整。

电路的接口部分设计

电路的接口部分采用DB型插头进行差分信号的传输,差分信号在传输时不容易辐射干扰,但由于阻抗不匹配造成的干扰还是可能产生误码的。插头采用弯针焊接到PCB上,弯针和焊接孔将会产生一定的电感,造成传输路径的不匹配,由于阻抗不匹配造成信号在接插件处反射,对后面一级控制系统产生EMI。将接插头的外壳接到数字地,在接到系统地的低阻抗回路就会对接插头处的反射噪声信号提供一个低阻抗回路,从而减小对下一级电路的影响。当然,主要的消除措施是在接收端加终端匹配。

本文小结

本文介绍的设计方案具有很高的控制信号转换速度,较长的通讯距离,会对高频系统产生很小的EMI。控制电路采用四层PCB和较优化的布局,还提高了抗ESD能力。在电源部分采用了DC-DC隔离和LDO器件对可编程逻辑进行分压处理。DC-DC是能量转换器件,可以对输入噪声做很好的隔离,本身产生的噪声也低于25mV,LDO器件可除稳压输出外,还可以对噪声进行抑制。采用高精度晶振和数组锁相环时钟控制可以提高系统精度和可靠性,还可以对外部时钟进行倍频处理。逻辑产生部分,采用高速CMOS器件进行缓冲并采用差分形式将信号进行转换,既提高了转换速度又增加了控制距离。由于接插件部分给传输带来的阻抗不匹配,因此接插件做接地处理,给噪声提供低阻抗返回路径,同时在接收端加匹配措施,避免了干扰信号传到下一级系统中。

高频噪声会对高频系统信号产生干扰甚至交调到高频系统中,因此对于本设计,对噪声抑制和提高EMC做了很好的改善,如晶振的电路设计中,采用0.1uF和0.001uF的π型电容网络使噪声抑制得到6dB的改善,但这种改善只有在高频部分才会有效,在低频部分和使用0.001uF的电容进行去耦效果几乎是一样的。

- 电路设计(188365)

- 可减少高(5378)

相关推荐

彩灯控制电路设计原理课程设计

低噪声APD偏置电路

1086

1086

通过超低噪声48V至5V、10W DC/DC转换器降低EMI

590

590

构建具有纳伏灵敏度的低噪声仪表放大器

369

369

#电路设计 低噪声 μModule DC-DC 转换器简化了 EMI 设计

2.7V 至 38V/500mA 低噪声降压-升压型 充电泵可节省空间并降低 EMI

8

8减少PCB排放的低噪声设计实践

1270

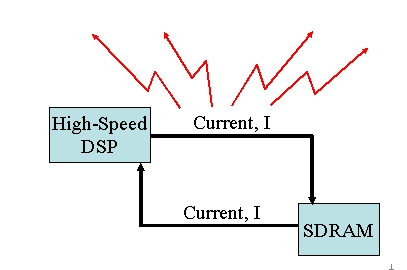

1270DSP系统中噪声和电磁干扰EMI的影响以及控制方法

1137

1137

EMI抗干扰设计与低噪声电路设计的方法有哪些

1355

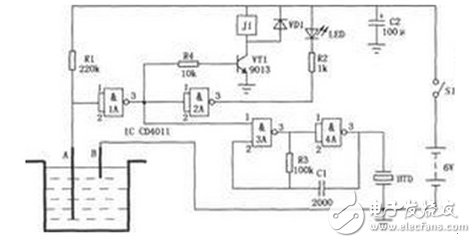

1355高低水位控制电路图大全(六款高低水位控制电路原理图详解)

153293

153293

基于Proteus与单片机的交通灯控制电路设计

16523

16523

感应加热电源控制电路

15018

15018基于S波段低噪声放大电路设计

806

806

如何避免在DSP系统中出现噪声和EMI问题

15

15长寿命低噪声的电磁制动控制电路制作

530

530

水温测量与控制电路设计

117

117PWM控制电路原理与电路设计FPGA

2043

2043

电机控制电路设计

2161

2161

如何避免在DSP系统中出现噪声和EMI问题

278

278

电子发烧友App

电子发烧友App

评论