摘要:在无线通信中,降低频率合成器的相位噪声和抑制其相应的寄生输出,一直是设计者追求的目标。PE3293是Peregrine公司生产的高性能1.8GHz/550MHz双模整数分频集成锁相环电路,它具有超低的寄生输出。文中介绍了PE3293的特点功能和组成原理,给出了PE3293在频率综合器设计中的应用电路。

关键词:频率合成器;相位噪声;寄生输出;PLL;PE3293

1 引言

同时频率切换时间和寄生输出的抑制对系统也很重要。频率合成器作为一种高质量的信号源,与电子系统的性能有很大关系。在通信系统中,使用高稳定的信号源,可以充分利用频率资源。实际上,在电子对抗、导航等电子系统中,高指标的信号源会给系统带来良好的性价比,从而为系统设计师提供可靠的技术保障。

2 PE3293的特点功能

表1 PE3293(以20脚TSSOP封装为例)的引脚定义

| 序 号 | 名 称 | 类 型 |

功 能 描 述 |

| 1 | N/C | 不连接 | |

| 2 | VDD | 电源,2.7~3.3V,需用一个电容就近旁路接地 | |

| 3 | CP1 | 输出 | PLL1内部的脉冲成形输出,用作外部VCO的输入驱动 |

| 4 | GND | 地端 | |

| 5 | fin1 | 输入 | 从PLL1(RR)VCO来的预分频器输入,最大频率为1.8GHz |

| 6 | Dec1 | PLL1的电源去耦端,有必要用一个电容就近接地 | |

| 7 | VDD1 | PLL1预分频器的电源,一般经3.3kΩ的电阻连到VDD | |

| 8 | fr | 输入 | 参考频率输入 |

| 9 | GND | 地端 | |

| 10 | f0LD | 输出 | 复用器输出,包括PLL1和PLL2主计数器或参考计数器输出/时钟检测信号,以及移位寄存器移出数据 |

| 11 | Clock | 输入 | CMOS时钟输入,在时钟信号的上升沿,各种计数器的串行数据将送入21bit的移位寄存器 |

| 12 | Data | 输入 | 二进制串行数据输入,为CMOS输入数据,MSB先,2bit的LSB为控制比特 |

| 13 | LE | 输入 | 负载使能CMOS入,当LE为高时,21bit的串行移位移位寄存器中的数据字将被送入相应的四个锁存器之一中(由控制比特决定) |

| 14 | VDD2 | 输出 | PLL1预分频器的电源,使用时经3.3kΩ的电阻连到VDD0 |

| 15 | Dec2 | 输出 | PLL1的电源去耦端,有必要用一个电容就近接地 |

| 16 | fin2 | 输入 | 从PLL1(IF)VCO来的预分频器输入,最大频率为500MHz |

| 17 | GND | 地端 | |

| 18 | CP2 | 输出 | PLL1内部的脉冲成形输出,用作外部VCO的输入驱动 |

| 19 | VDD | 2.7~3.3V电源,需经一个电容就近接地 | |

| 20 | VDD | 电源,2.7~3.3V,需经一个电容就近接地 |

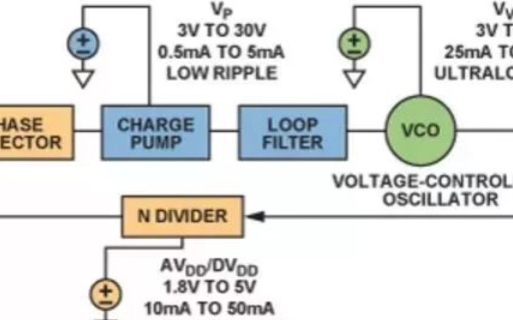

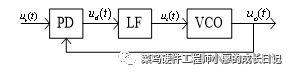

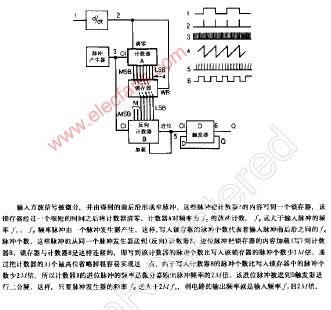

3 PE3293的组成原理

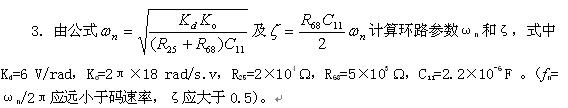

PLL1(RF)的VCO频率fin1的大小与fr的值有关,它们之间的关系如下:

数据输入端Data输入的数据在时钟输入Clock 的上升沿逐次移入21bit的移位寄存器且MSB(M16)在先,因此,当LE为高时,数据送入由图4所示的最后2位地址位所决定的21bit移位寄存器的相应地址中。比如,当程序对计数器A1进行控制 时,送入寄存器的最后两比特(S0, S1)应为(1,1),计数器A1中的5比特位可以按表2设置。因此,在正常情况下,即使不用PLL2?IF?? S16也应设为0。应注意的是,PE3293的工作模式、鉴相器极性和功率控制均可以由C10~C14和C20~C24来控制。

表2 PE3293的计数器设计表

| 分频比 | MSB | LSB | 地址位 | ||||

| S11 | S10 | S9 | S8 | S7 | S1 | S0 | |

| A14 | A13 | A12 | A11 | A10 | 1 | 1 | |

| 0 | 0 | 0 | 0 | 0 | 0 | 1 | 1 |

| 1 | 0 | 0 | 0 | 0 | 1 | 1 | 1 |

| 2 | 0 | 0 | 0 | 1 | 0 | 1 | 1 |

| - | - | - | - | - | - | 1 | 1 |

| 31 | 1 | 1 | 1 | 1 | 1 | 1 | 1 |

5 结语

- 锁相环(86948)

相关推荐

高性能锁相环PE3293及其应用

摘要:在无线通信中,降低频率合成器的相位噪声和抑制其相应的寄生输出,一直是设计者追求的目标。PE3293是Peregrine公司生产的高性能1.8GHz/550MHz双模整数分频

2006-03-11 13:33:39 486

486

486

486

什么是锁相环 锁相环的组成 锁相环选型原则有哪些呢?

大家都知道锁相环很重要,它是基石,锁相环决定了收发系统的基础指标,那么如此重要的锁相环选型原则有哪些呢?

2023-08-01 09:37:05 672

672

672

672

模拟锁相环和数字锁相环区别

模拟锁相环和数字锁相环的主要区别在于它们的控制方式不同。模拟锁相环是通过模拟电路来控制频率和相位,而数字锁相环是通过数字信号处理技术来控制频率和相位。此外,模拟锁相环的精度较低,而数字锁相环的精度较高。

2023-02-15 13:47:53 2765

2765

2765

2765如何使用FPGA实现高性能全数字锁相环的设计

本文提出了一种适用范围广泛的全数字锁相环(ADPLL)实现方法.在锁相环输入频率未知的情况下,实现锁相锁频功能。本文从全数字锁相环的基本实现方式入手.进行改进,并使用VH DL语言建模,使用FPGA进行验证。

2021-01-26 15:03:00 65

65

65

65如何使用FPGA实现高性能全数字锁相环的设计

本文提出了一种适用范围广泛的全数字锁相环(ADPLL)实现方法.在锁相环输入频率未知的情况下,实现锁相锁频功能。本文从全数字锁相环的基本实现方式入手.进行改进,并使用VH DL语言建模,使用FPGA进行验证。

2021-01-26 15:03:00 18

18

18

18数字锁相环(DPLL),数字锁相环(DPLL)是什么?

数字锁相环(DPLL),数字锁相环(DPLL)是什么?

背景知识:

随着数字电路技术的发展,数字锁相环在调制解调、频率合成、FM 立体声解码、彩色副

2010-03-23 15:06:21 5312

5312

5312

5312软件锁相环的设计与应用

根据虚拟无线电技术的特点和锁相环的基本原理,提出一种适于计算机软件化实现的锁相环数学模型,分析不同参数对锁相环捕获和跟踪性能的影响,得出不同情况下参数设定的基

2008-08-15 12:36:19 98

98

98

98锁相环是如何实现倍频的?

锁相环是如何实现倍频的? 锁相环(Phase Locked Loop, PLL)是一种电路,用于稳定和恢复输入信号的相位和频率。它可以广泛应用于通信、计算机、音频等领域中。其中一个重要的应用就是

2023-09-02 14:59:37 386

386

386

386锁相环原理

锁相环原理

锁相环路是一种反馈电路,锁相环的英文全称是Phase-Locked Loop,简称PLL。其作用是使得电路上的时钟和某一外部时钟的相位同步。因锁相环可以

2007-08-21 14:46:04 4689

4689

4689

4689模拟锁相环,模拟锁相环原理解析

模拟锁相环,模拟锁相环原理解析

背景知识:

锁相技术是一种相位负反馈控制技术,它利用环路的反馈原理来产生新的频率点。它的主要

2010-03-23 15:08:20 5716

5716

5716

5716锁相环PLL的基础知识

锁相环 (PLL) 电路存在于各种高频应用中,从简单的时钟清理电路到用于高性能无线电通信链路的本振 (LO),再到矢量网络分析仪 (VNA) 中的超快速开关频率合成器。本文解释了锁相环电路的一些构建模块,并参考了每种应用,以帮助指导新手和锁相环专家导航器件选择以及每种不同应用固有的权衡取舍。

2022-12-23 14:03:54 2293

2293

2293

2293

模拟锁相环应用实验

一、实验目的1、掌握模拟锁相环的组成及工作原理。2、学习用集成锁相环构成锁相解调电路。3、学习用集成锁相环构成锁相倍频电路。

二、锁相环路的基本原理

2009-03-22 11:44:37 124

124

124

124详解FPGA数字锁相环平台

一、设计目标 基于锁相环的理论,以载波恢复环为依托搭建数字锁相环平台,并在FPGA中实现锁相环的基本功能。 在FPGA中实现锁相环的自动增益控制,锁定检测,锁定时间、失锁时间的统计计算,多普勒频偏

2017-10-16 11:36:45 18

18

18

18锁相环技术在频率跟踪中的应用研究

本文介绍锁相环及其频率跟踪的基本原理,给出二阶锁相环和四阶锁相环的设计依据。在此基础上,对四阶锁相环实现频率跟踪的转换时间进行了仿真,就如何减小频率跟踪的转换时间

2010-07-29 16:28:14 42

42

42

42锁相环(PLL)的工作原理及应用

锁相环路是一种反馈控制电路,简称锁相环(PLL,Phase-Locked Loop)。锁相环的特点是:利用外部输入的参考信号控制环路内部振荡信号的频率和相位。

2022-03-29 09:54:55 10729

10729

10729

10729并网逆变器锁相环设计

直接影响到逆变器的性能。如何利用DSP等数字芯片,设计出一个可以克服各种电网畸变及故障的软件锁相环,是当今科学研究的热点问题。 本文首先论述的锁相环技术的发展历史及前景,简单阐述了传统的锁相环技术,指出了它们的缺点并

2017-12-08 11:12:07 23

23

23

23基于FPGA的自适应锁相环设计

利用锁相环进行载波跟踪是获取本地载波的一种重要方法,针对锁相环的噪声性能和跟踪速度不能同时达到最优的限制,在锁相环PLL中引入自适应模块,根据环路所处

2010-11-25 17:19:33 29

29

29

29pll锁相环的作用 pll锁相环的三种配置模式

pll锁相环的作用 pll锁相环的三种配置模式 PLL锁相环是现代电子技术中广泛应用的一种电路,它的作用是将一个特定频率的输入信号转换为固定频率的输出信号。PLL锁相环的三种配置模式分别为

2023-10-13 17:39:48 167

167

167

167pll锁相环倍频的原理

pll锁相环倍频的原理 PLL锁相环倍频是一种重要的时钟信号处理技术,广泛应用于数字系统、通信系统、计算机等领域,具有高可靠性、高精度、快速跟踪等优点。PLL锁相环倍频的原理涉及到锁相环,倍频器

2023-09-02 14:59:24 444

444

444

444锁相环的研究和频率合成

锁相环的研究和频率合成一、实验目的:1. 振荡器(VCO)的V—f 特性的研究2. 对称波锁相环基本特性的研究3. 利用锁相环实现频率合成二、锁相环原理:

2009-03-06 20:02:52 1771

1771

1771

1771

锁相环的基本组成和工作原理

因锁相环可以实现输出信号频率对输入信号频率的自动跟踪,所以锁相环通常用于闭环跟踪电路。锁相环在工作的过程中,当输出信号的频率与输入信号的频率相等时,输出电压与输入电压保持固定的相位差值,即输出电压与输入电压的相位被锁住,这就是锁相环名称的由来。

2022-05-10 14:25:19 6544

6544

6544

6544如何实现高性能的锁相环(PLL)设计

锁相环(PLL)是现代通信系统的基本构建模块,通常用在无线电接收机或发射机中,主要提供"本振"(LO)功能;也可用于时钟信号分配和降噪,而且越来越多地用作高采样速率模数或数模转换的时钟源。

2022-03-04 14:45:01 2941

2941

2941

2941

基于锁相环的低频函数发生器

介绍了锁相环的原理以及Freescale公司的锁相环频率合成器件MC145151-2的主要特点,给出了MC145151-2和ICL8038低频锁相环函数发生器的工作原理、设计思想、电路结构、模块设计方法及其

2010-12-11 17:45:49 51

51

51

51软件锁相环在频率突变时锁不住 锁相环无法锁定怎么办?

软件锁相环在频率突变时锁不住 锁相环无法锁定怎么办? 锁相环(PLL)是一种用于在电路中生成稳定频率的技术。它是在1960年代开发的,并被广泛应用于通信、雷达、卫星技术等领域中。锁相环的主要作用

2023-10-13 17:39:58 97

97

97

97智能全数字锁相环的设计

智能全数字锁相环的设计:在FPGA片内实现全数字锁相环用途极广。本文在集成数字锁相环74297的基础上进行改进,设计了锁相状态检测电路,配合CPU对环路滤波参数进行动态智能配

2009-06-25 23:32:57 70

70

70

70锁相环的性能,仿真和设计(第3版)

锁相环的性能,仿真和设计(第3版):

PLL BASICS ......9CHAPTER 1 BASIC PLL OVERVIEW .....11CHAPTER 2 THE CHARGE PUMP

2009-07-25 16:56:22 340

340

340

340基于高压VCO的高性能锁相环设计

锁相环(PLL) 是现代通信系统的基本构建模块。PLL 通 常用在无线电接收机或发射机中,主要提供本振(LO) 功 能;也可用于时钟信号分配和降噪,而且越来越多地用作高采 样速率模数 (A

2011-03-30 16:01:16 49

49

49

49锁相环的基本组成及工作原理

因锁相环可以实现输出信号频率对输入信号频率的自动跟踪,所以锁相环通常用于闭环跟踪电路。锁相环在工作的过程中,当输出信号的频率与输入信号的频率相等时,输出电压与输入电压保持固定的相位差值,即输出电压与输入电压的相位被锁住,这就是锁相环名称的由来。

2020-11-03 14:55:49 14026

14026

14026

14026

基于数字锁相环消除反馈滞后的方法

针对传统数字锁相环存在的反馈滞后造成系统动、静态性能退化的问题,提出一种消除反馈滞后一拍的方法,以无反馈滞后理想数字锁相环为参考模型,利用数字锁相环当前输出与上一时刻输出,计算得到与理想数字锁相环

2018-01-02 10:30:41 9

9

9

9智能全数字锁相环的设计

摘要: 在FPGA片内实现全数字锁相环用途极广。本文在集成数字锁相环74297的基础上进行改进,设计了锁相状态检测电路,配合CPU对环路滤波参数进行动态智

2009-06-20 12:39:32 1313

1313

1313

1313

锁相环设计仿真与应用

锁相环设计仿真与应用:PLL Performance, Simulation, and Design3rd EditionI would like to thank the following people for their as

2008-08-16 10:14:53 68

68

68

68锁相环设计与仿真的基本知识

锁相环:在通信领域中,锁相环是一种利用反馈控制原理实现的频率及相位同步技术,其作用是将电路输出的时钟与其外部的参考时钟保持同步。

2023-06-30 15:53:39 1199

1199

1199

1199

一种基于FPGA实现的全数字锁相环

锁相环被广泛应用于电力系统的测量和控制中。介绍了一种新型的基于比例积分控制逻辑的全数字锁相环。通过对其数学模型的分析,阐述了该锁相环的各项性能指标与设计参数的

2010-07-02 16:54:10 29

29

29

29锁相环(PLL)基本原理 当锁相环无法锁定时该怎么处理的呢?

锁相环(PLL)基本原理 当锁相环无法锁定时该怎么处理的呢? 锁相环(Phase Locked Loop, PLL)是一种电路系统,它可以将输入信号的相位锁定到参考信号的相位。在锁相环中,反馈回路

2023-10-23 10:10:15 47

47

47

47锁相环的原理及应用详细资料说明

锁相环(PLL)电路存在于各种高频应用中,从简单的时钟净化电路到用于高性能无线电通信链路的本振(LO),以及矢量网络分析仪(VNA)中的超快开关频率合成器。锁相环是一种反馈系统,其中电压控制振荡器

2020-12-16 13:57:00 24

24

24

24使用MAX9382的锁相环应用

本应用笔记讨论了影响锁相环(PLL)死区和抖动性能的鉴频鉴相器特性。在采用电荷泵环路滤波器设计的PLL中,提供最短持续时间的鉴相器输出脉冲几乎消除了PLL死区行为和相关锁相环抖动。

2023-02-23 17:52:07 368

368

368

368

使用MC145170锁相环实现调频锁相环收音机的PCB原理图免费下载

本文档的主要内容详细介绍的是使用MC145170锁相环实现调频锁相环收音机的PCB原理图免费下载。

2020-11-02 17:15:00 72

72

72

72使用FPGA实现数字锁相环的设计资料说明

锁相环路是一种反馈控制电路,简称锁相环( PLL)。锁相环的特点是:利用外部输入的参考信号控制环路内部振荡信号的频率和相位。因锁相环可以实现输出信号频率对输入信号频率的自动跟踪, 所以锁相环通常

2020-08-06 17:58:25 24

24

24

24使用PLD内部锁相环解决系统设计难题

摘要: 从整个应用系统的角度,理解和分析PLD内部锁相环;在此基础上,深入剖析锁相环的相移结构,同时用这个技术解决系统设计难题。

关键

2009-06-20 12:40:02 651

651

651

651

什么是锁相环?PLL和DLL都是锁相环区别在哪里?

什么是锁相环?PLL和DLL都是锁相环区别在哪里? 锁相环(Phase Locked Loop,PLL)是一种基于反馈的控制系统,用于提供稳定的时钟信号。它可以将参考信号的相位与输出信号的相位进行

2023-10-13 17:39:53 106

106

106

106基于TRAC器件的锁相环设计研究

以TRAC020LH 完全可重配置模拟器件和TRAC 开发软件为基础,设计模拟锁相环;给出仿真结果和利用PIC 单片机对器件进行配置的应用电路。该锁相环成功应用于逆变器的频率跟踪,性能

2009-04-15 11:42:39 11

11

11

11快速了解Pasternack推出的高性能USB控制锁相环频率合成器

稳定性、高精度以及优异的相位噪声特性,从而可使信号链中的器件以最佳性能工作。这些新式锁相环频率合成器的用途包括信号发生器、台式测试和测量、电子战及微波无线电。

2018-04-26 11:16:00 601

601

601

601 电子发烧友App

电子发烧友App

评论