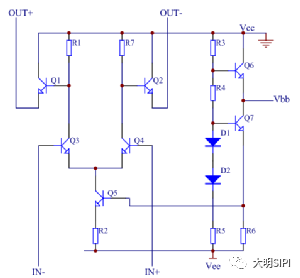

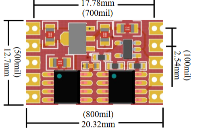

什么叫做LVDS信号?请问TTL信号与LVDS信号有什么区别? LVDS信号 LVDS(Low Voltage Differential Signaling)又称低压差分信号传输技术,是一种采用差分

2023-10-18 15:38:18 70

70 LVDS是一种低摆幅的差分信号技术,它使得信号能在差分PCB线对或平衡电缆上以几百Mbps的速率传输,其低压幅和低电流驱动输出实现了低噪声和低功耗。

2023-10-02 16:44:00 252

252

差分信号和差模信号的区别联系 在电路与传输中,信号可以用多种方式进行传递。其中包括差分信号和差模信号。差分信号和差模信号,可以用于很多的应用,例如在通信、功率放大器和模拟电路等领域中,起着非常重要

2023-09-19 17:33:46 329

329 差分信号怎么辨别方向? 差分信号是一种衡量电路中两点电势差的方法。它使用两个相同的传感器,将它们所测得的电信号进行相减,得出一个表示该差异的值。但是,差分信号的方向如何辨别呢? 在分析差分信号的方向

2023-09-19 17:33:44 163

163 信号发生器怎么产生差分信号? 信号发生器是电子仪器中非常重要的一个设备,它是用来产生高精度、高稳定性电信号的设备。在电子行业中,它扮演着至关重要的角色,广泛用于各种电子测试、电信实验以及各种实验室等

2023-09-19 17:23:02 379

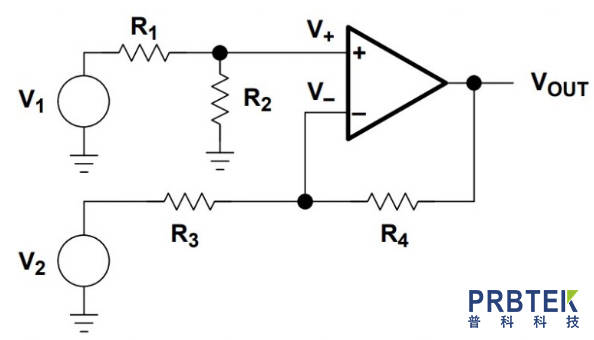

379 差分信号如何转换成单端信号? 差分信号和单端信号是电子信号传输中非常常见的两种形式。差分信号由两个互相反向的信号组成,单端信号只有一个信号。差分信号由于可以减少电磁干扰和提高传输距离,常被用于高速

2023-09-19 17:22:55 1185

1185 差分信号怎么用示波器测量? 差分信号是一种相对于地面电位或者参考电位进行测量的电信号。与普通电信号不同的是,差分信号由两条互补线性电缆或者两只信号线组成。这两条线路中,一条线路携带着正极性信号,另一

2023-09-19 17:22:47 226

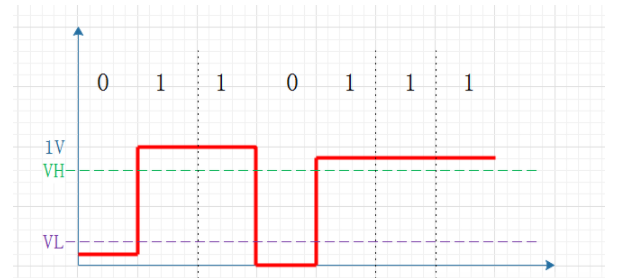

226 差分信号是5V的还是24V的?差分信号电压是多少? 差分信号是指由两个相同但电位不同的信号组成的信号,它们的电位差就是差分信号。在电子技术中,通常用差分信号来传输信号,差分信号可以使信号的抗干扰能力

2023-09-19 17:22:19 509

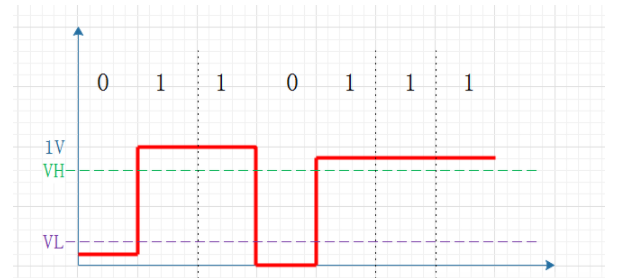

509 差分信号怎么判断0和1? 差分信号是指信号的两个不同状态之间的差值,这种信号在很多通信系统中都被广泛应用。传输数据时,差分信号被发送到接收端,接收端需要根据差分信号来判断0和1。那么,差分信号

2023-09-19 17:22:16 455

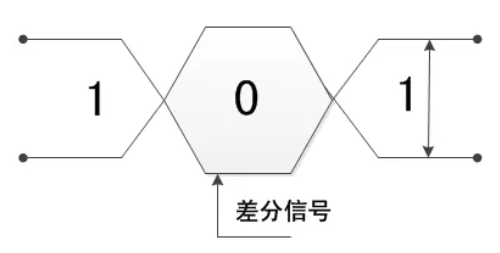

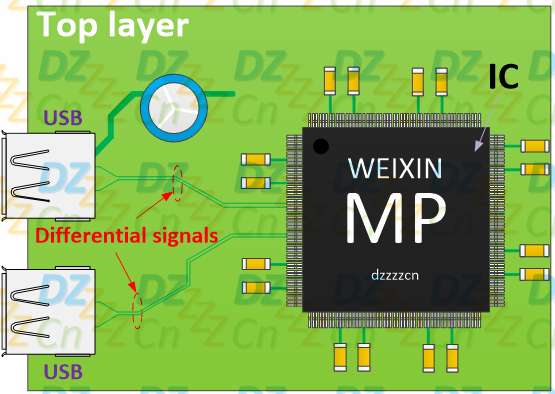

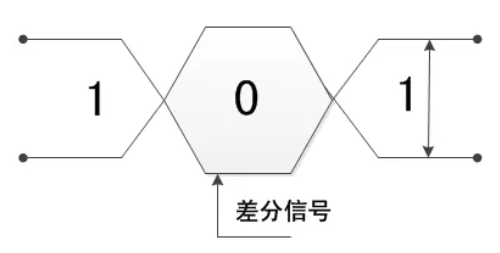

455 差分线是 PCB 设计中非常重要的一部分信号线,因此我们对差分信号的处理要求相当严谨。 (差分信号原理图示) 差分信号与单端信号的区别 单端信号指的是用一个线传输的信号,参考点为大地。换句话说,单端

2023-09-12 10:15:15 611

611

▼关注公众号: 工程师看海▼ 差分线是PCB设计中非常重要的一部分信号线,因此我们对差分信号的处理要求相当严谨。 (差分信号原理图示) 差分信号 与 单端信号 的区别 单端信号 指的是用一个线

2023-09-05 08:46:52 673

673

差分信号是用一个数值来表示两个物理量之间的差异。从严格意义上来讲,所有电压信号都是差分的,因为一个电压只能是相对于另一个电压而言的。

2023-08-08 16:28:51 816

816

单端信号是相对于差分信号而言的,单端输入指信号有一个参考端和一个信号端构成,参考端一般为地端。

2023-08-07 09:39:05 259

259

差分信号是用一个数值来表示两个物理量之间的差异。从严格意义上来讲,所有电压信号都是差分的,因为一个电压只能是相对于另一个电压而言的。

2023-08-04 10:23:49 449

449

差分信号在高速电路设计中的应用越来越广泛,电路中最关键的信号往往都要采用差分结构设计,比如PCIe、Ethernet、USB、HDMI等。

2023-06-14 14:22:39 3775

3775

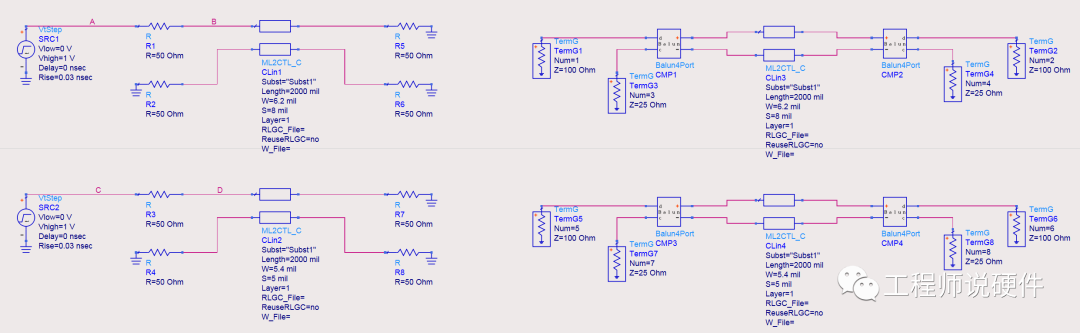

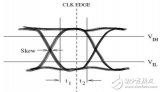

本章我们开始《信号完整性基础》 系列第五章节差分信号相关知识的讲解。随着信号速率的不断提高,传统并行接口的应用挑战越来越大,基于差分信号的Serdes接口越来越普及,差分信号在其中的重要性不言而喻。

2023-06-09 10:37:38 1193

1193

差分信号是共模信号和差模信号的叠加,理想情况下共模信号是恒定的。

2023-06-09 09:08:13 934

934

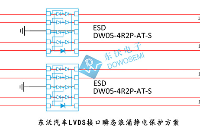

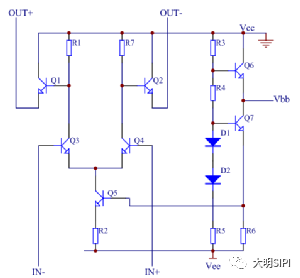

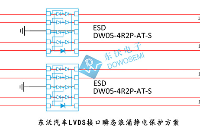

都知道,汽车工作环境比较恶劣,为此,在设计高速低电压差分信号(LVDS)接口系统时,应选用正确的电路保护元件免受瞬态威胁并满足现代汽车的安全性和可靠性。事实证明,在 LVDS 差分线路上,选用瞬态

2023-06-08 09:43:37 355

355

单端探头是一种常见的测量工具,它可以用于测量电路中的电压、电流、阻抗等参数。在差分信号测量中,单端探头可以通过一些特殊的技术来实现对差分信号的测量。下面将介绍单端探头如何测量差分型号。 1.

2023-06-02 10:06:16 778

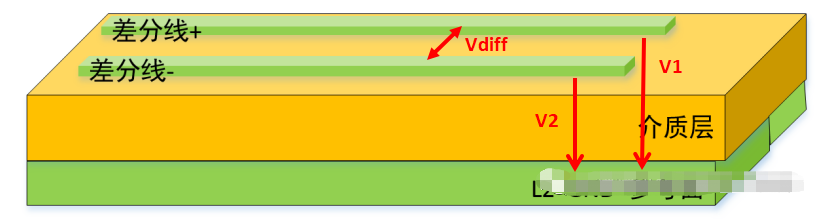

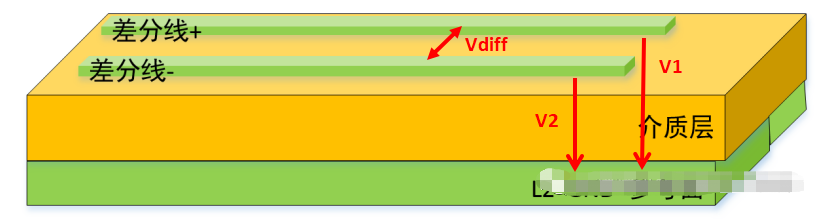

778 差分信号是指利用两个输出驱动pin去驱动两根传输线。这两根传输线,一根传输信号,另一根传输它的互补信号。接收端看到的信号是这两条传输线上的信号压差。差分对就是用来传输一对差分信号,并且存在耦合关系的传输线。例如LVDS就是一种常见的低压差差分信号。

2023-05-06 16:02:47 3126

3126

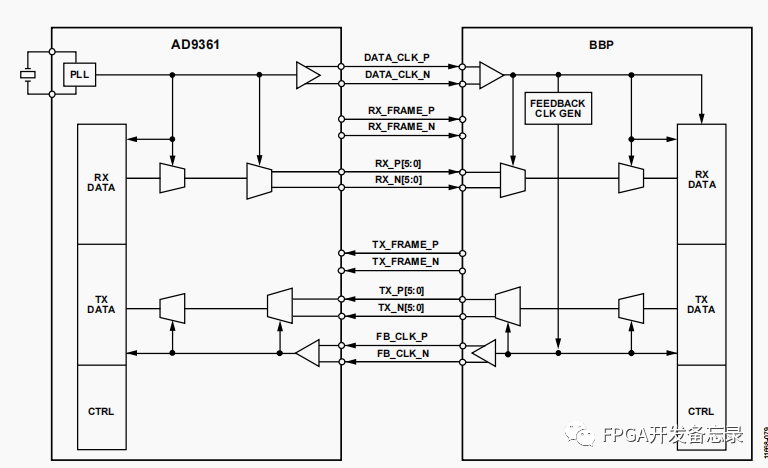

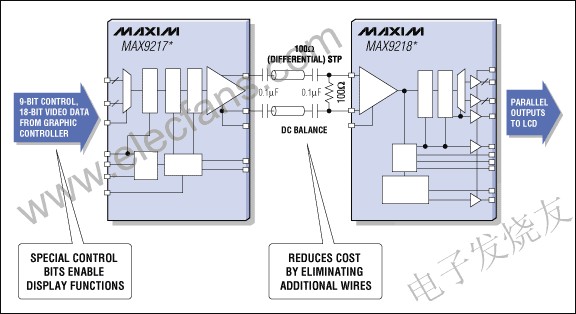

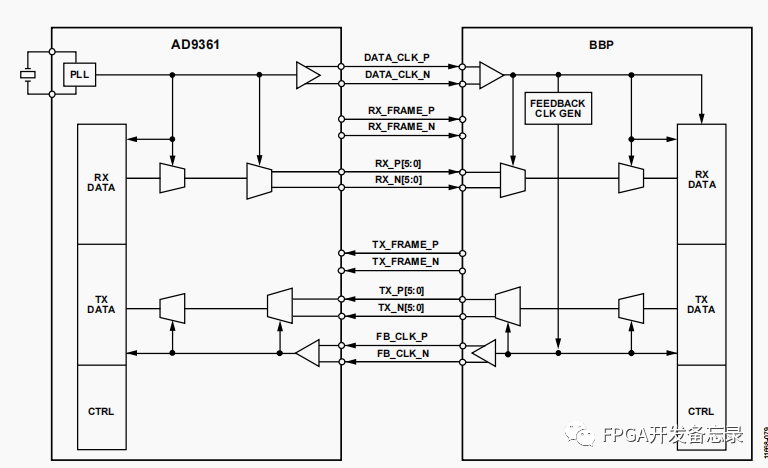

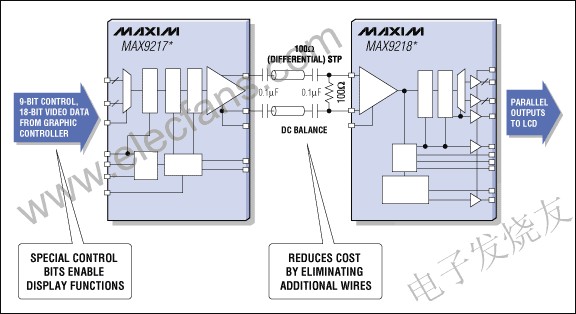

接下来将介绍AD9361数据路径在低电压差分信号(LVDS)模式下运行。AD9361数据接口使用并行总线(P0和P1)在AD9361和BBP之间传输数据样本。

2023-04-25 15:51:25 3015

3015

单端信号是相对于差分信号而言的,单端输入指信号由一个参考端和一个信号端构成,参考端一般为地端。

2023-04-07 11:26:28 919

919 LVDS (Low Voltage Differential Signaling)是一种小振幅差分信号技术,它使用非常低的幅度信号 (250mV~450mv)通过一对平行的PCB走线或平衡电缆传输数据是一种专业的低电压差分信号

2023-04-06 09:46:43 745

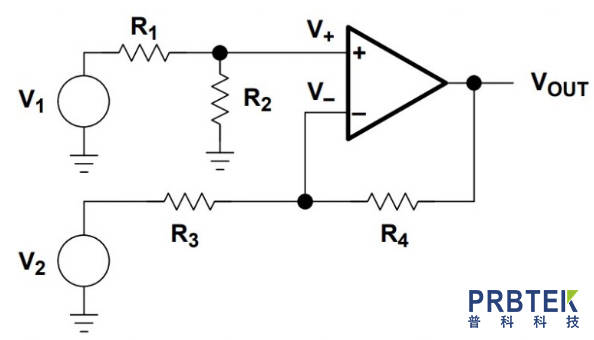

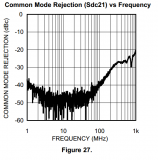

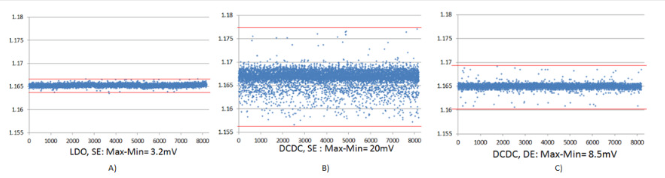

745 差分信号是一种常见的信号形式,它是指由两个信号之间的差值构成的信号。在许多应用中,我们需要处理低压差分信号,这就要求电路设计者使用带有低偏置和高共模抑制的差分放大器。

2023-04-03 11:14:55 791

791

LVDS(Low-Voltage Differential Signaling ,低电压差分信号)是美国国家半导体(National Semiconductor, NS,现TI)于1994年提出

2023-03-08 15:40:00 1912

1912

来源:罗姆半导体社区 在高速PCB设计中,差分信号(DIFferential Signal)的应用越来越广泛,电路中最关键的信号往往都要采用差分结构设计。 为什么这样呢?和普通的单端信号走线相比

2023-02-02 14:33:07 366

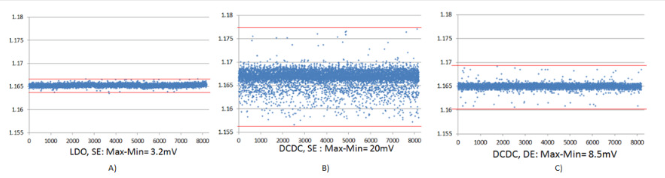

366 差分信号是在模拟测量过程中解决噪声的宝贵工具。差分信号的优势在于将噪声作为共模消除的简单性。挑战在于设计一个电路,使差分对的两个导体实际上具有共性噪声。这一挑战延伸到嵌入式硬件工程师和集成电路(IC)设计人员。

2022-12-02 11:12:22 1231

1231

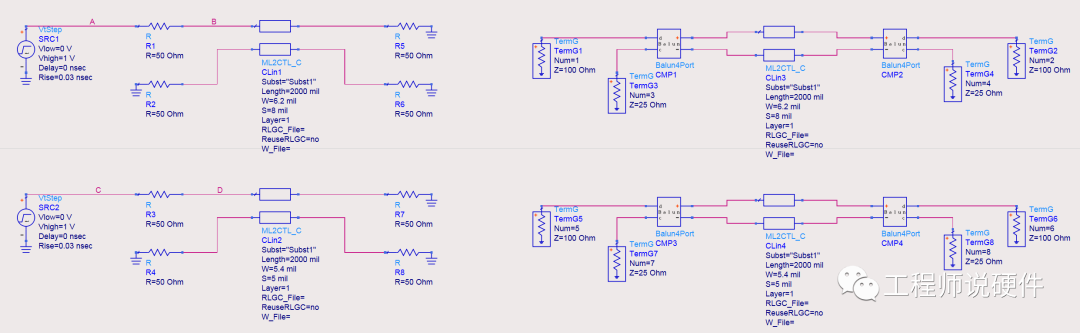

如题,需要一个差分信号输入仿真,不知道怎么产生差分信号。。。。

2012-11-28 14:48:55

使用低压差分信号的带电插入

2022-11-14 21:08:29 0

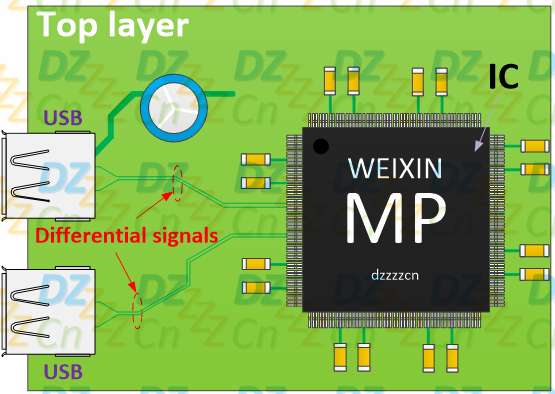

0 在高速 PCB 设计中,差分信号的应用越来越广泛,这主要是因为和普通的单端信号走线相比,差分信号具有抗干扰能力强、 能有效抑制EMI、时序定位精确的优势。作为一名(准)PCB 设计工程师,我们当然需要充分理解差分信号!

2022-11-07 11:26:15 7

7 获得连接:差分信号发送

2022-11-07 08:07:22 0

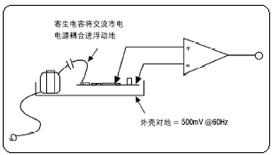

0 探头有很多种,差分探头在开关电源中的应用非常普遍,差分探头差分信号的常用测量方法如下。

2022-10-14 15:40:24 3617

3617 AC 系列模块是精密的差分信号转换器,可将正负电压或差分信号转换为单路正(或正负) 电压信号。

2022-08-19 15:37:19 0

0 LVDS(Low Voltage Differential Signal)即低电压差分信号。

2022-07-03 15:20:13 1911

1911 AC 系列模块是精密的差分信号转换器,可将正负电压或差分信号转换为单路正(或正负) 电压信号。

2022-05-19 10:47:59 1889

1889

习惯了单端信号,对差分信号的使用还是会有点发怵。所以有的器件厂商,虽然输入接口是差分,但是会注明一下,单端输入时的具体接法。

2022-05-16 16:46:33 2280

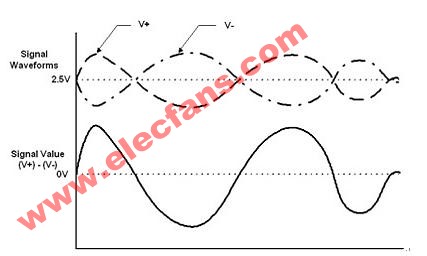

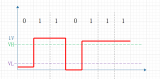

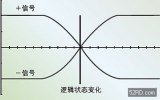

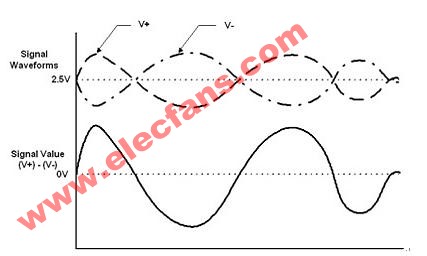

2280 差分传输是一种信号传输的技术,区别于传统的一根信号线一根地线的做法(单端信号),差分传输在这两根线上都传输信号,这两个信号的振幅相等,相位相反。在这两根线上传输的信号就是差分信号。

2022-03-28 10:44:47 2387

2387 在高速 PCB 设计中,差分信号的应用越来越广泛,这主要是因为和普通的单端信号走线相比,差分信号具有抗干扰能力强、能有效抑制EMI、时序定位精确的优势。作为一名(准)PCB 设计工程师,我们当然需要充分理解差分信号

2022-02-12 09:55:51 9700

9700

单端信号是相对于差分信号而言的,单端输入指信号有一个参考端和一个信号端构成,参考端一般为地端。差分传输是一种信号传输的技术,区别于传统的一根信号线一根地线的做法(单端信号),差分传输在这两根线上都传输信号,这两个信号的振幅相等,相位相反。

2022-02-09 10:14:02 3

3 差分传输是一种信号传输的技术,区别于传统的一根信号线一根地线的做法,差分传输在这两根线上都传输信号,这两个信号的振幅相等,相位相反。在这两根线上传输的信号就是差分信号。差分信号又称差模信号,是相对共模信号而言的。

2022-02-09 10:04:29 14

14 怎么对原理图的差分信号添加差分属性呢?

2022-01-02 09:02:00 2074

2074 在高速 PCB 设计中,差分信号的应用越来越广泛,这主要是因为和普通的单端信号走线相比,差分信号具有抗干扰能力强、能有效抑制EMI、时序定位精确的优势。作为一名(准)PCB 设计工程师,我们当然需要充分理解差分信号

2021-01-29 07:41:33 16

16 单端信号 单端信号是相对于差分信号而言的,单端输入指信号有一个参考端和一个信号端构成,参考端一般为地端。 差分信号 差分传输是一种信号传输的技术,区别于传统的一根信号线一根地线的做法(单端信号),差

2020-12-11 15:04:37 7169

7169

差分放大电路在数显表应用很多,本文以图文形式简单介绍差分信号、单端信号的概念及差分放大电路的作用,方便大家对差分放大电路相关知识有所了解。 1、什么是单端信号?什么是差分信号?单端传输是指用一根

2020-12-03 22:48:00 34

34 当不采用单端信号而采取差分信号方案时,我们用一对导线来替代单根导线,增加了任何相关接口电路的复杂性。那幺差分信号提供了什幺样的有形益处,才能证明复杂性和成本的增加是值得的呢?

2020-11-30 10:04:06 14733

14733 在高速PCB设计中,差分信号(DIFferential Signal)的应用越来越广泛,电路中最关键的信号往往都要采用差分结构设计。

2020-04-20 17:55:24 1154

1154 在高速PCB设计中,差分信号(DIFferential Signal)的应用越来越广泛,电路中最关键的信号往往都要采用差分结构设计。

2020-01-10 17:55:47 1554

1554 差分信号(DifferenTIal Signal)在高速电路设计中的应用越来越广泛,电路中最关键的信号往往都要采用差分结构设计

2020-01-03 17:32:33 1673

1673 差分信号(DifferenTIal Signal)在高速电路设计中的应用越来越广泛,电路中最关键的信号往往都要采用差分结构设计。

2019-08-26 16:23:20 591

591 简要介绍提供8kV IEC ESD保护的ADI MLVDS(多点低压差分信号)收发器。概要说明MLVDS的应用领域、特性及其与LVDS的比较。

2019-07-05 06:11:00 1821

1821 差分信号的第二个主要好处是,它对外部电磁干扰(EMI)是高度免疫的。一个干扰源几乎相同程度地影响差分信号对的每一端。既然电压差异决定信号值,这样将忽视在两个导体上出现的任何同样干扰。除了对干扰不大灵敏外,差分信号比单端信号生成的 EMI 还要少。

2019-02-19 10:06:52 8856

8856

差分传输是一种信号传输的技术,区别于传统的一根信号线一根地线的做法,差分传输在这两根线上都传输信号,这两个信号的振幅相等,相位相差180度,极性相反。在这两根线上传输的信号就是差分信号。

2018-01-15 10:08:15 57733

57733

布线非常靠近的差分信号对相互之间也会互相紧密耦合,这种互相之间的耦合会减小EMI发射,差分信号线的主要缺点是增加了PCB的面积,本文介绍电路板设计过程中采用差分信号线布线的布线策略。 众所周知,信号

2017-12-11 15:47:01 817

817

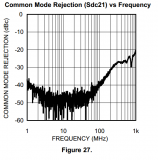

您是否注意到了差分信号在高性能信号路径中正日益占据主导地位?差分信号可提供多种优势!我一直在考虑这样一个事实,即每个差分信号路径都有一个与其相关的寄生共模信号路径。在差分信号路径中,大部分环境噪声都可作为共模噪声耦合。很多差分器件都能很好地抑制这种噪声。

2017-04-08 04:49:54 10744

10744

LVDS,即Low Voltage Differential Signaling,是一种低压差分信号技术接口。它是美国NS公司(美国国家半导体公司)为克服以TTL电平方式传输宽带高码率数据时功耗大、EMI电磁干扰大等缺点而研

2012-07-19 16:01:53 5074

5074

低电压差分信号(LVDS)是EIA/TIA-644标准中定义的总线技术。这种技术的特点是通过使用差分信号有较低的电压摆幅,从而具备Gbps数据速率的能力。

2011-08-01 16:44:13 1474

1474 差分信号就是驱动器端发送两个等值、反相的信号,接收端通过比较这两个电压的差值来判断逻辑状态0还是1。而承载差分信号的那一对走线就称为差分走线。 差分信号,有些也称差动信号,用两根完全一样,极性相反的信号传输一路数据,依靠两根信号电平差进行判决

2011-03-11 15:22:03 212

212 随着数字电路数据量的提高,数据的传输速率也越来越快,LVDS(低压差分信号)标准越来越多的应用在FPGA和ASIC器 件中。文章对LVDS信号的特点进行了分析,说明了PCB设计中差分走线的注意事项并结合实际应用设计了一块LVDS接口板。 关键词: LVDS; PCB设计;接口;阻抗

2011-02-23 09:54:03 339

339 为了节约PCB板空间,充分灵活利用FPGA内部资源,对FPGA内置差分信号匹配终端进行研究。根据差分信号阻抗匹配的基础理论,在自制的PCB电路板上利用差分信号线传递时钟和图像数据

2011-01-04 17:07:13 40

40 基于低电压差分信号(LVDS)的高速信号传输

2010-12-17 17:21:46 38

38 低电压差分信号传输(LVDS)已经在众多应用中得到验证,LVDS在传送高数据率信号的同时还具有其它优势: 与低电源电压的兼容性;低功耗;低辐射;高抗干扰性;简单的布线和终端匹

2010-08-31 11:14:52 1591

1591

低压差分信号(LVDS)是一种低压、差分信号传输方案,主要用于高速数据传输。根据 ANSI/TIA/EIA-644 规范中的定义,它是一种最为常见的差分接口。这种标准只对适合于 LVDS 应用的驱动

2010-06-10 09:59:48 2015

2015

差分信号,什么是差分信号

一个差分信号是用一个数值来表示两个物理量之间的差异。从严格意义上来讲,所有电

2009-09-06 08:16:44 36718

36718

摘要:ANSI EIA/TIA-644标准定义的低电压差分信号(LVDS)非常适合包括时钟分配、点对点以及多点之间的信号传输。本文描述了使用LVDS将高速通讯信号分配到多个目的端的方法。

2009-05-01 11:14:27 1602

1602

lvds是什么意思?

摘要:与ECL、PECL和CML标准相比,ANSI EIA/TAI-644的低电压差分信号(LVDS)标准具有低功耗、低噪声辐射等优势。本文主要讨论LVDS的特性及

2009-05-01 11:13:29 9857

9857

摘要:ANSI EIA/TIA-644标准定义的低电压差分信号(LVDS)非常适合包括时钟分配、点对点以及多点之间的信号传输。本文描述了使用LVDS将高速通讯信号分配到多个目的端的方法。

2009-04-24 16:05:19 1198

1198

摘要:与ECL、PECL和CML标准相比,ANSI EIA/TAI-644的低电压差分信号(LVDS)标准具有低功耗、低噪声辐射等优势。本文主要讨论LVDS的特性及其可能的应用。 最近几年,随着微

2009-04-24 16:04:30 862

862

什么是(叫)差分信号

一个差分信号是用一个数值来表示两个物理量之间的差异。从严格意义上来讲,所有电压信号都是

2008-11-26 18:40:41 1477

1477 示波器的差分信号测量

初步介绍差分测量、放大器类型、应用及怎样避免常见错误

2008-11-26 18:36:53 17551

17551

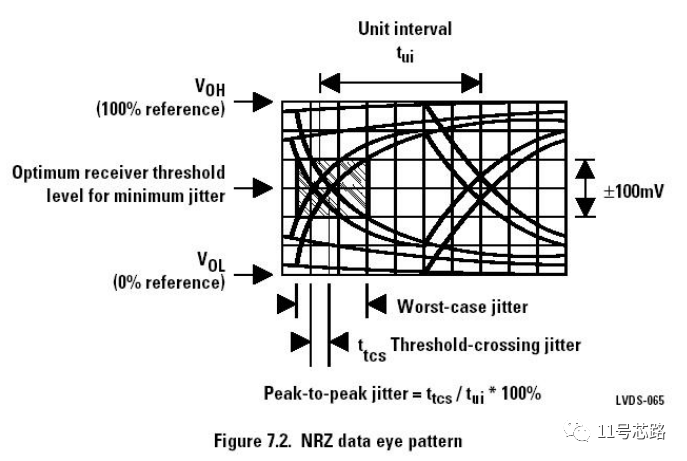

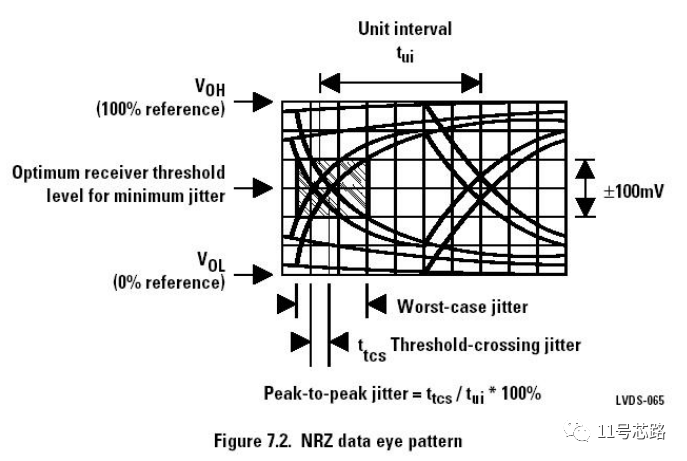

LVDS信号电平特性

LVDS物理接口使用1.2V偏置电压作为基准,提供大约400mV摆幅。LVDS驱动器由一个驱动差分线对的电流源组成(通常电

2008-10-16 13:50:25 16254

16254 什么是lvds信号

LVDS:Low Voltage Differential Signaling,低电压差分信号。LVDS传输支持速率一般在155Mbps(大约为77MHZ)以上。LVDS是一种低摆幅的差分信号

2008-10-16 13:49:11 7293

7293 1 LVDS信号介绍LVDS:Low Voltage Differential Signaling,低电压差分信号。LVDS传输支持速率一般在155Mbps(大约为77MHZ)以上。LVDS是一种低摆幅的差分信号技术,它使得信号能在差

2008-10-16 13:44:45 152

152

正在加载...

电子发烧友App

电子发烧友App

评论